Quantum chip port impedance test device and test method

A technology of impedance testing and chips, which is applied in the direction of measuring devices, measuring resistance/reactance/impedance, measuring electrical variables, etc., can solve the problems of low test accuracy, quantum chips are easy to be broken down, and manual test efficiency, so as to improve test efficiency, The effect of convenient and quick measurement and reducing the chip damage rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

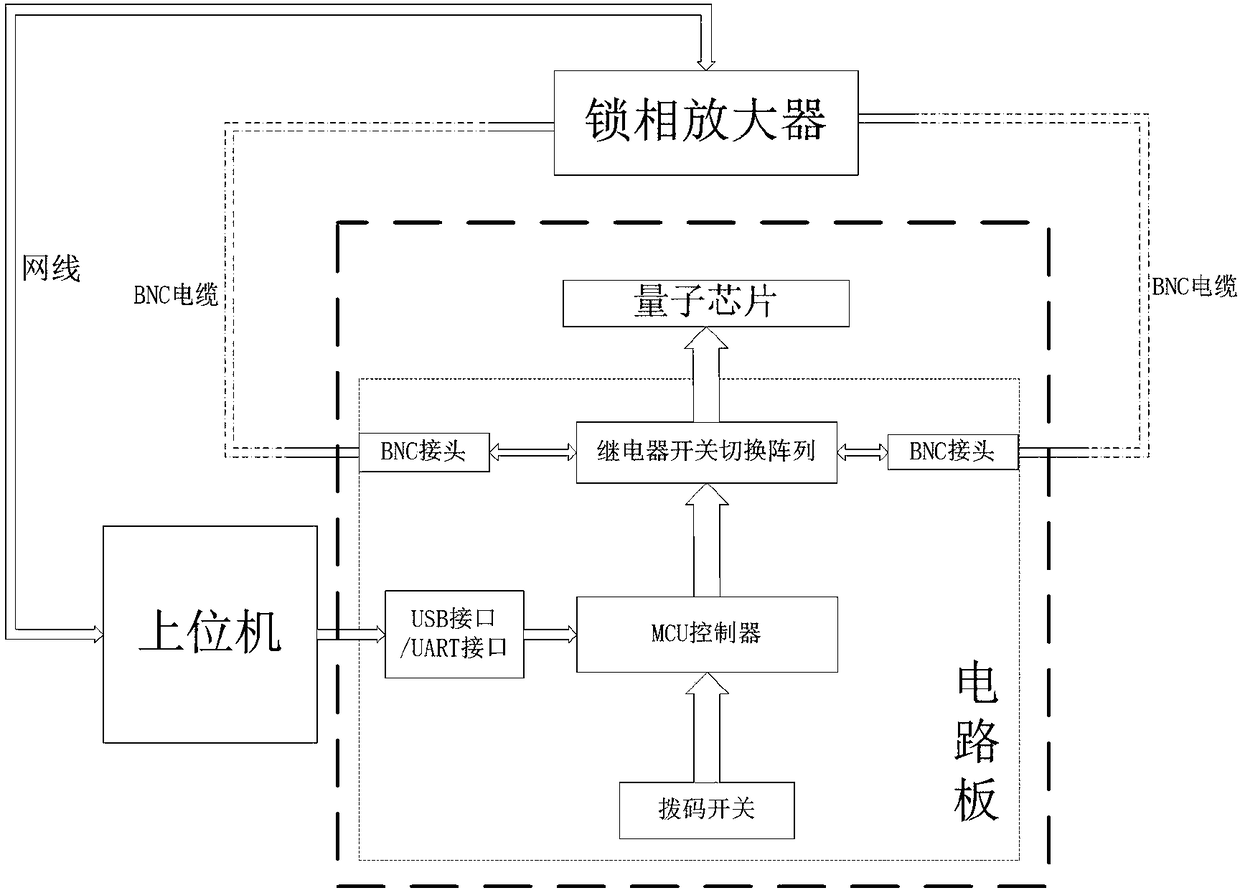

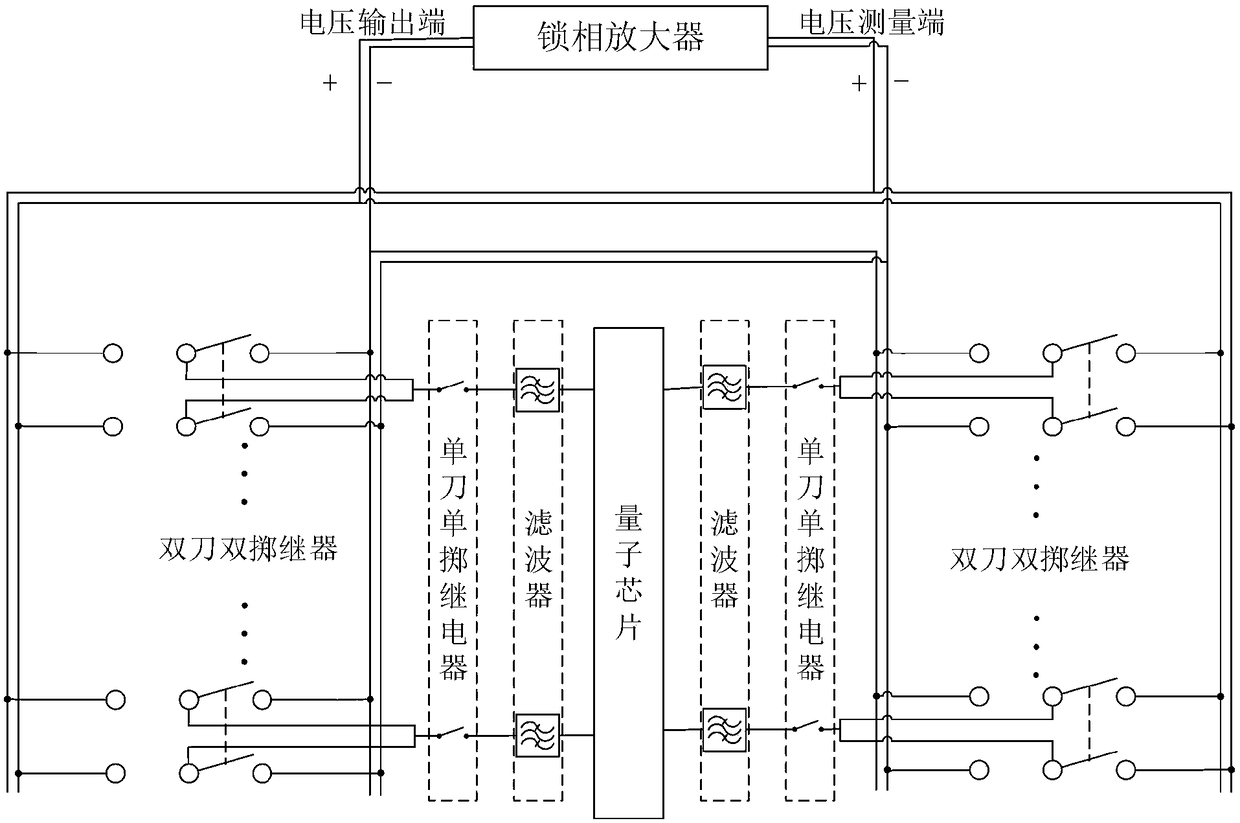

[0043] refer to figure 1 and figure 2 , A quantum chip port impedance test device, including a lock-in amplifier, a relay array switching circuit, a quantum chip, an MCU controller, and a host computer, the output end of the lock-in amplifier is connected to the input end of the relay array switching circuit, and the relay array switching circuit. The output end is connected to the input end of the lock-in amplifier, and the lock-in amplifier is used to provide small voltage output and small voltage measurement, which is used to meet the requirement of extremely low test voltage between the ports of the quantum chip and to improve the test accuracy. Each channel of the relay array switching circuit is connected to each port of the quantum chip, and the switching circuit of the relay array switching circuit is used to realize the switching of the voltage output terminal and the voltage detection terminal of the lock-in amplifier to the port channel of each quantum chip, instea...

Embodiment 2

[0049] refer to figure 2 The difference from Embodiment 1 is that each double-pole double-throw relay of the relay array switching circuit is connected to a single-channel filter, and the single-channel filter is connected to a single port of the quantum chip.

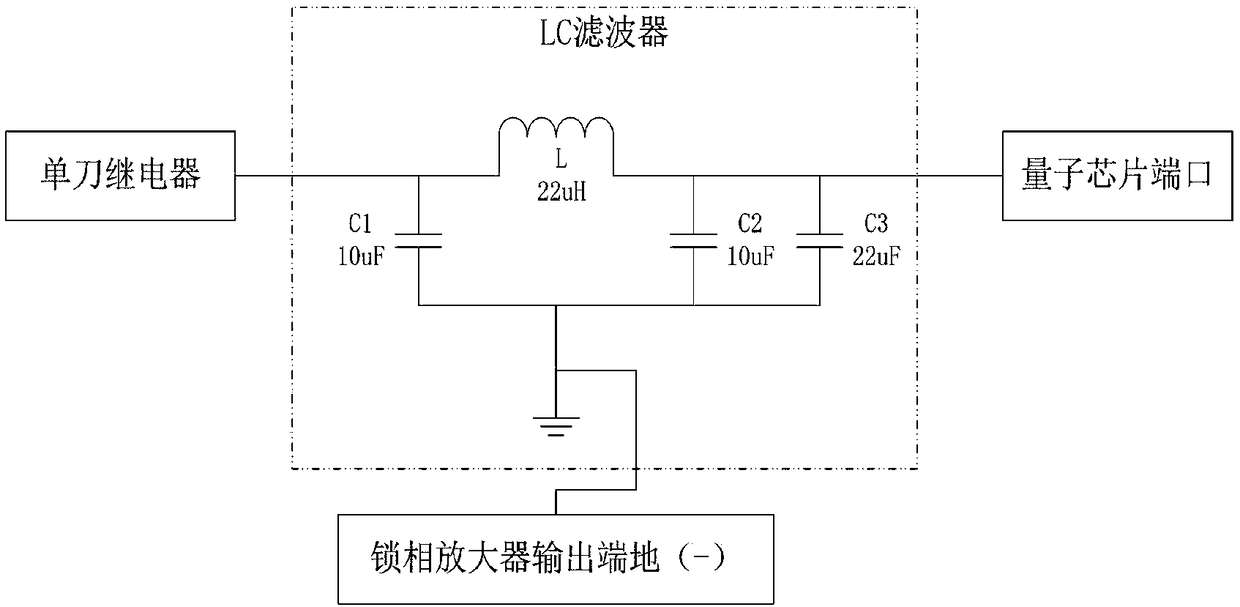

[0050] refer to image 3 , the filter structure and connection mode are shown in the figure, each channel of the relay array switching circuit is connected to a single channel filter, and the single channel filter is connected to a single port of the quantum chip. The form of the filter between the SPST relay and the quantum chip port is a 3-stage Butterworth low-pass LC filter, which is composed of a 10uF capacitor C1, a 22uH inductor L, a 10uF capacitor C2 and a 22uF capacitor C3. The ground terminal of the filter should be connected to the low potential (-) of the output terminal of the lock-in amplifier. The connection of the filter has a good effect on suppressing the electromagnetic interference of the relay an...

Embodiment 3

[0053] In this embodiment, the circuit structure is basically the same as the above-mentioned embodiment, the difference is that the relay array switching circuit also includes a single-pole relay, and the relay array is composed of a plurality of double-pole double-throw relays and single-pole single-throw relays. The ports correspond to a double-pole double-throw relay and a single-pole single-throw relay respectively, and the double-pole double-throw relay is connected to the quantum chip port through the single-pole relay. In this way, high-level, low-level and floating high-impedance states can be provided for each quantum chip port, and the impedance between several ports can be tested more conveniently and flexibly.

[0054] figure 2 The connection method between the lock-in amplifier and the relay array, the connection method between the relay array and the filter, the connection method between the filter and the quantum chip, and the composition method of the entire ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More