Interruption control flow diagram-based interruption verification method

A technology of control flow graph and verification method, applied in the direction of instrument, error detection/correction, calculation, etc., can solve problems such as affecting security, randomness and complexity of interrupt handler, and achieve the effect of improving reliability and security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

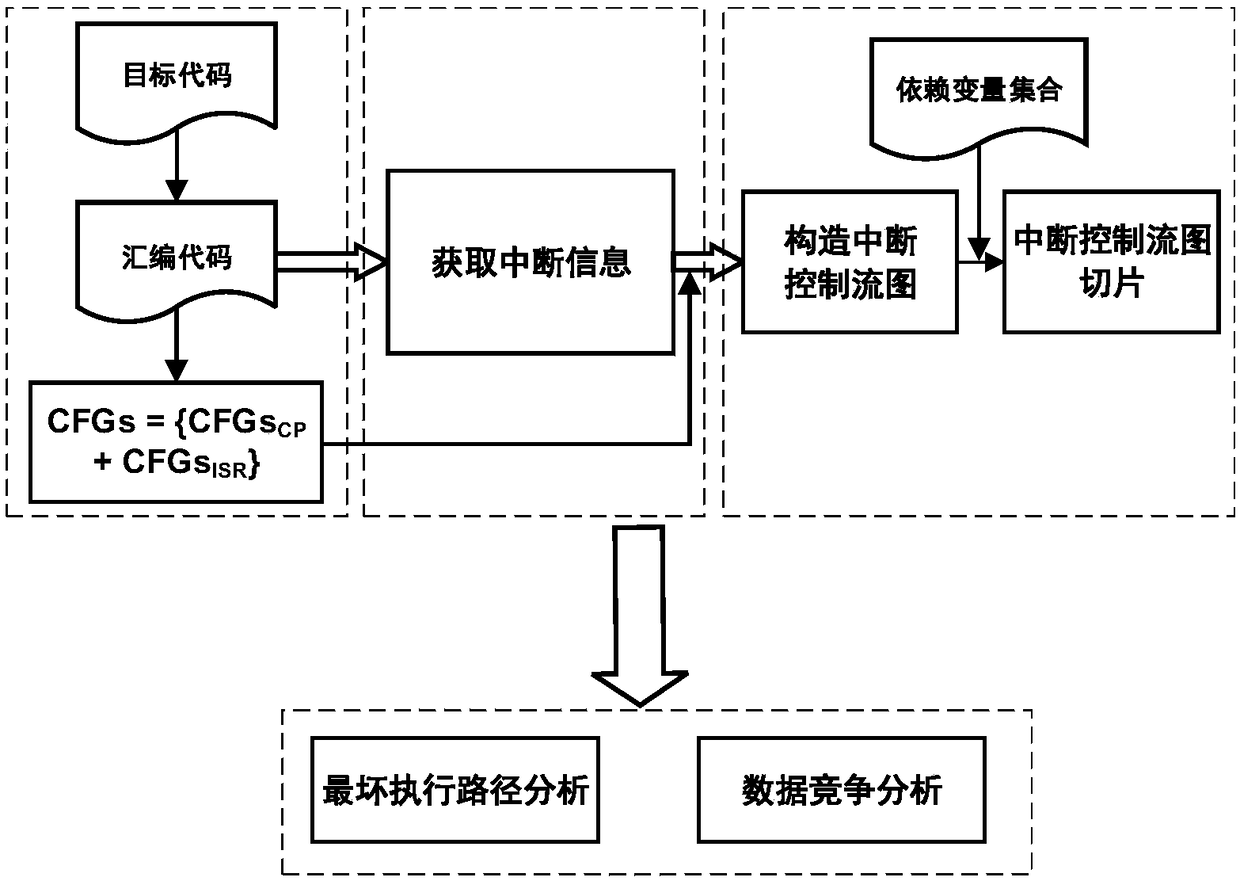

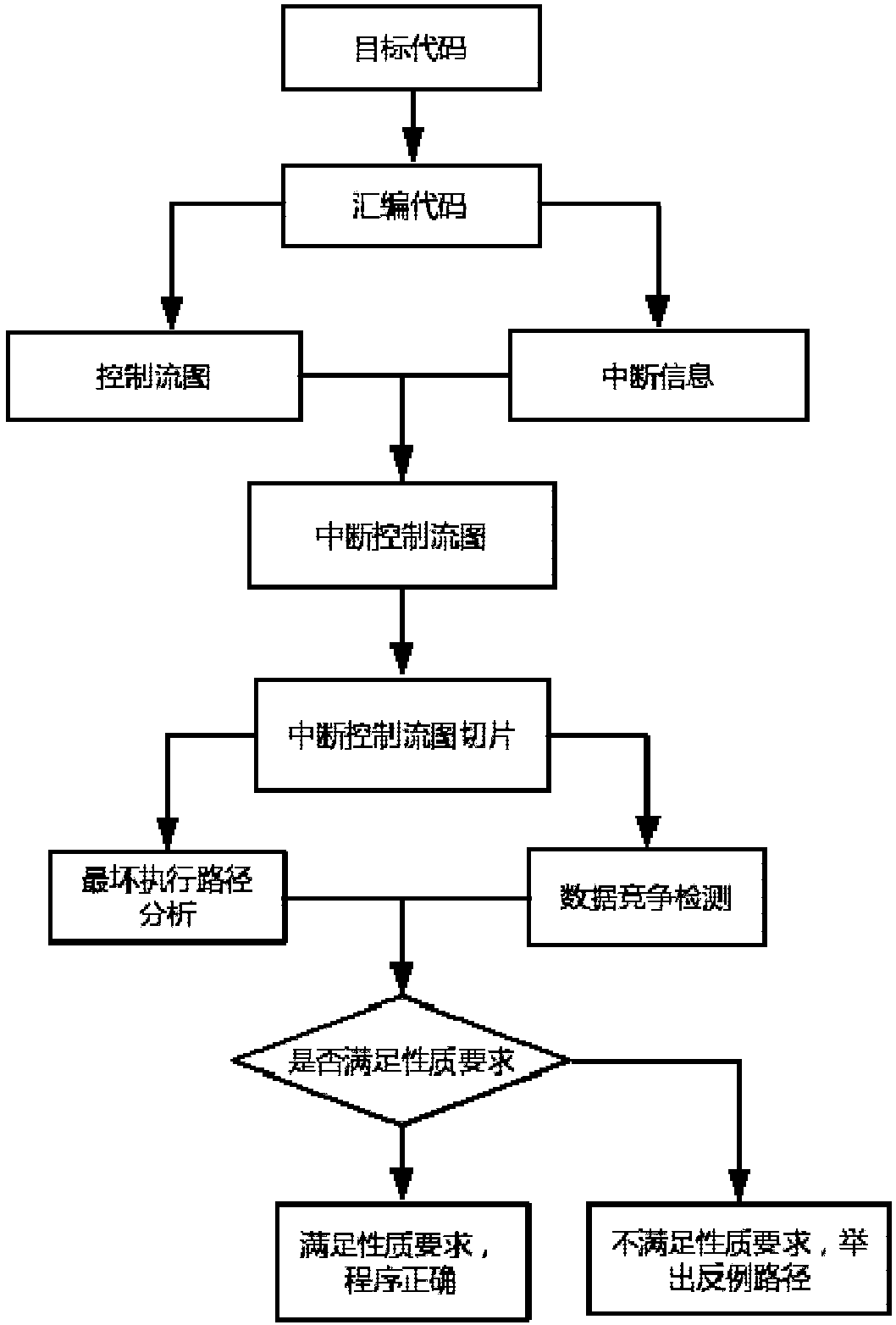

Method used

Image

Examples

Embodiment

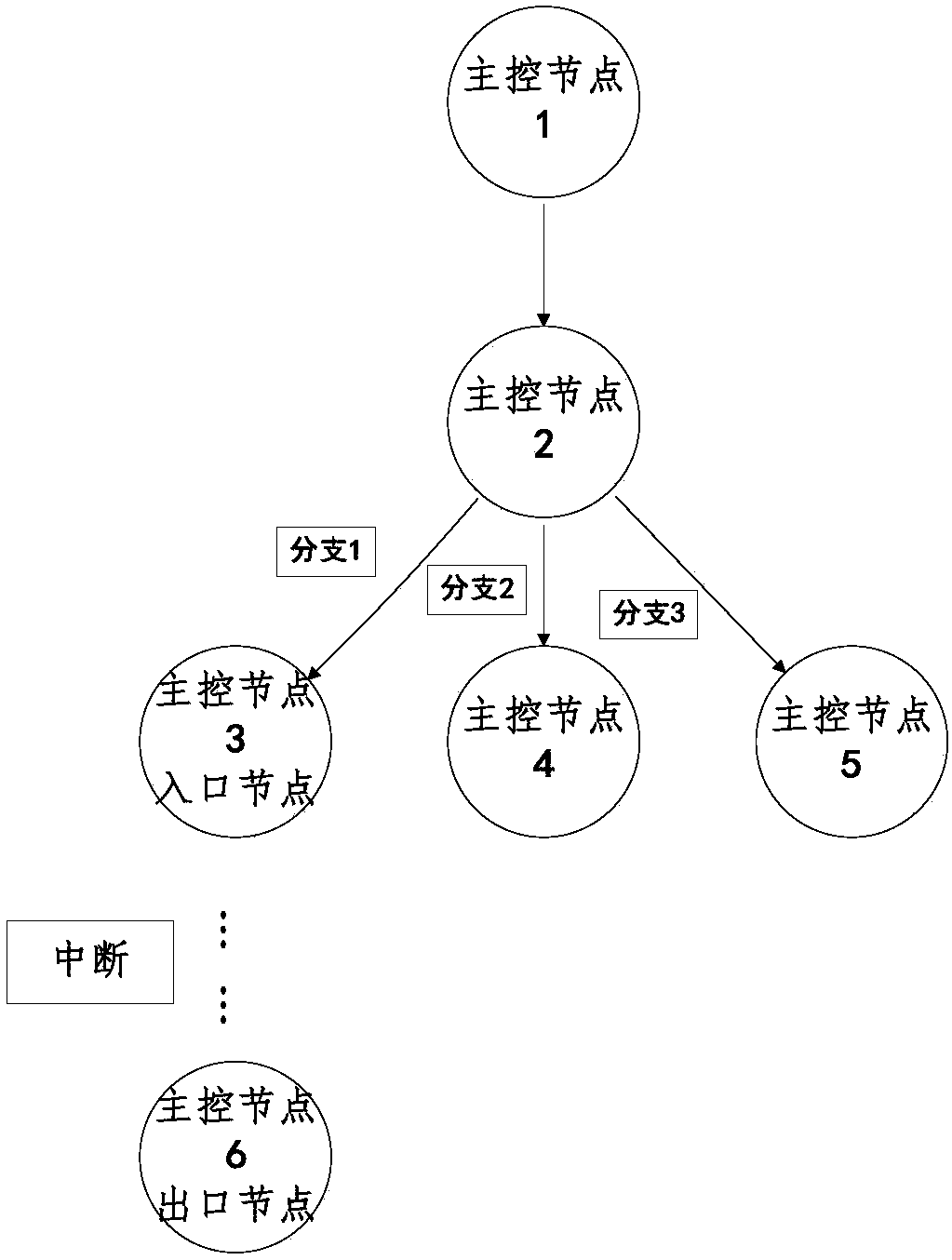

[0076] Such as image 3 , Figure 4 as shown, image 3 shows a structure of the main control flow graph, including the main control node, branch 1, branch 2, branch 3 and the directed edges between each node, Figure 4 shows a structure of interrupt processing control flow graph, including interrupt node, branch 1, branch 2, branch 3 and the directed edges between each node, set Figure 4 The interrupt handling control flow graph shown in image 3 The interrupt handler for the interruption of the master control flow graph, and each node is executed only once, then the worst path analysis process is:

[0077] 1) Merge the marked nodes in the same branch in the main control program into one node;

[0078] 2) Merge all marked nodes in the same branch in the same interrupt handler in the branch corresponding to the main control program of the appeal into one node.

[0079] Among them, ci represents the instruction cycle in the basic block i, and ni represents the number of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More