Desktop supercomputing hardware platform based on DSP and FPGA multi-co-processing card

A hardware platform and co-processing card technology, applied in the direction of electrical digital data processing, digital computer components, and various digital computer combinations, etc., can solve the problems of poor openness, limited scalability, poor scalability, etc. Power consumption and heat dissipation pressure, strong computing power, area saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Embodiments of the present invention are described in detail below, and the embodiments are exemplary and intended to explain the present invention, but should not be construed as limiting the present invention.

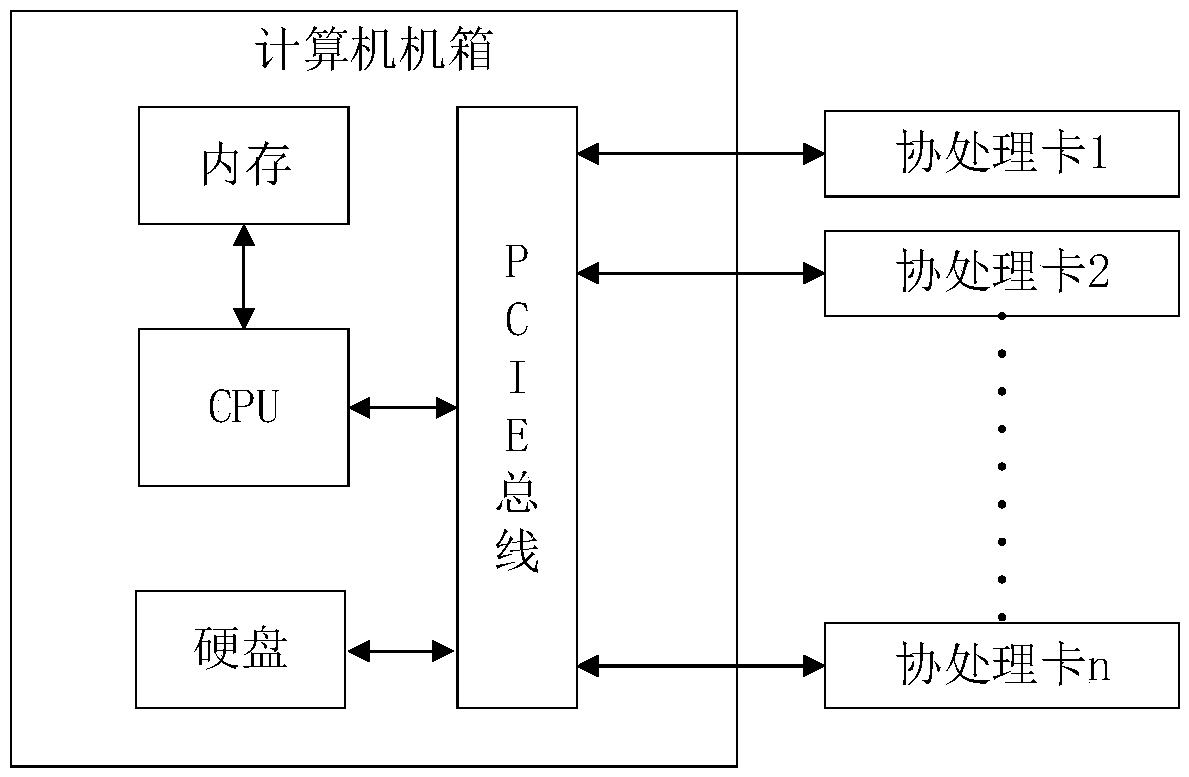

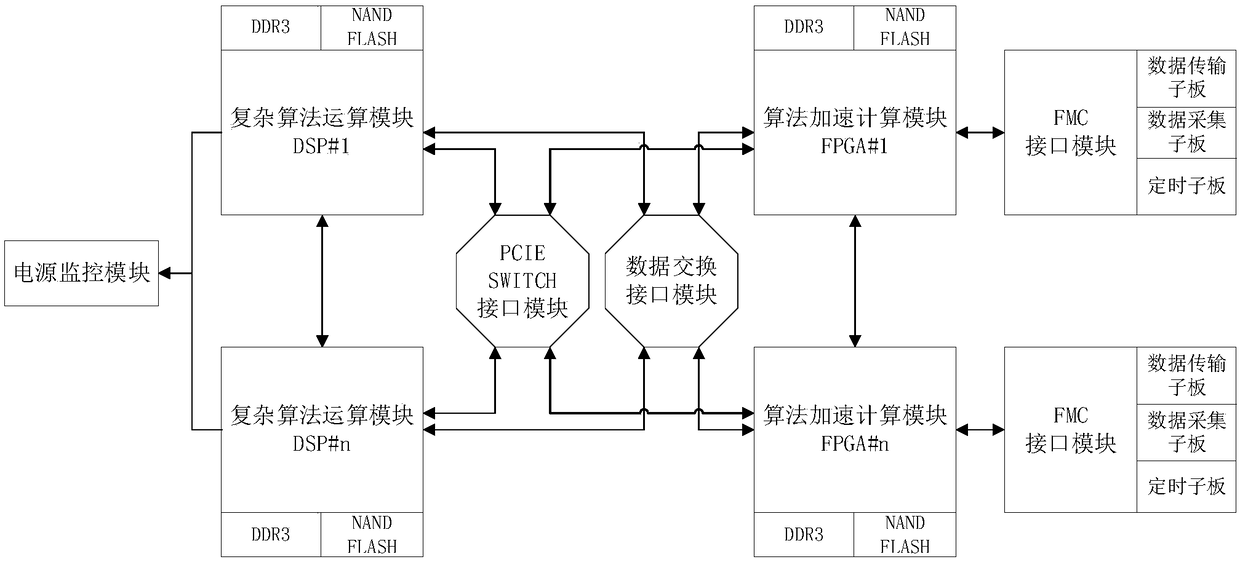

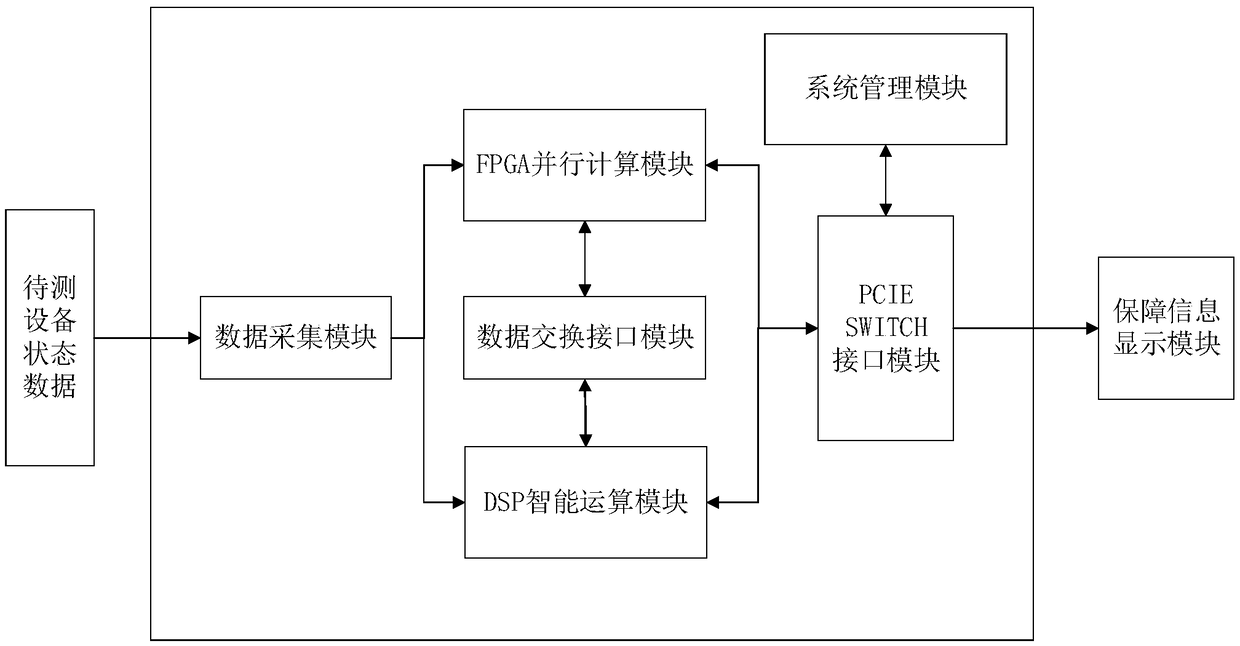

[0035] Such as figure 1 As shown, a desktop supercomputing hardware platform based on DSP and FPGA multi-coprocessing cards is composed of a computer chassis equipped with multiple co-processing cards. The co-processing card contains multiple DSP processors and multiple FPGA chips. PCIE bus slot for expansion to build a desktop supercomputer hardware platform with high availability, low power consumption, and small size.

[0036] The computer case adopts a commercial personal computer structure, including a general-purpose CPU processor, a hard disk, a memory and a PCIE bus slot.

[0037]The general-purpose CPU processor runs Windows or Linux operating systems; the general-purpose CPU processor is used for system configuration management, task scheduling, dat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More