Packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., to achieve the effects of reducing manufacturing costs, reducing thickness, and ensuring simplicity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

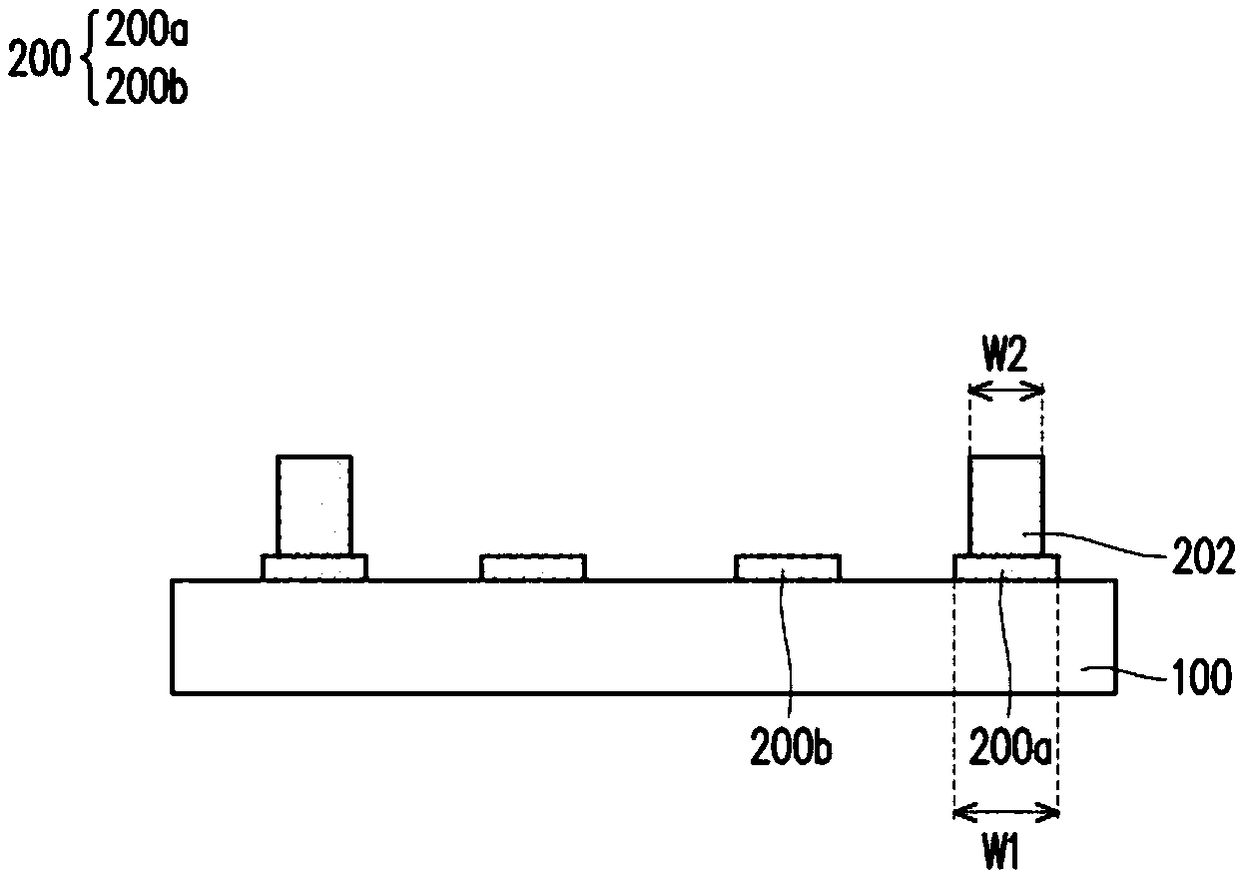

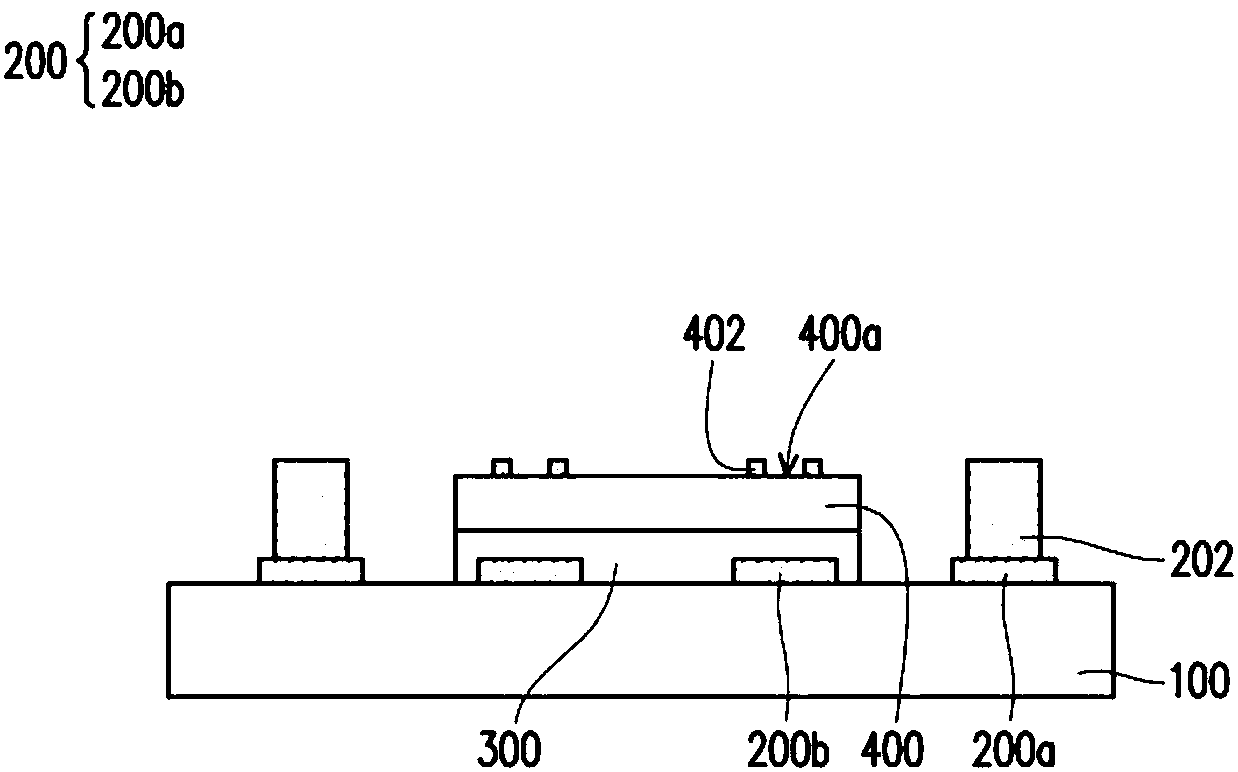

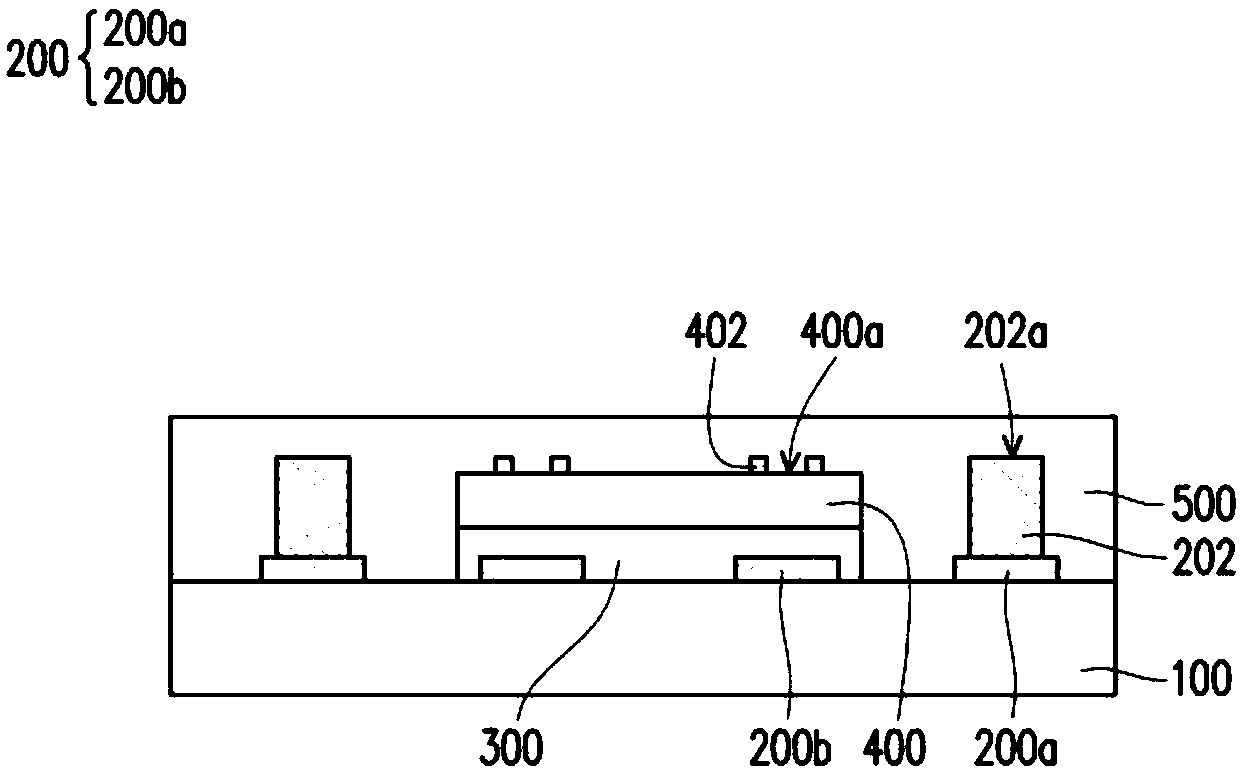

[0038] Figure 1A to Figure 1J It is a schematic cross-sectional view of the manufacturing process of the packaging structure 10 according to an embodiment of the present invention.

[0039] refer to Figure 1A , providing a carrier substrate 100 . The carrier substrate 100 includes a metal carrier substrate, a glass carrier substrate or a silicon wafer substrate. For example, in this embodiment, a metal carrier substrate can be used as the carrier substrate 100 . Other materials of the carrier substrate utilized in other embodiments may also be used in this embodiment. A first circuit layer 200 is formed on the carrier substrate 100 . In some embodiments, the formation of the first circuit layer 200 on the carrier substrate 100 may be performed by, for example, an electroless plating process, a chemical plating process, a thermal evaporation process or sputtering. Process (sputtering process). For example, a metal layer (not shown) can be formed on the carrier substrate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More