A BCD semiconductor device and a method for manufacture the same

A semiconductor and device technology, applied in the field of BCD devices and their manufacturing, which can solve the problems of limited application and rising on-resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

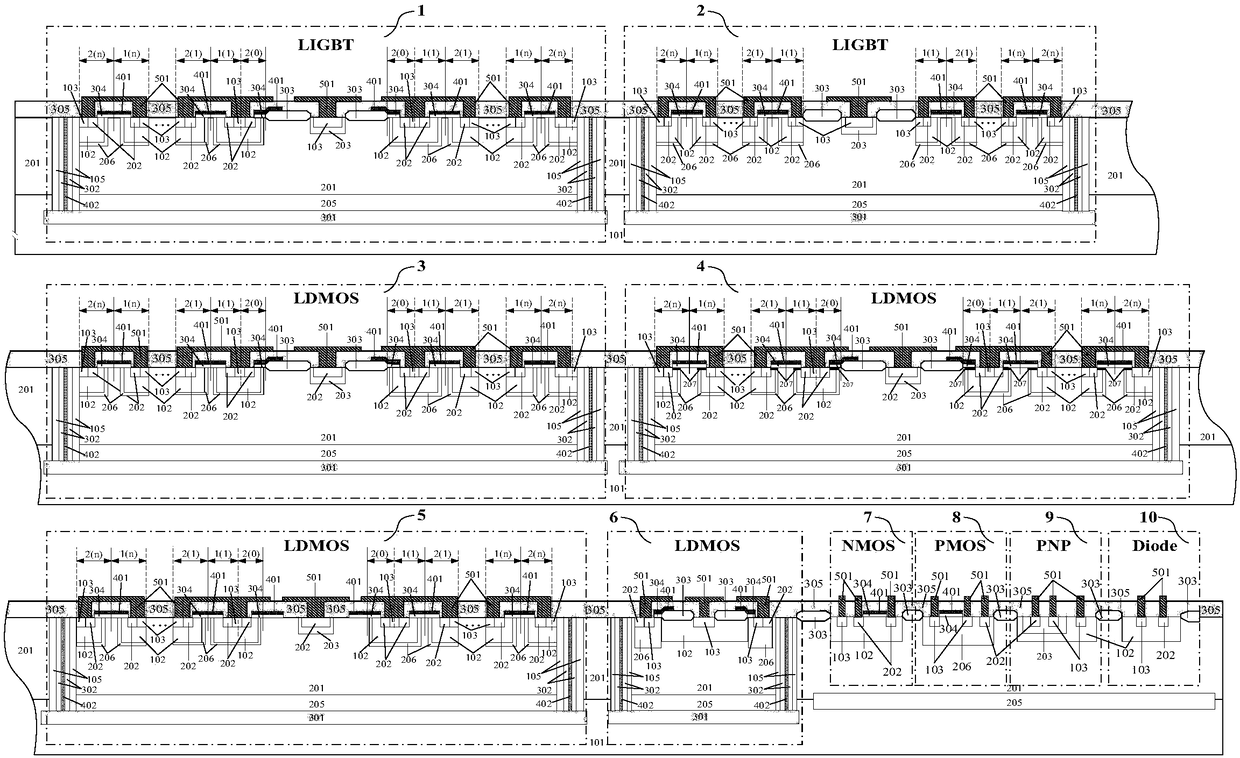

[0081] like figure 1 As shown, a BCD semiconductor device includes a first high-voltage nLIGBT device 1, a second high-voltage nLIGBT device 2, a first high-voltage nLDMOS device 3, a second high-voltage nLDMOS device 4, and a third high-voltage nLDMOS device 5 integrated on the same chip , the first high voltage pLDMOS device 6, the low voltage NMOS device 7, the low voltage PMOS device 8, the PNP device 9 and the diode device 10, the first high voltage nLIGBT device 1, the second high voltage nLIGBT device 2 and the first high voltage nLDMOS device 3, the first high voltage nLIGBT device 3, the first The second high-voltage nLDMOS device 4, the third high-voltage nLDMOS device 5, and the first high-voltage pLDMOS device 6 all adopt dielectric isolation to realize complete isolation of high-voltage and low-voltage devices. The first high-voltage nLIGBT device 1, the second high-voltage nLIGBT device 2, and the first high-voltage nLDMOS device 3. The second high-voltage nLDMOS...

Embodiment 2

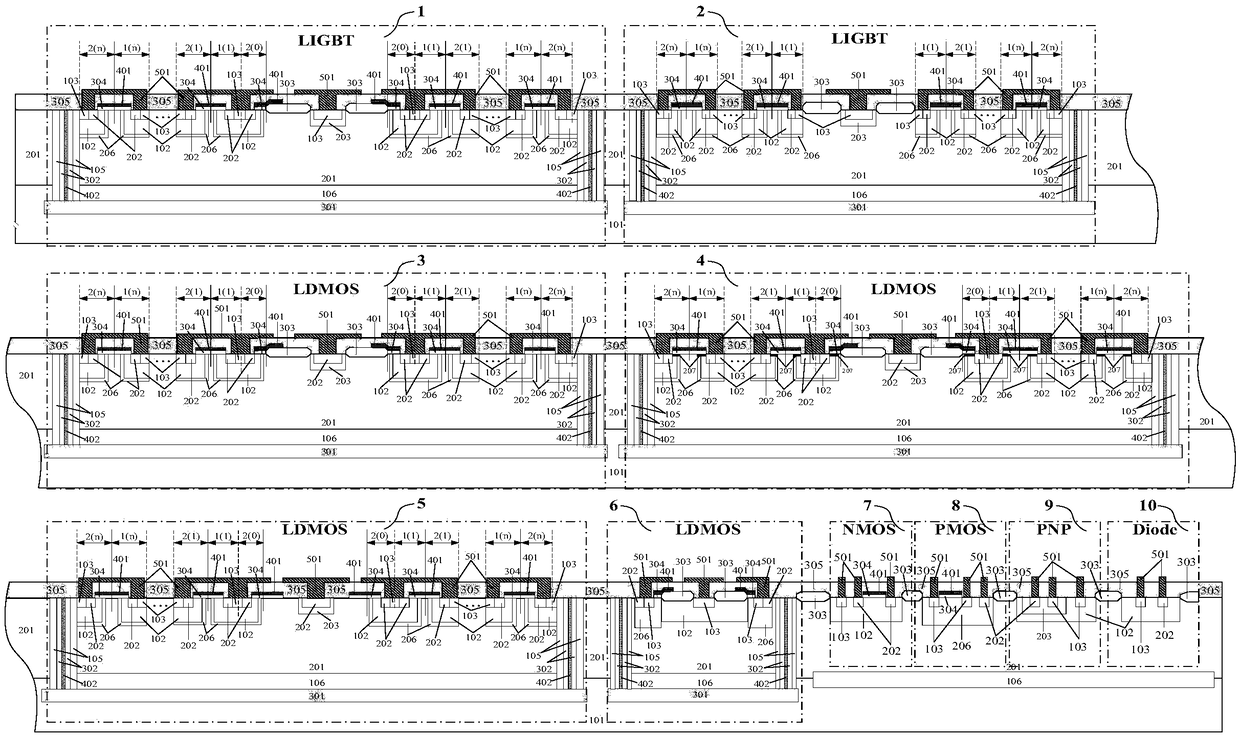

[0112] like figure 2 As shown, the difference between the BCD semiconductor device of this embodiment and Embodiment 1 lies in: the first high-voltage nLIGBT device 1, the second high-voltage nLIGBT device 2, the first high-voltage nLDMOS device 3, the second high-voltage nLDMOS device 4, and the first high-voltage nLDMOS device 4. Three high-voltage nLDMOS devices 5, the first high-voltage pLDMOS device 6, the buried layer 205 of the second conductivity type above the dielectric 301 is replaced with the first conductivity type withstand voltage structure 106, the first conductivity type withstand voltage structure 106 and the side wall of the dielectric groove 302 The implanted regions 105 of the first conductivity type are connected to each other.

Embodiment 3

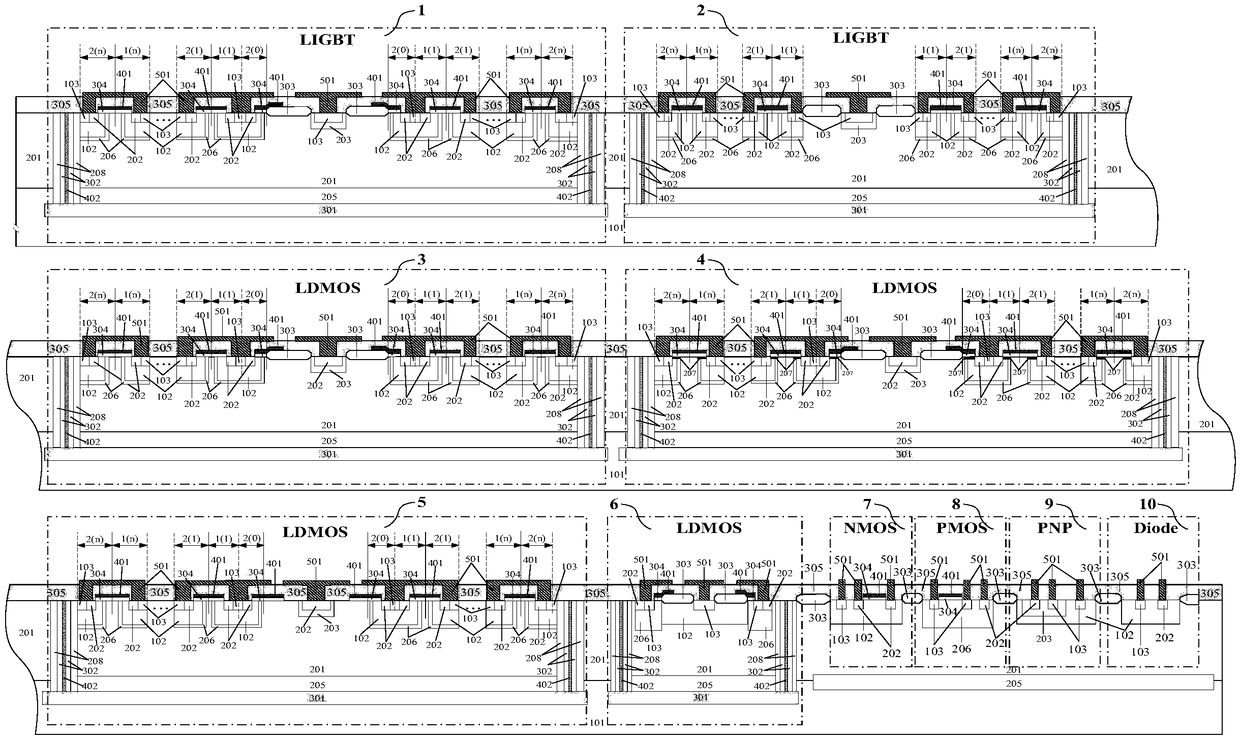

[0114] like image 3 As shown, the difference between the BCD semiconductor device of this embodiment and Embodiment 1 lies in: the first high-voltage nLIGBT device 1, the second high-voltage nLIGBT device 2, the first high-voltage nLDMOS device 3, the second high-voltage nLDMOS device 4, and the first high-voltage nLDMOS device 4. For the three high-voltage nLDMOS devices 5 and the first high-voltage pLDMOS device 6 , the left and right side walls of the dielectric trench 302 have the implanted regions 105 of the first conductivity type replaced with dielectric field-enhancing structures 208 of the second conductivity type.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More