A high speed memory chip having multiple independent access channels

A memory chip and independent access technology, which is applied in the direction of instruments, electrical digital data processing, etc., can solve the problems of high storage price, difficult interface implementation, high cost ratio, etc., to achieve data sharing and data exchange, total storage Cost reduction, storage and processing effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

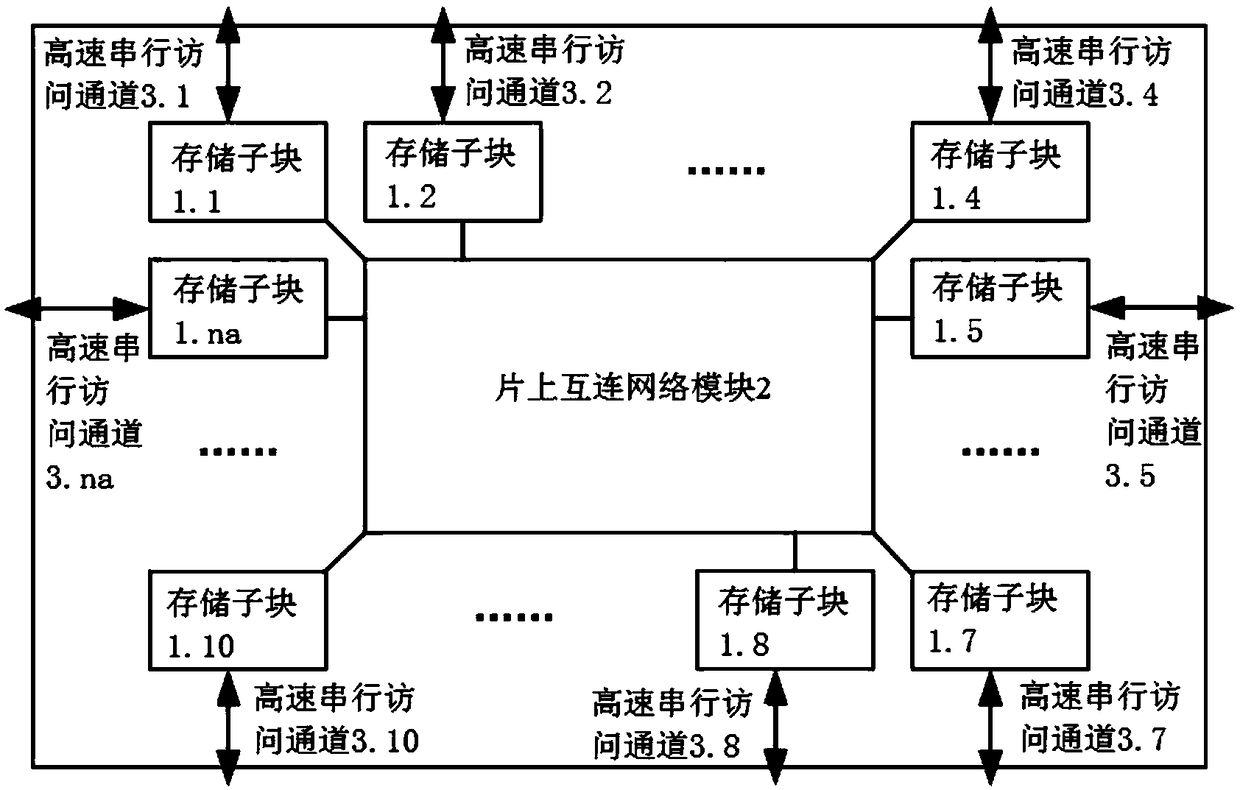

[0035] Such as figure 1 As shown, a high-speed memory chip with multiple independent access channels includes on-chip memory and several high-speed serial access channels. The high-speed serial access channels are respectively marked as 3.1, 3.2, 3.3, ..., 3.na, na is a natural number, and also includes an on-chip interconnection network module 2. The on-chip memory includes several storage sub-blocks that can be accessed in parallel. The storage sub-blocks are respectively marked as 1.1, 1.2, 1.3, ..., 3. The number of row access channels is equal, the high-speed serial access channels are closely coupled with the storage sub-blocks one by one, each high-speed serial access channel is connected with one storage sub-block, and na storage sub-blocks are interconnected through the on-chip interconnection network module 2, Here, the high-speed serial access channel is composed of a single Serdes Lane. From the perspective of the memory chip, the channel receives and sends two dir...

Embodiment 2

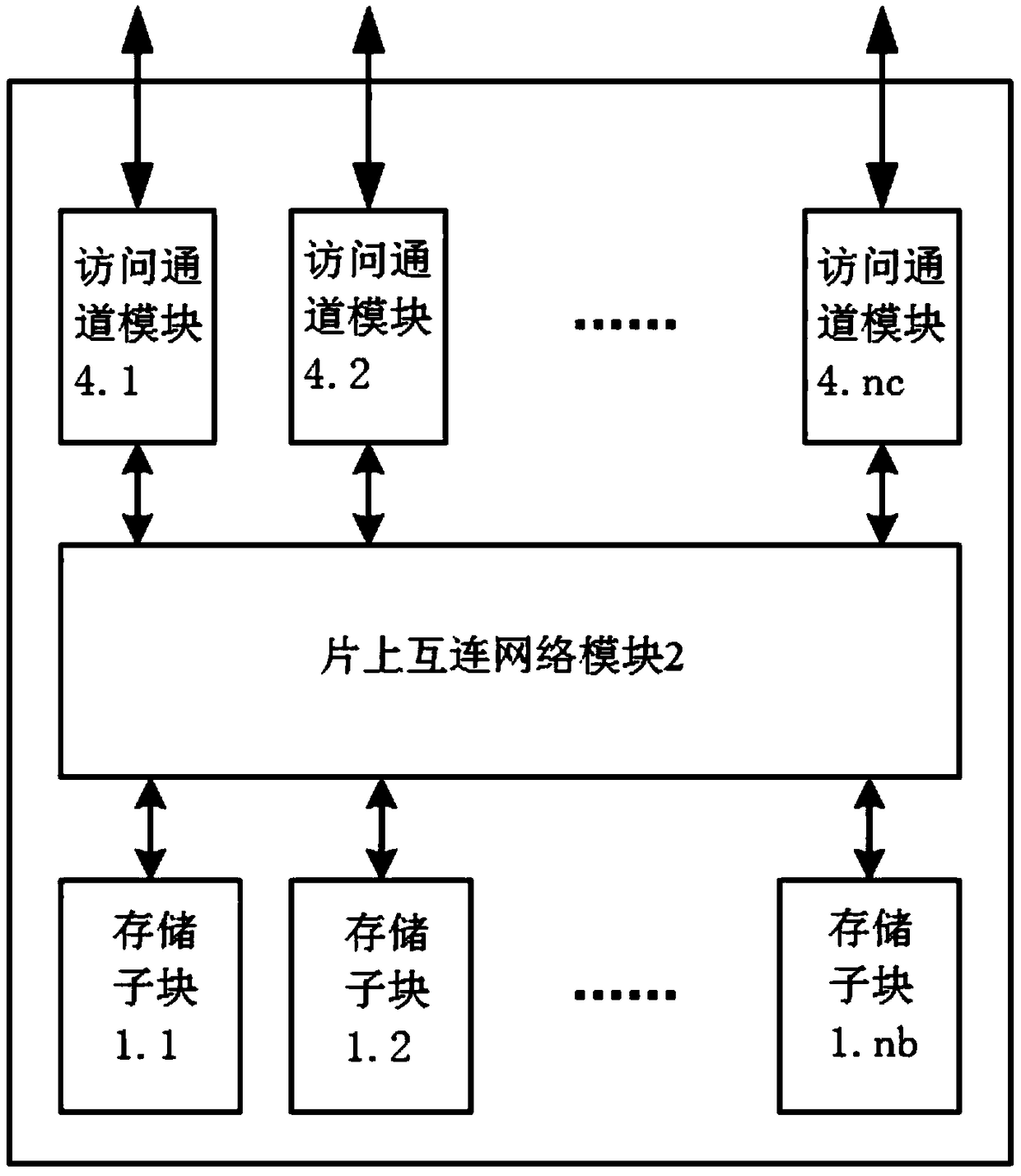

[0039] Such as image 3 As shown, a high-speed memory chip with multiple independent access channels includes an on-chip memory and several high-speed serial access channels, and also includes an on-chip interconnection network module 2. The on-chip memory includes several memory sub-blocks that can be accessed in parallel. The storage sub-blocks are respectively marked as 1.1, 1.2, 1.3, ..., 1.nb, the high-speed serial access channel is loosely coupled with the storage sub-block, the high-speed serial access channel is connected with the on-chip interconnection network module 2 through the access channel module, and access The channel modules are marked as 4.1, 4.2, 4.3, .

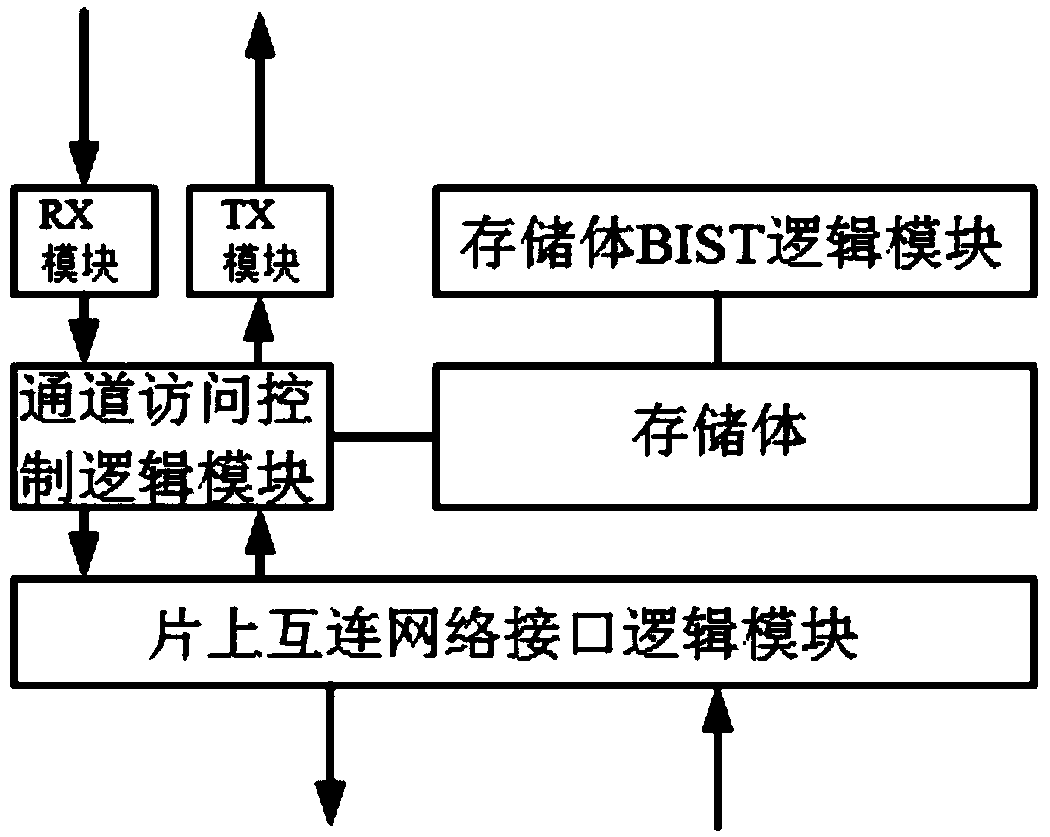

[0040] Such as Figure 4 As shown, the access channel module includes a channel access control logic module. The channel access control logic module communicates with the high-speed serial access channel through the RX module and the TX module respectively. The channel access control logic module is conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More