Method for optimizing chip friability based on response surface modeling

A fragility and response surface technology, applied in simulators, instruments, control/regulation systems, etc., can solve problems such as safety issues, affecting processing efficiency, and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

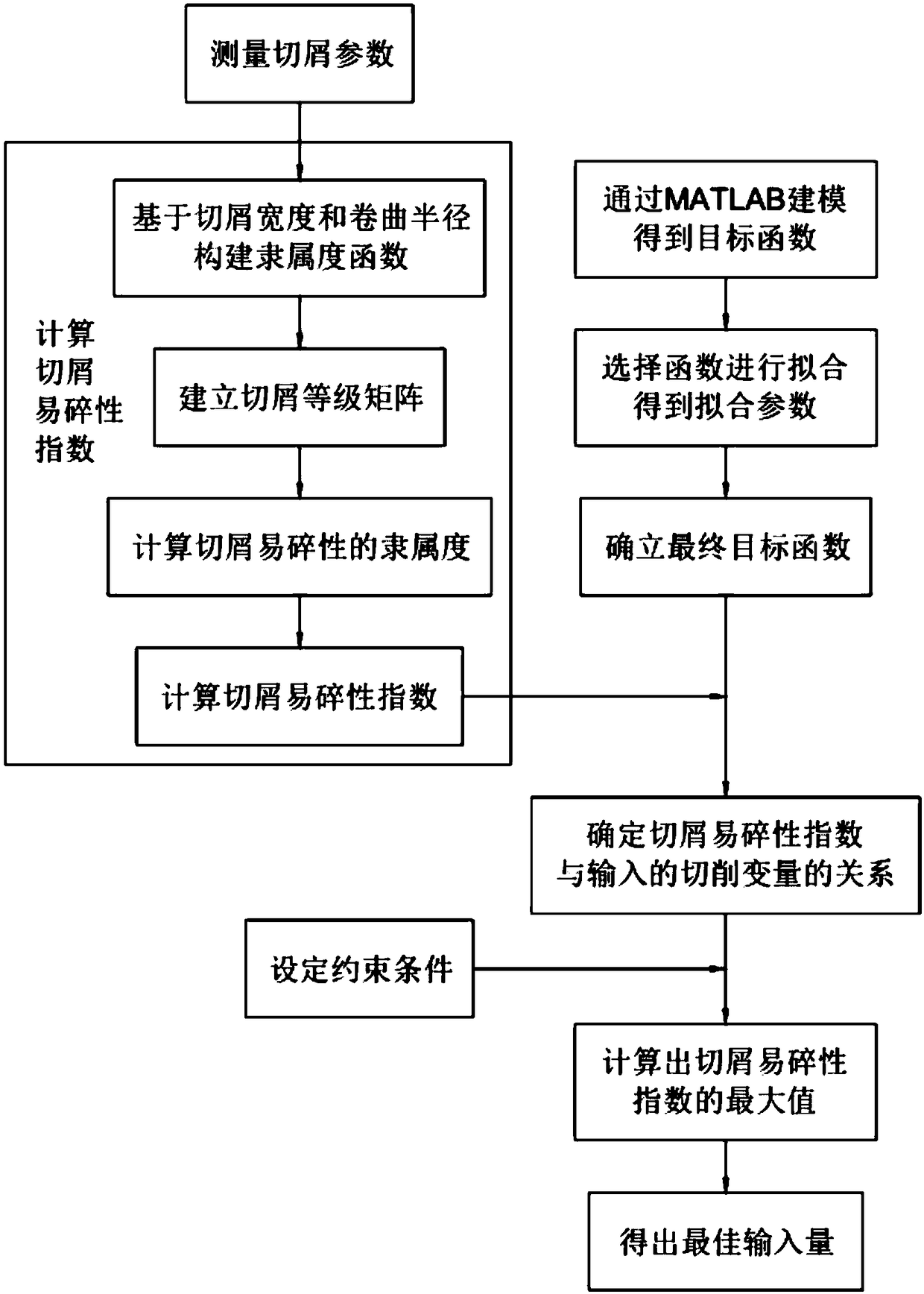

[0068] Such as figure 1 As shown, a method for optimizing chip friability based on response surface modeling includes the following steps:

[0069] a. Evaluate the chip friability and calculate the chip friability index C in ;

[0070] b. Modeling by response surface method RSM and optimizing chip friability.

[0071] In this embodiment, first of all, the fuzzy logic theory in fuzzy mathematics is applied to the establishment of a model for evaluating chip friability, and finally a model for evaluating chip friability is successfully established, and by defining chip friability Index C in Quantitatively expresses the fragility of chips, and provides output data for multivariate quadratic fitting using the response surface method. Then, using the method of implementing multivariate quadratic fitting in MATLAB, the function with the highest accuracy is selected through multiple simulations , finally obtained the multivariate quadratic objective function, and successfully est...

Embodiment 2

[0073] On the basis of embodiment 1, this embodiment includes the following steps before performing step a:

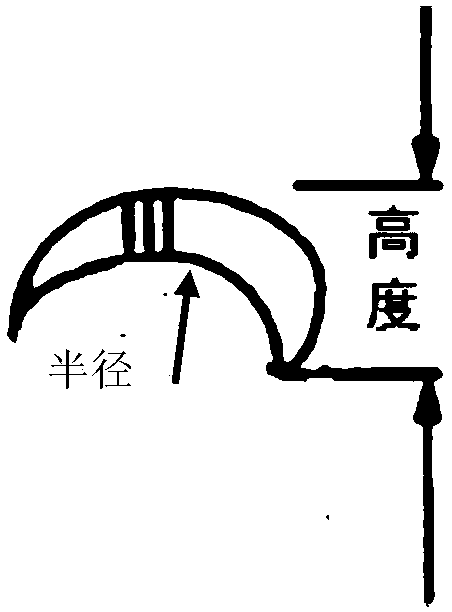

[0074] Measure chip parameters including chip width and chip curl radius. The chip width refers to the width value on a chip, not the length value. Since the range of the length value often exceeds the range that the instrument can measure, the measurement of the width value makes the evaluation of the calculated data more accurate; the chip curl radius is an item The index used to indicate the degree of curling of chips. Since the degree of curling is expressed by the radian of the curling part, it will make it difficult to define the specific curling part. Therefore, measuring the radius of the curling part to illustrate the degree of curling of chips can make the measurement data more accurate and facilitate the calculation of chips. Fragility Index.

Embodiment 3

[0076] In this embodiment, on the basis of embodiment 2, said step a includes the following steps:

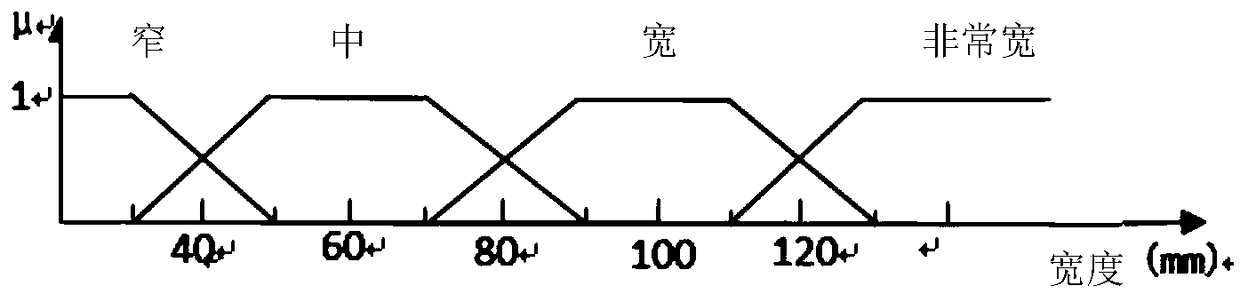

[0077] a101. Construct width membership function and curl radius membership function respectively based on chip width and curl radius:

[0078] Chip=S N (df 1 , df 2 )

[0079] where N represents the chip group whose dimensions are width and curl radius, df 1 and df 2 The size characteristics of chips can be blurred;

[0080] DF 1 =[μF 1i (df 1 ) / F1i (df 1 )]

[0081] DF 2 =[μF 2j (df 2 ) / F 2j (df 2 )]

[0082] Among them, F represents the grade level of the chip shape, DF 1 is the first dimension feature, DF 2 is the second dimension feature, μ is df 1 or df 2 membership degree value;

[0083] a102, establish chip shape matrix M:

[0084]

[0085] m N ={(A k ) ij}, i=1...m, j=1...n

[0086] Among them, i is the grade level of the chip shape of the first dimension feature, j is the grade level of the chip shape of the second dimension feature, A k ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More