Watertight circuit board fabrication method

A manufacturing method and circuit board technology, applied in the electronic field, can solve the problems of large occupied area of chips and devices, signal delay, large power consumption, etc., and achieve the effect of increasing connection density, avoiding position movement, and avoiding displacement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0080] Such as Figures 1 to 8 Shown is a step diagram of the method for making the watertight circuit board in this embodiment.

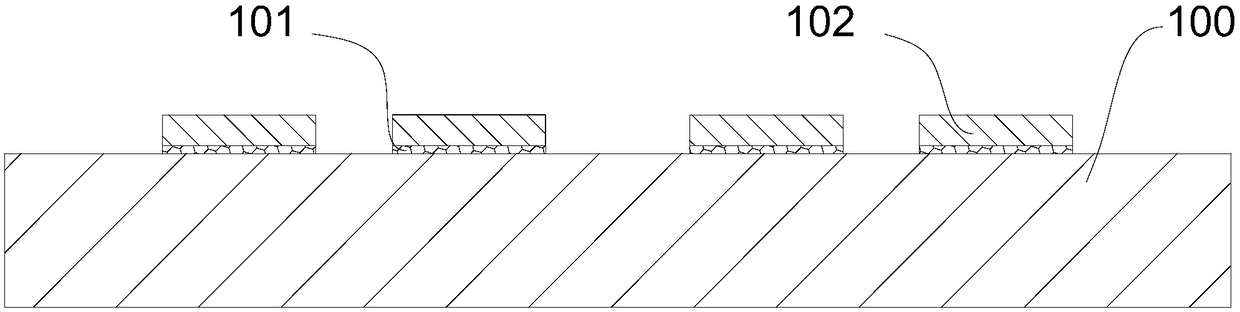

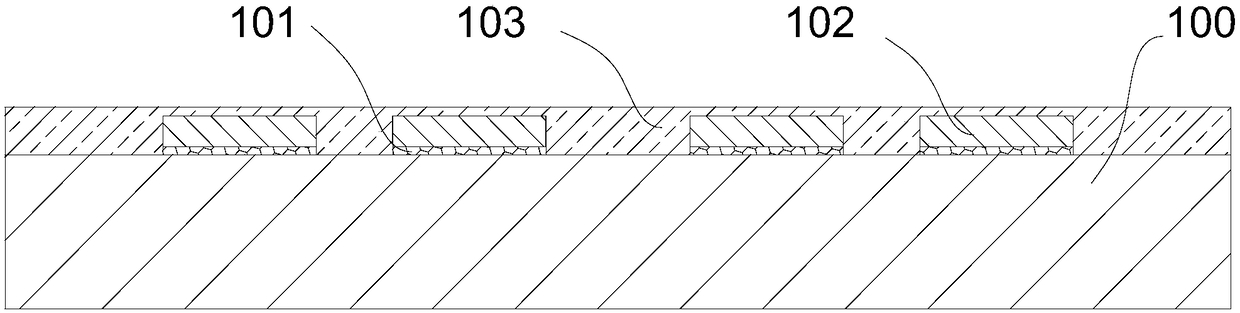

[0081] This is the example, such as figure 1 As shown, the sealing base layer 100 is a whole made of glass plate, and the sealing base layer 100 is made by processing a glass plate whose thickness, size, and physical / chemical / mechanical properties meet the requirements. Such as figure 2 As shown, the electronic component 102 with component pins is pasted on the sealing base layer 100 with a patch material 101 (which can be liquid, solid or film), and the position of the electronic component 102 on the sealing base layer is fixed to avoid electronic components in the subsequent process. Part 102 is displaced, affecting the connection. In this embodiment, the electronic component 102 is a chip with chip pins, and the chip pins are component pins (but not limited thereto, and may also be bare chips, electronic components, electronic devices, or ot...

Embodiment 2

[0091] The difference between embodiment two and embodiment one is:

[0092] Such as Figure 9 , 10 As shown, the sealing substrate has its own patch groove 110, or the patch groove 110 is made on the upper surface of the sealing base layer 100 by photolithography, wet etching, dry etching or other processes, such as Figure 11 As shown, the electronic component 102 is pasted in the patch groove 110 through the patch material 101 . The position of the electronic component 102 is limited by the patch groove 110 to avoid displacement of the electronic component 102 in subsequent processes.

[0093] Wherein, the sealing base layer 100 is a whole, and the whole itself has patch grooves 110 ; or, the sealing base layer 100 is a multi-layer structure, and the uppermost layer has patch grooves 110 .

[0094] Such as Figure 12 As shown, the sealing base layer 100 is covered with a first insulating layer 103 , and the first insulating layer 103 and the sealing base layer 100 encap...

Embodiment 3

[0102] The difference between embodiment three and embodiment one is:

[0103] Such as Figure 19 , 20 As shown, the first insulating layer 103 is a two-layer laminated structure, including a first insulating layer 103A and a second insulating layer 103 . Such as Figure 20 As shown, the first via hole 104 passes through the first first insulating layer 103A and the second first insulating layer 103B.

[0104] The material, thickness, and area covered on the watertight substrate can be selected according to needs, and the first first insulating layer 103A and the second first insulating layer 103 can use the same or different materials. In this embodiment, the first insulating layer 103 has a stacked structure of two layers, but it is not limited thereto, and a stacked structure of more than three layers may also be used. Similarly, the second insulating layer 106 may also adopt a multi-layer structure similar to that of the first insulating layer 103 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More