Chip of reverse blocking IGBT and manufacturing method

A chip and reverse resistance technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve the problems of wide diffusion area of P+ isolation area, waste of chip terminal area, long diffusion time, etc., and reduce the chip terminal area area, improve utilization rate, and reduce the effect of using area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

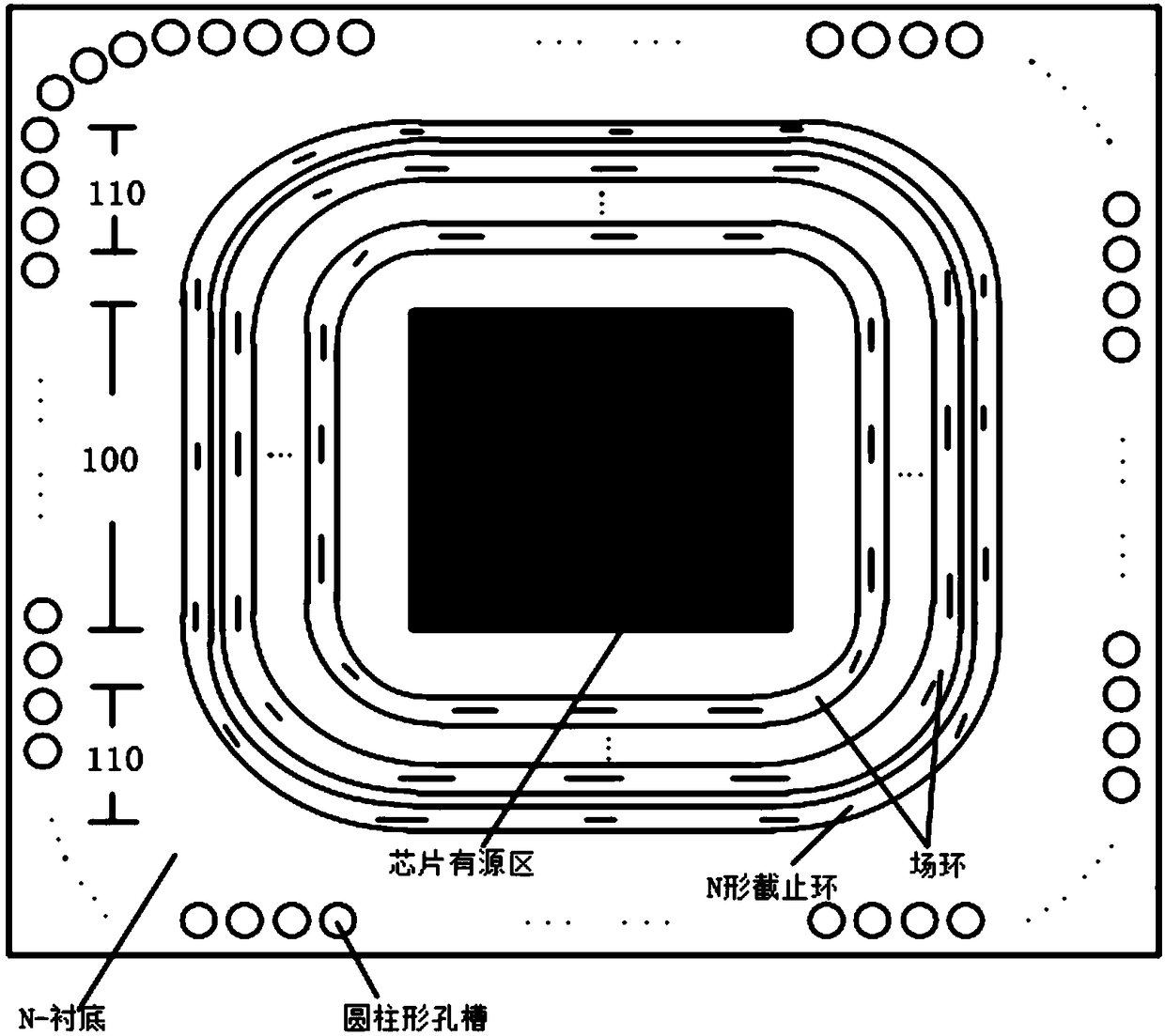

[0023] In this embodiment, a single-row cylindrical hole array is used, such as figure 1 As shown, the N-substrate doping concentration is 1e13cm -3 —5e13cm -3 , Thickness 400μm-550μm (depending on the size of the withstand voltage). The width of the active area of the chip (100) is 200μm-400μm, the width of the terminal area (110) is 200μm-1000μm (depending on the withstand voltage), and the distance between the cylindrical holes is about 1μm-20μm (depending on the overall size of the chip) , the inner diameter of the cylindrical hole is 5μm-30μm (depending on the chip area), and the concentration of physical vapor deposition is 1e20cm -3 -5e20cm -3 B ion gas. Through experiments and simulation tests, when the same diffusion isolation region P+ is obtained, the diffusion time required by the present invention accounts for 1%-10% of the traditional diffusion method time. The chip edge area required by the structure is reduced by 80%-95%, thereby effectively reducing th...

Embodiment 2

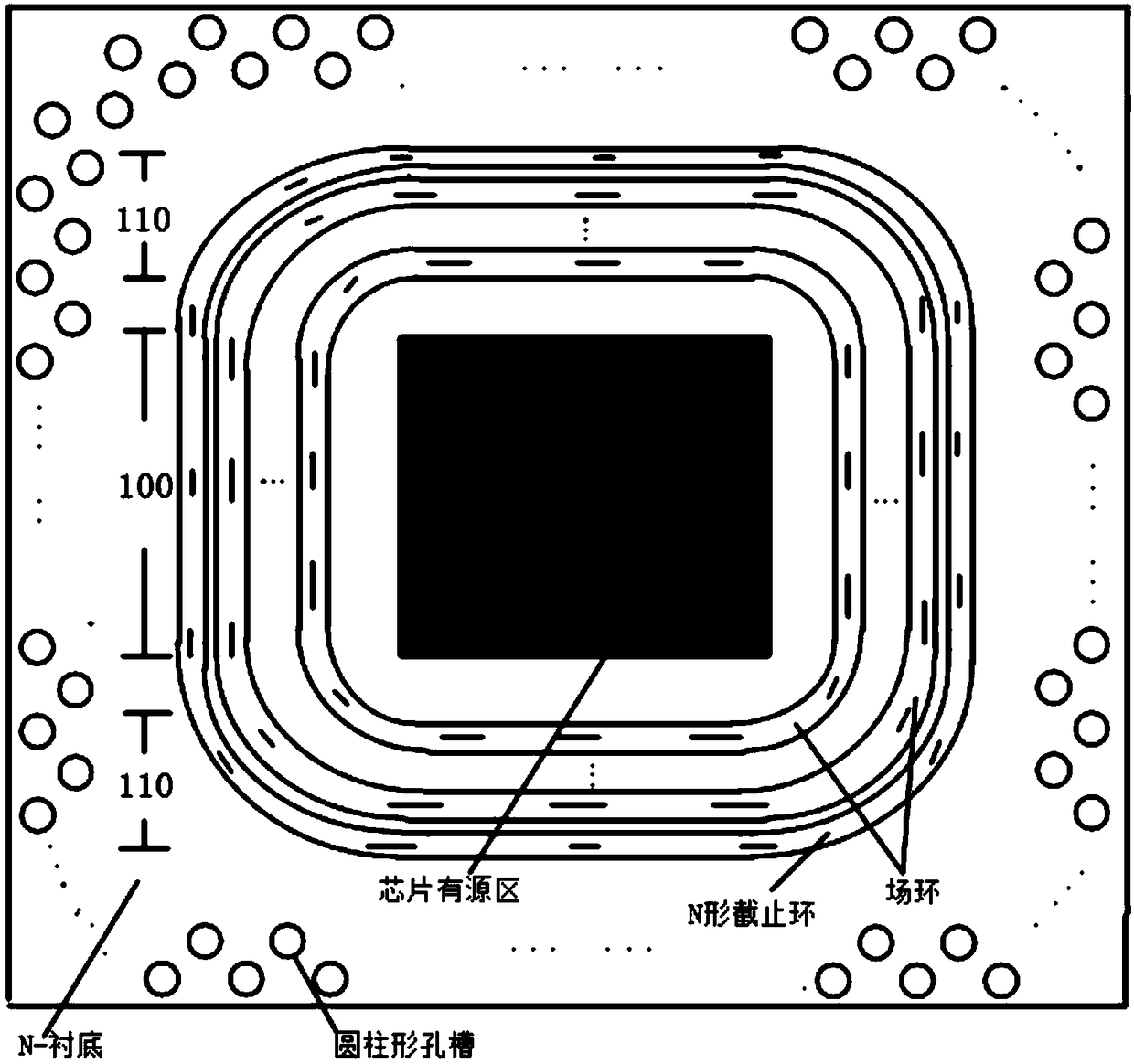

[0025] In this embodiment, a double-row isosceles triangular cylindrical hole array is used, such as figure 2 As shown, the N-substrate doping concentration is 1e13cm -3 —5e13cm -3 , Thickness 400μm-550μm (depending on the size of the withstand voltage). The width of the active area of the chip (100) is 200 μm-400 μm, the width of the terminal area (110) is 200 μm-1000 μm (according to the size of the withstand voltage), and the distance between the outermost cylindrical holes is about 10 μm-20 μm (according to the overall size of the chip) fixed), the inner cylindrical hole and the outermost two cylindrical holes form an isosceles triangle, and the distance between the outermost cylindrical hole and the inner cylindrical hole is 1μm-10μm (the distance between the outermost hole and the outer hole The distance between), the inner diameter of the cylindrical hole is 5μm-30μm (depending on the chip area), and the concentration of physical vapor deposition is 1e20cm -3 -5e2...

Embodiment 3

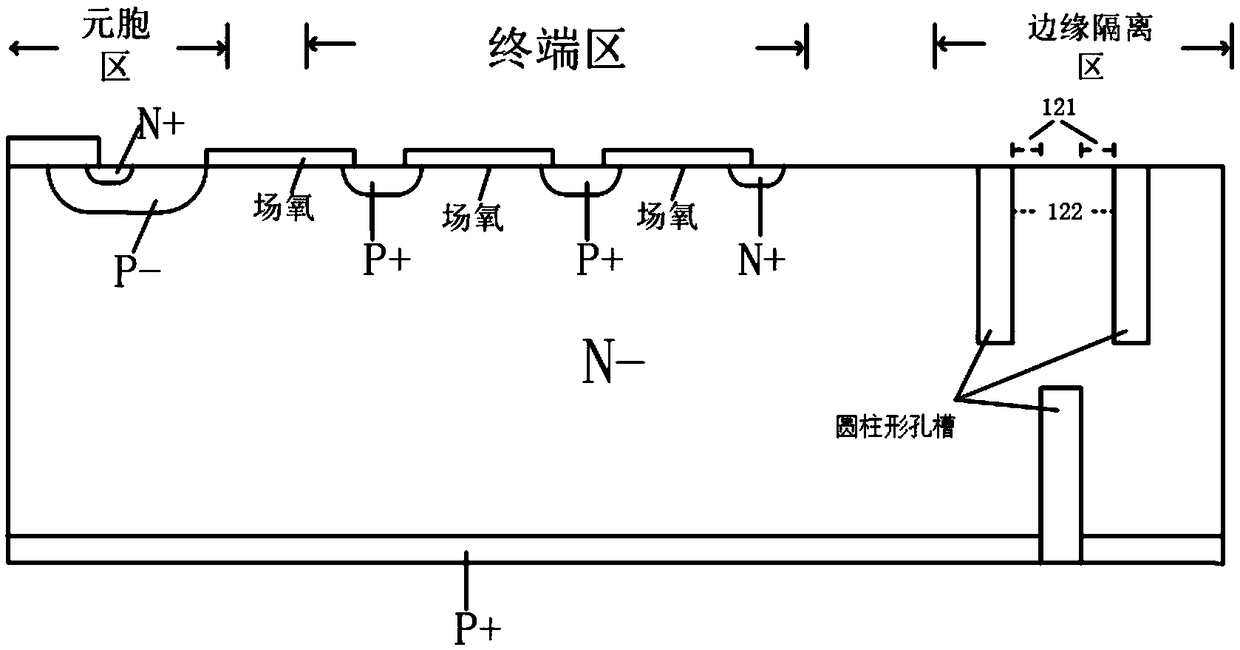

[0027] In this embodiment, a double-sided non-penetrating cross-cylindrical hole array is used, such as image 3 As shown in the chip section, the N-substrate doping concentration is 1e13cm -3 —5e13cm -3 , Thickness 400μm-550μm (depending on the size of the withstand voltage). The width of the active area of the chip is 200μm-400μm, the width of the terminal area is 200μm-1000μm (according to the size of the withstand voltage), the distance between the cylindrical holes on the surface of the chip (122) is about 10μm-20μm, the back hole groove and the two holes on the surface The lateral distance (121) of the groove is 1 μm-10 μm, the inner diameter of the cylindrical hole is 5 μm-30 μm, the depth of the groove accounts for 40%-60% of the substrate thickness, and the concentration of physical vapor deposition is 1e20cm -3 -5e20cm -3 The B ion gas, the cross distribution of the cylindrical holes on the chip surface and the cylindrical holes on the bottom of the chip is show...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More