Automatic control method and device of PCB layout

An automatic control device and layout technology, applied in the direction of printed circuit manufacturing, multilayer circuit manufacturing, electrical components, etc., can solve the problems of error-prone, cost-prone, manual omission, etc., and achieve the effect of avoiding poor tinning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

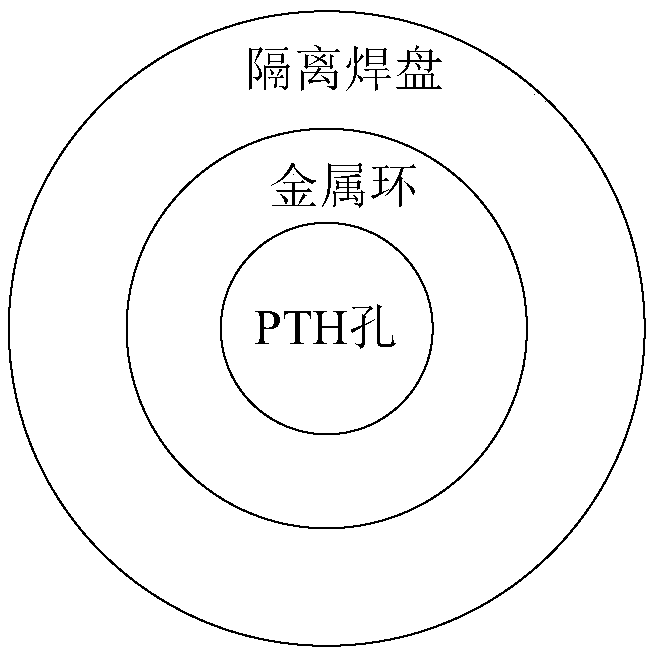

[0050] When using the allegro software developed by Cadence for PCB design, through the secondary development skill of the candence software, the number of connection layers of the PTH holes is limited. Once more than 3 layers are connected, the copper surface will be laid on the back and it will automatically follow the PTH. The antipad size of the hole is avoided. Specifically, when using the allegro software developed by Cadence for PCB design, by writing a skill program that limits the number of PTH hole connection layers and automatically avoids the copper surface of the same attribute according to the size of the antipad after the number of layers exceeds the limit, then the Skill program Put it into the Skill menu, and execute the Skill program to set the requirements for the number of connection layers for all PTH holes, and automatically avoid the problem of too many connection layers for PTH holes during layout design.

[0051] The specific steps can be as follows: ...

Embodiment 2

[0059] The automatic control method of the PCB layout of the embodiment of the present invention, comprises the steps:

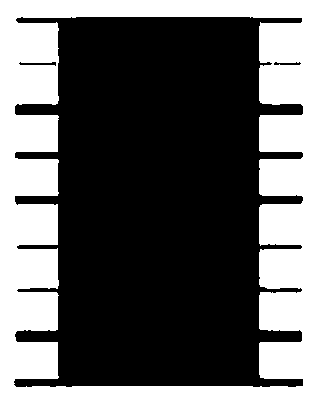

[0060] 1. If image 3 As shown, set the power pins of the slot, such as three 3v3 PTH holes on the left and four 12V PTH holes on the right.

[0061] 2. Run the skill program and the following dialog box will appear. Such as Figure 4 Shown:

[0062] 3. Select the PTH hole to be set to image 3 Take the 7 PTH holes as an example, select them and click OK.

[0063] 4. After the setting is completed, output the done command.

[0064] 5. When the fourth layer of copper surface is laid, it will automatically avoid the connection according to the antipad size of the PTH hole (take 12v as an example). Its effect is as Figure 5 shown.

[0065] image 3 and Figure 5 Among them, the black area covering 3V3 is the conductive copper skin of 3V3 property, and the black area covering 12v is the copper skin of 12v property, that is, the conductive copper skin ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More