Push-push injection-locking-type frequency multiplier circuit

A frequency multiplier and circuit technology, applied in the field of push-push note-lock frequency multiplier circuits, can solve the problems of narrow operating frequency range, large input signal swing, insufficient output power, etc., and can solve the point of high imaginary impedance. Matching problems, eliminating the use of DC blocking capacitors, and the effect of low input swing requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

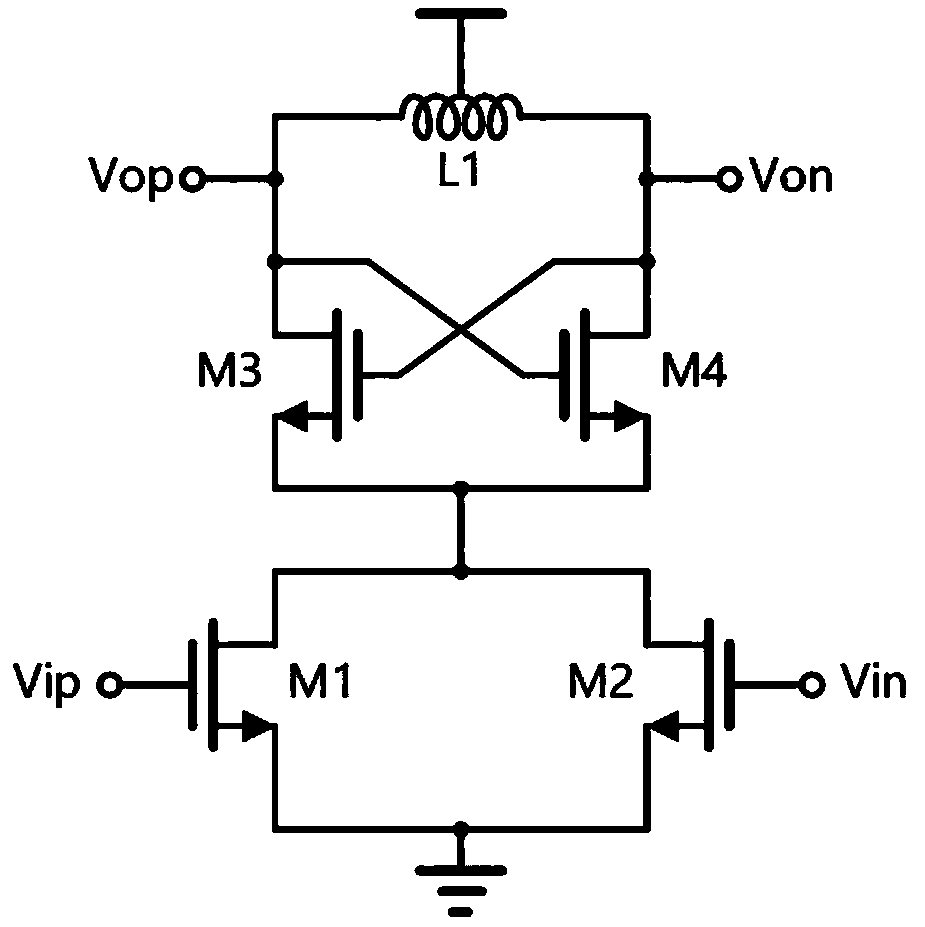

[0019] A push-push note-lock type frequency multiplier circuit, comprising: an input differential pair tube, a cross-coupled pair tube, and an LC circuit; the input differential pair tube is composed of a first NMOS tube M1 and a second NMOS tube M2; the first NMOS tube The drain of M1 is connected to the drain of the second NMOS transistor M2 to form a common drain terminal; the source of the first NMOS transistor M1 is connected to the source of the second NMOS transistor M2 to form a first common source terminal, and the first NMOS transistor M2 A common source terminal is grounded; the gate Vip of the first NMOS transistor M1 and the gate Vin of the second NMOS transistor M2 are connected to a pair of differential input signals; the cross-coupled pair of transistors is composed of the third NMOS transistor M3 and the fourth NMOS transistor M4; The gate of the third NMOS transistor M3 is connected to the drain of the fourth NMOS transistor M4 to form a first gate-drain conne...

Embodiment 2

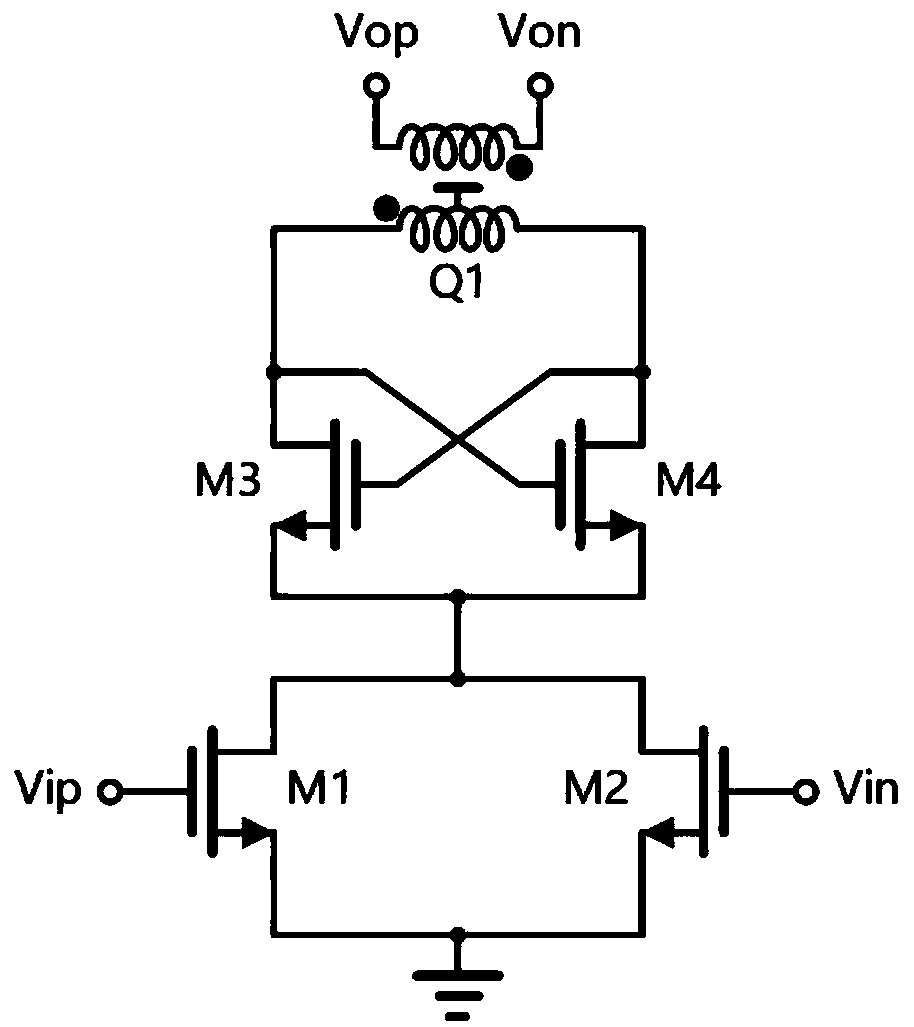

[0022]A push-push injection lock type frequency multiplier circuit, comprising: an input differential pair tube, a cross-coupled pair tube, and a transformer; the input differential pair tube is composed of a first NMOS tube M1 and a second NMOS tube M2; the first NMOS tube M1 The drain of the first NMOS transistor M2 is connected to the drain of the second NMOS transistor M2 to form a common drain terminal; the source of the first NMOS transistor M1 is connected to the source of the second NMOS transistor M2 to form a first common source terminal, and the first The common source terminal is grounded; the gate Vip of the first NMOS transistor M1 and the gate Vin of the second NMOS transistor M2 are connected to a pair of differential input signals; the cross-coupled pair of transistors is composed of the third NMOS transistor M3 and the fourth NMOS transistor M4; The gate of the third NMOS transistor M3 is connected to the drain of the fourth NMOS transistor M4 to form a first ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More