An FPGA implementation method of combined pulse compression and projectile velocity compensation for hypersonic platforms

A pulse compression, hypersonic technology, applied in radio wave measurement systems, instruments, etc., can solve the problems of high development cost, reduce signal processing efficiency, increase data interaction time, etc., to reduce the demand for hardware resources and improve signal processing. The effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

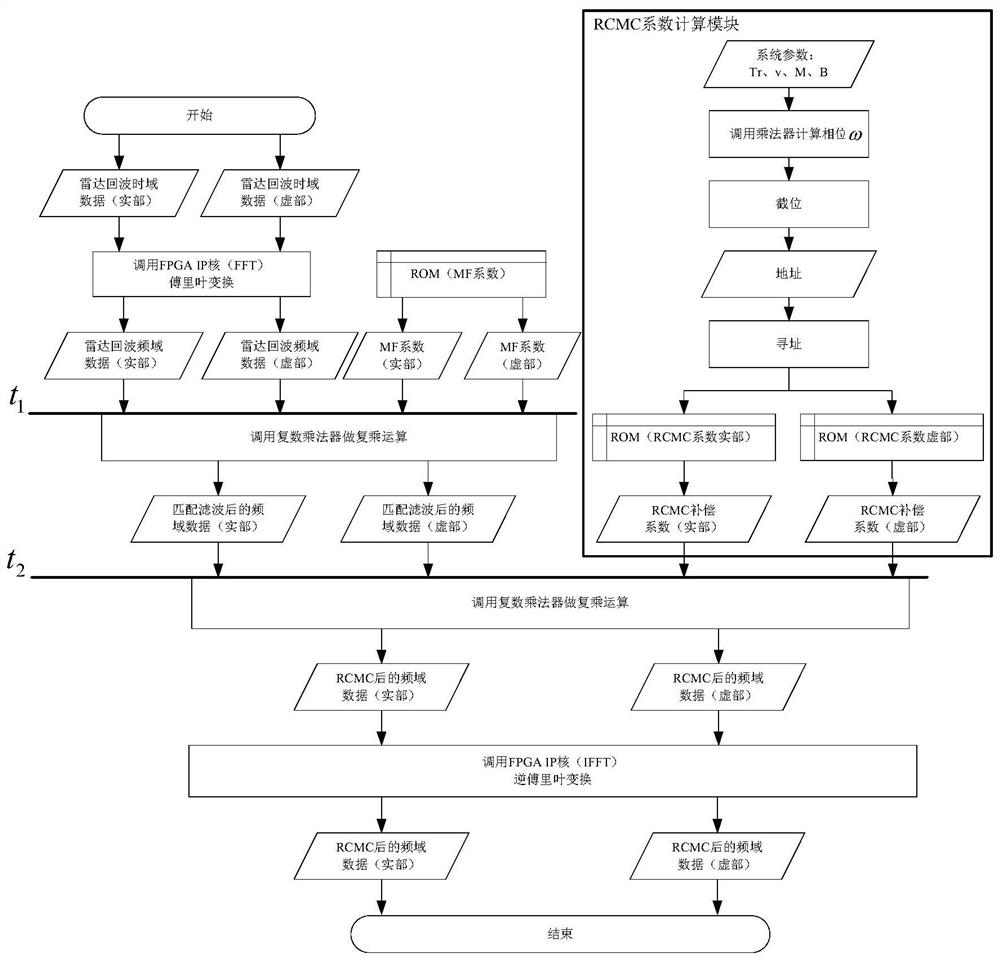

[0042] The present invention will be further elaborated below by describing a preferred specific embodiment in detail in conjunction with the accompanying drawings.

[0043] A kind of FPGA implementation method of hypersonic platform joint pulse compression and projectile velocity compensation of the present invention, it comprises the following steps:

[0044]S1, using the carrier frequency f 0 , bandwidth B, pulse duration T p , chirp frequency k, pulse number M, projectile distance R 0 , These parameters calculate the real part and the imaginary part of the radar echo time domain data, and the real part and the imaginary part of the frequency domain matched filter coefficient. In the present embodiment, the radar echo data is generated in MATLAB , matched filter (MF) coefficient; the real part and the imaginary part of frequency domain matched filter coefficient are stored in two coe files respectively, and these two coe files are stored in two ROMs respectively;

[0045...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More