Preparation method of improved SiC planar MOSFET device

An improved and device technology, which is applied in the field of preparation of improved SiC planar MOSFET devices, can solve the problems of difficulty in further reducing specific on-resistance and low carrier mobility, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0024] An improved preparation method of SiC planar MOSFET device includes:

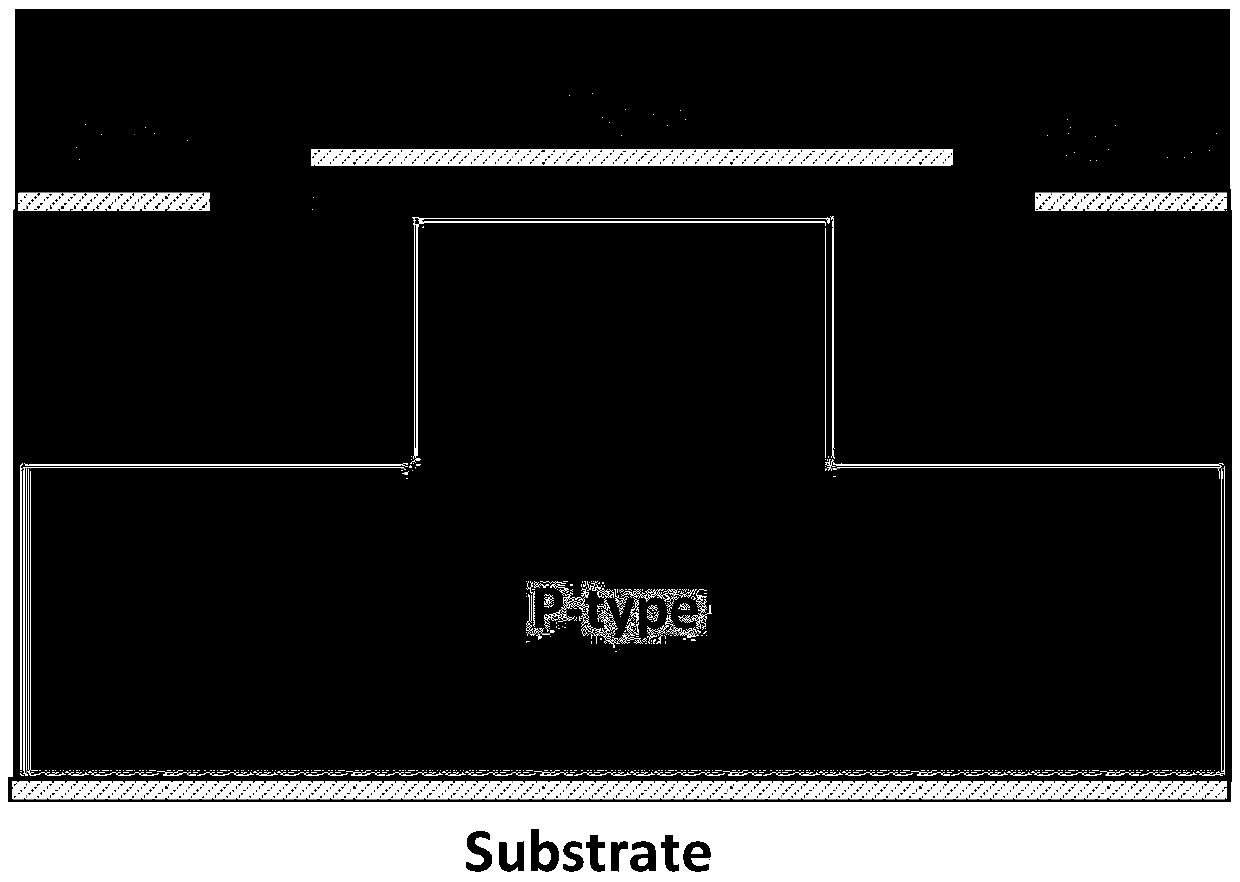

[0025] Prepare an epitaxial layer on the substrate;

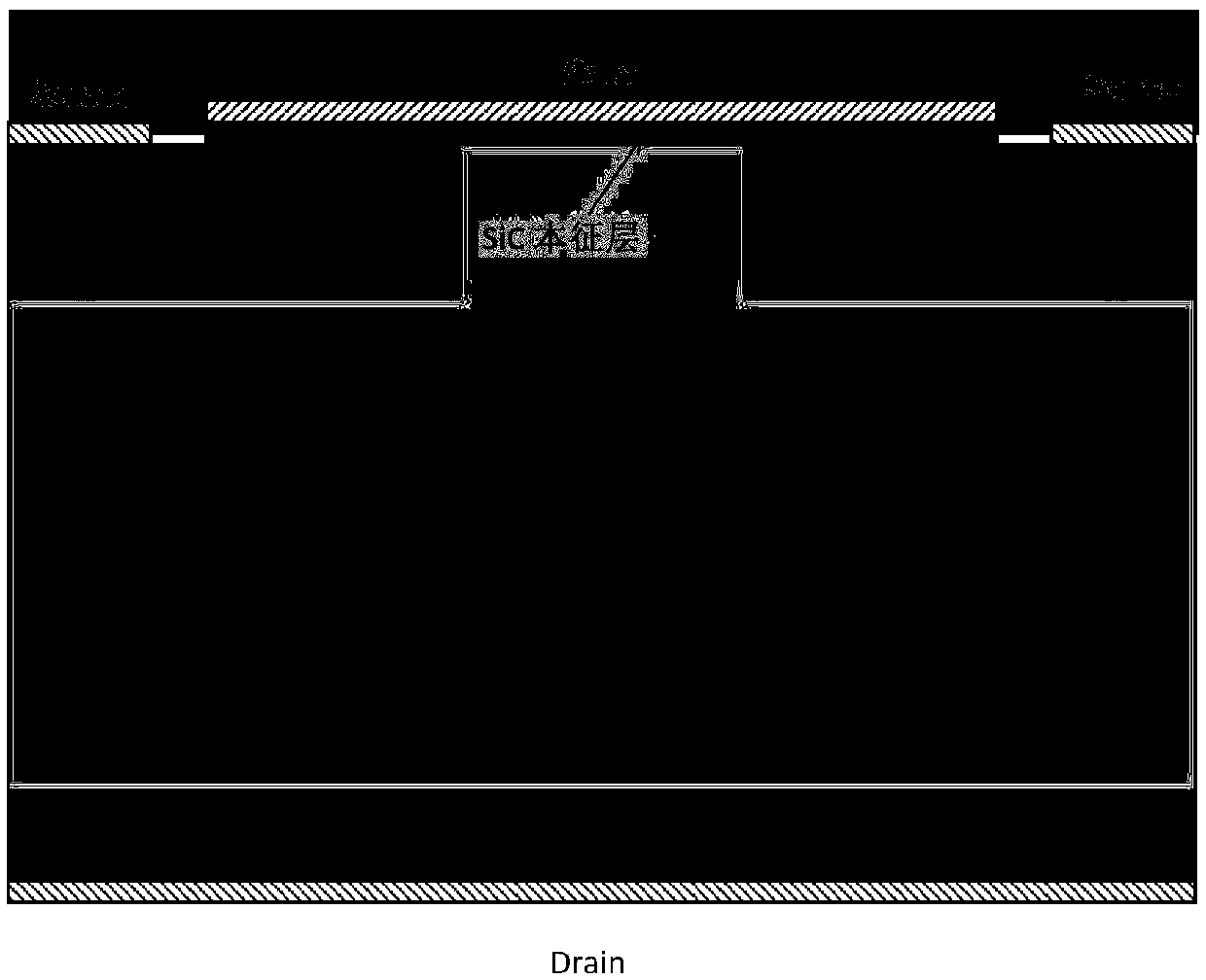

[0026] Grow a certain thickness of SiC intrinsic layer on the surface of the epitaxial layer;

[0027] P-well regions are formed on the surface of the epitaxial layer through mask deposition, photolithography, etching and implantation processes;

[0028] N+ source region is formed by mask deposition, photolithography, etching and implantation processes;

[0029] P+ source contact area through mask deposition, photolithography, etching and implantation processes;

[0030] Forming a gate oxide layer through a thermal oxidation process;

[0031] Polysilicon is formed on the surface of the gate oxide layer through a polysilicon deposition process, and a polysilicon electrode is formed through a polysilicon etching process;

[0032] Depositing the gate-source isolation dielectric, and opening the source contact hole through an etching process;

[0033] Metallization...

Embodiment

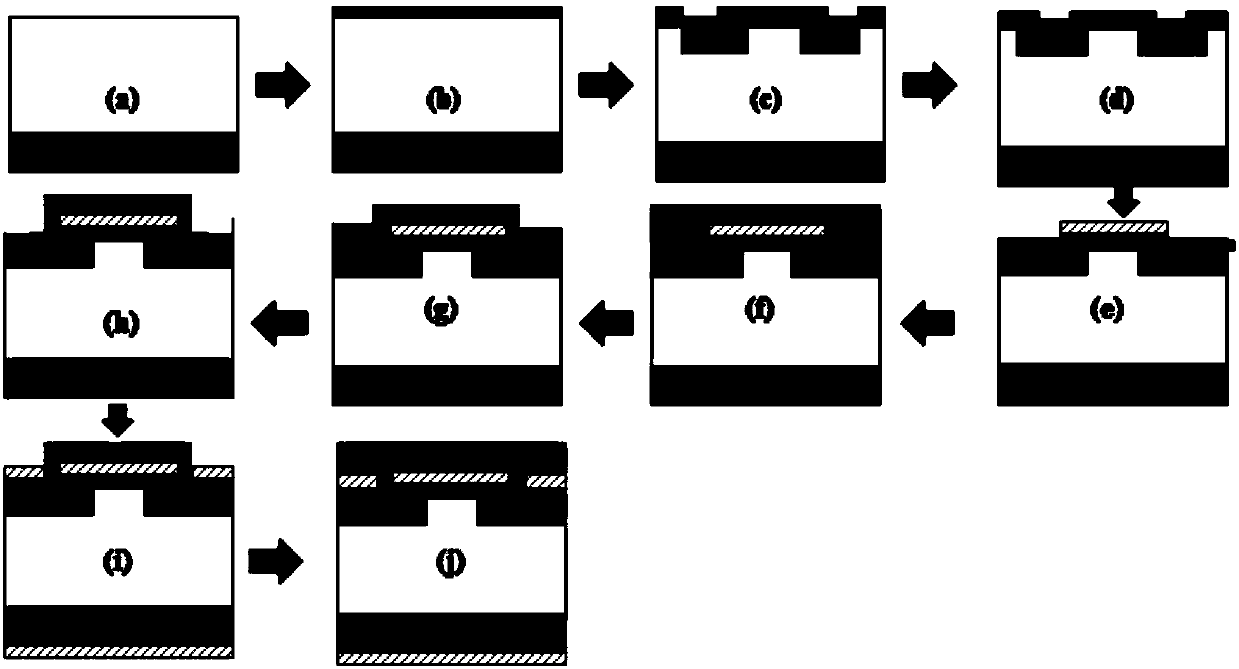

[0046] Such as figure 1 As shown, a method for preparing an improved SiC planar MOSFET device structure includes the following steps:

[0047] (1) Grow an epitaxial layer with a certain thickness on the surface of a heavily doped SiC substrate, such as figure 1 (a) Shown.

[0048] (2) A certain thickness of SiC intrinsic layer is then grown on the surface of the epitaxial layer, such as figure 1 (b) Shown.

[0049] (3) Growing a certain thickness of the implanted mask medium on the surface of the epitaxial layer, and forming such as photolithography, etching and implantation processes figure 1 (c) The mask shape is shown, and P-well ion implantation is performed. The implanted impurities are high-energy Al ions. At the end of the implantation, the mask medium on the surface is removed.

[0050] (4) Growing a certain thickness of the implanted mask medium on the surface of the epitaxial layer, and forming such as photolithography, etching and implantation processes figure 1 (d) The ma...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More