Wafer Back Process Method for Super Junction Devices

A backside process, super junction technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as residual defects and particles that cannot be cleaned, and achieve the effect of avoiding poor thickness uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

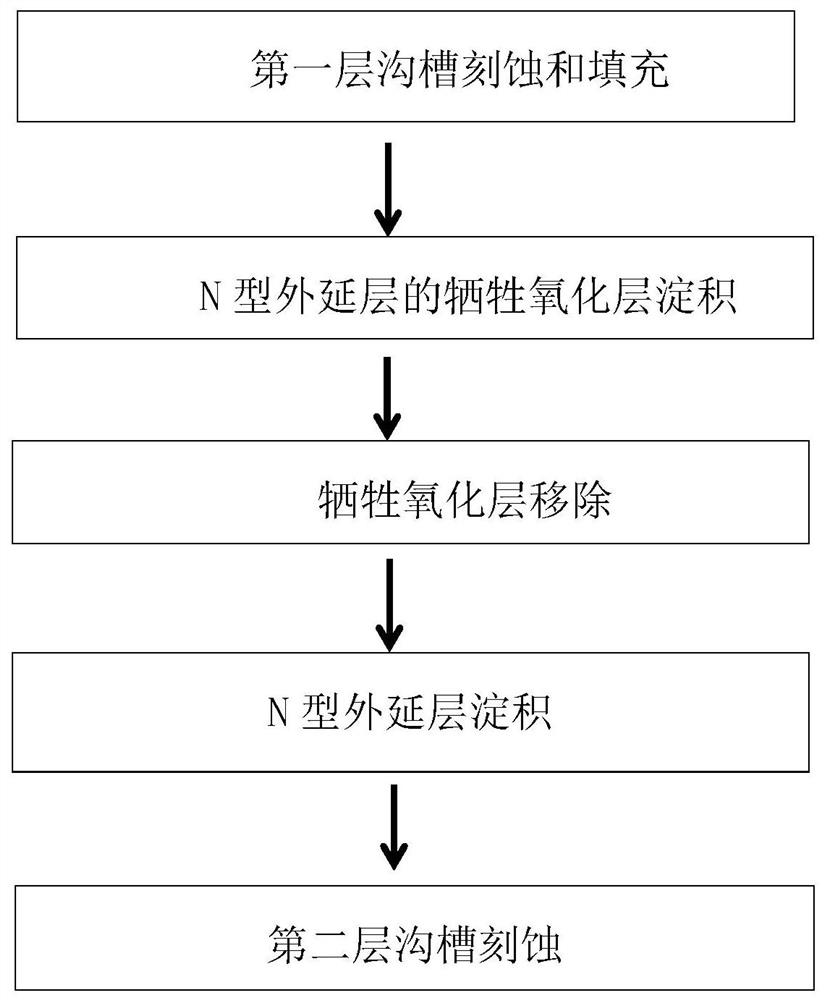

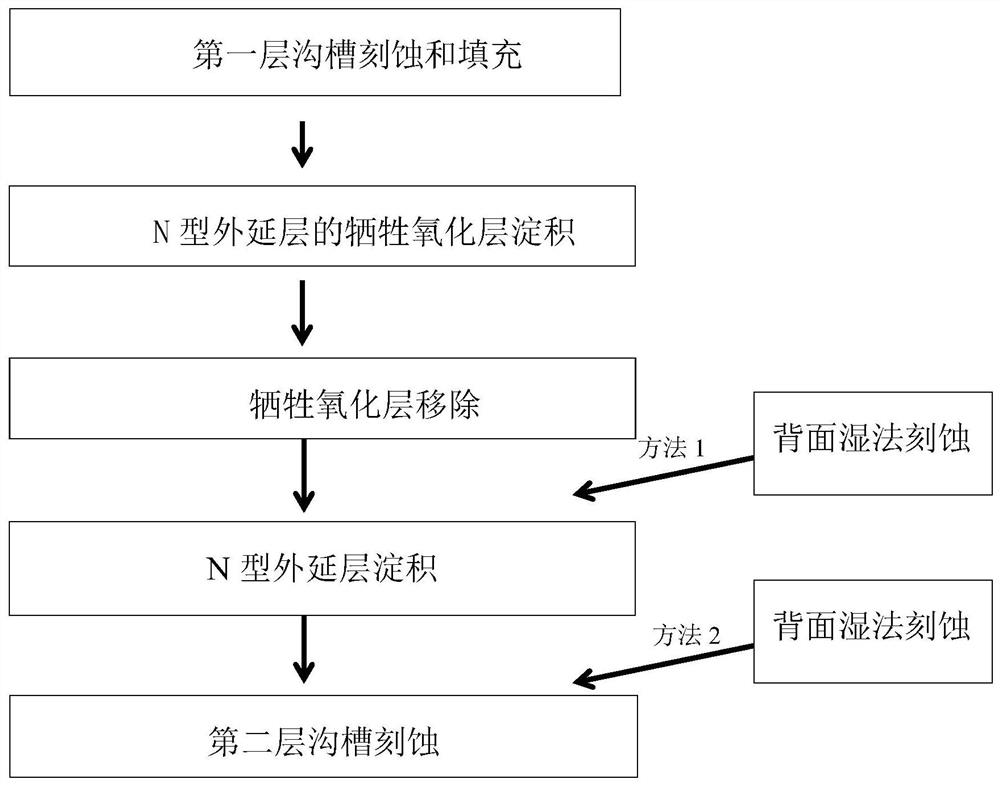

[0029] The process method for the backside of the wafer of the super junction device according to the present invention is a process of making the superjunction device on the wafer, and the backside of the wafer has been attached with a backside sealing film. It includes the following process steps:

[0030] In the first step, a first-layer trench is formed by etching on a semiconductor substrate, such as a silicon substrate or a silicon epitaxial layer, and is filled by epitaxial deposition.

[0031] In the second step, the sacrificial oxide layer is deposited on the N-type epitaxial layer. Since there may be some defects on the surface of the material, these defects can be eliminated by forming a sacrificial oxide layer.

[0032] In step 3, the sacrificial oxide layer is removed.

[0033] In the fourth step, a wet etching process of polysilicon on the backside of the wafer is performed. All polysilicon is etched away by wet etching on the backside. Make sure that there i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More