Chip package structure and method for forming same

A chip packaging structure and wafer technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems affecting the performance of the packaging structure, reducing the size of semiconductor packaging, wafer peeling, etc., to improve packaging performance, improve warpage and Delamination phenomenon, the effect of reducing the thermal expansion coefficient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] A manufacturing process flow of a CoW package structure includes the following steps:

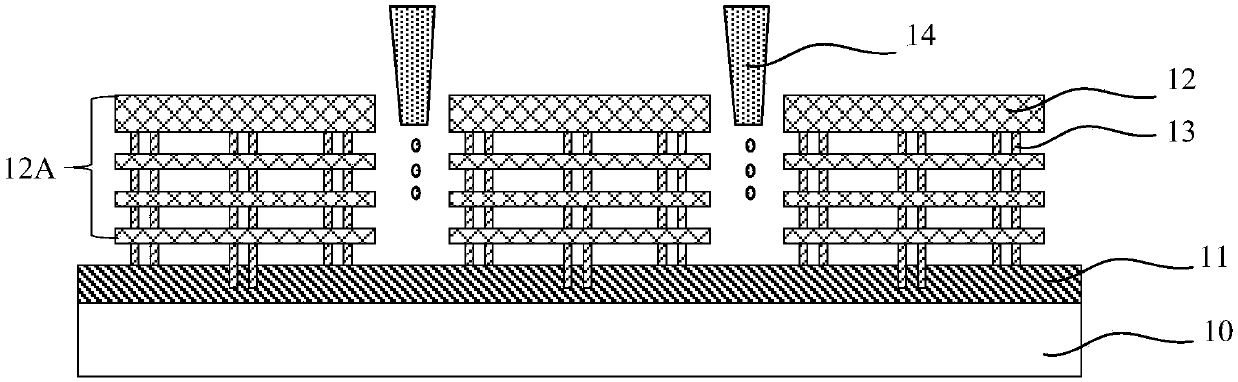

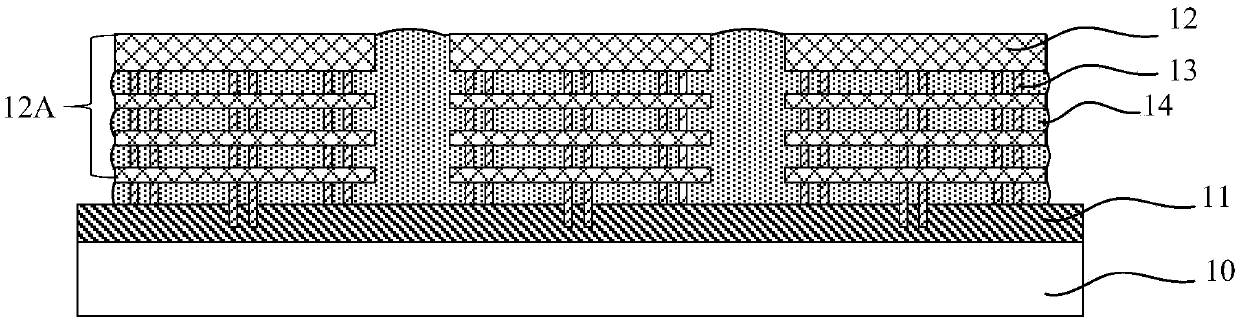

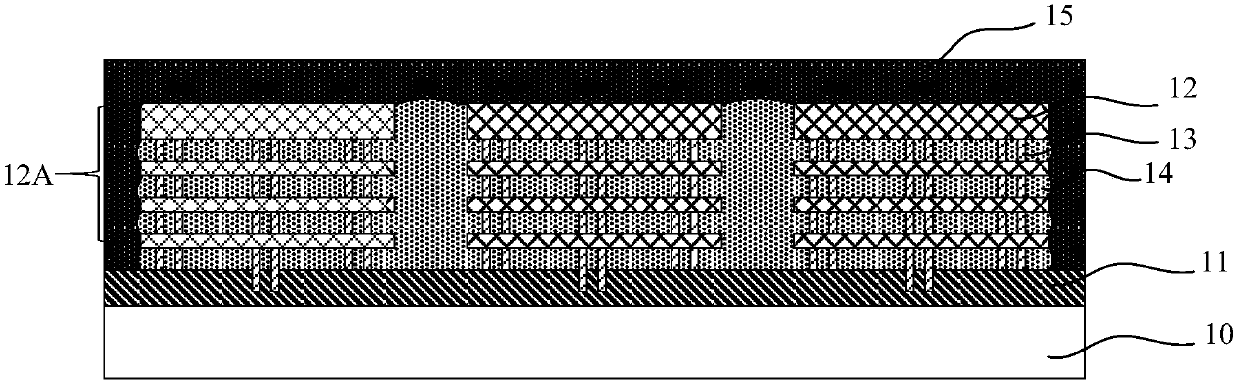

[0032] First, please refer to Figure 1A , paste a carrier 10 on the bottom of the element wafer 11 to support the element wafer 11;

[0033] Then, please continue to refer to Figure 1A stacking (Stacking) a plurality of chips (Die) 12 at corresponding positions on the surface of the component wafer 11, and completing the electrical interconnection between the chips 12 and between the chips and the component wafer 11 by means of reflow or thermocompression bonding, The TSVs (through silicon vias, used for vertical interconnection and conduction) 13 of two adjacent layers of wafers 12 are aligned and electrically contacted to form a plurality of wafer stacks 12A, Figure 1A It is shown that four wafers 12 are stacked into a chip stack 12A, but the actual number of wafers in each wafer stack is not limited to four, and the wafer 12 can be a memory chip such as DRAM or NAND, or a log...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More