An integrated test system and method for an FPGA high-speed SerDes interface

A technology for interface testing and integration testing, applied in error detection/correction, detection of faulty computer hardware, instruments, etc., can solve the problems of high test cost, high cost, long test time, etc., to achieve high scalability and flexibility effectiveness, reduce intervention, and improve test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

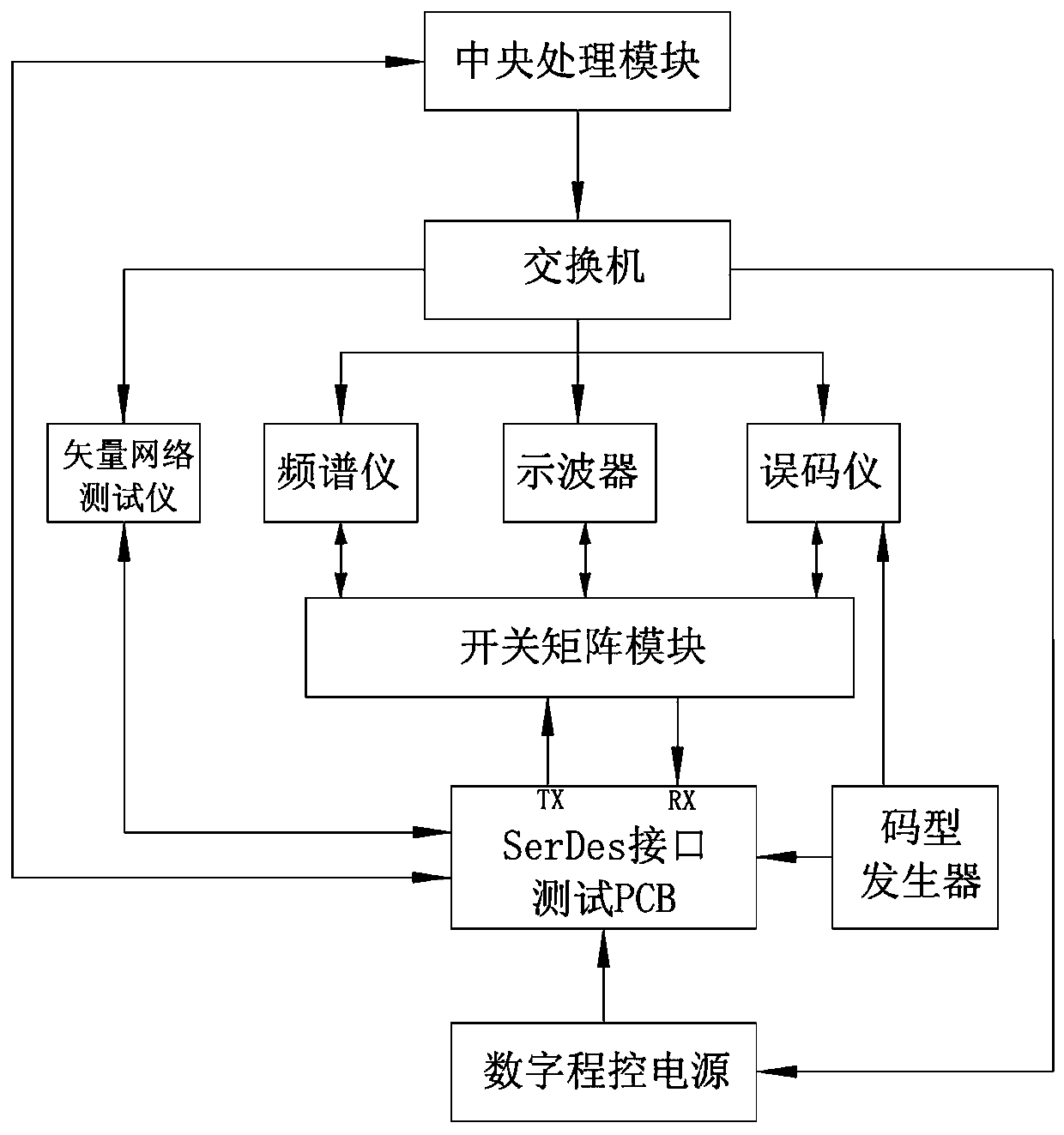

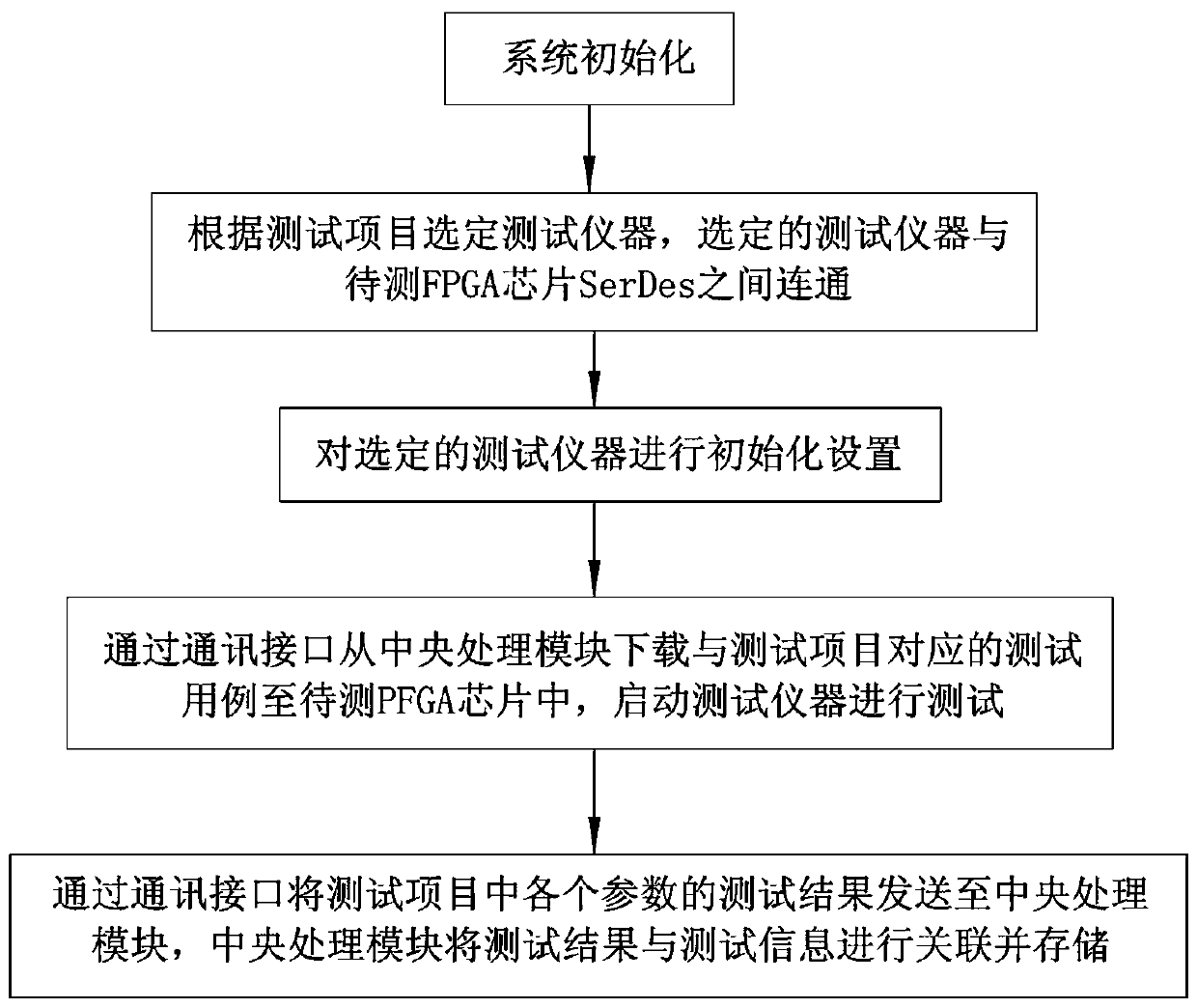

[0032] The invention discloses an integrated test system and method for an FPGA high-speed SerDes interface.

[0033] The test system includes 1. It includes a central processing module, a switch, a digital program-controlled power supply, a pattern generator, a test instrument module, and a SerDes interface test PCB. The first communication terminal of the central processing module is connected to the switch, and the test signal output end of the switch is connected through the test instrument module. SerDes interface test PCB, switch power signal output terminal is connected to SerDes interface test PCB through digital program-controlled power supply, the second communication terminal of central processing module is connected to SerDes interface test PCB, pattern generator sends reference clock signal to SerDes interface test PCB and test instrument module ;

[0034] The SerDes interface test PCB is provided with an FPGA test fixture for loading the FPGA chip to be tested, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More