Low-damage AlGaN/GaN HEMT gate groove etching method

A low-damage, gate-trough technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as inability to accurately control the etching accuracy, large surface damage to the etched sample, and uneven sample etching. Achieve the effect of reducing roughness, reducing bombardment, and reducing surface damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

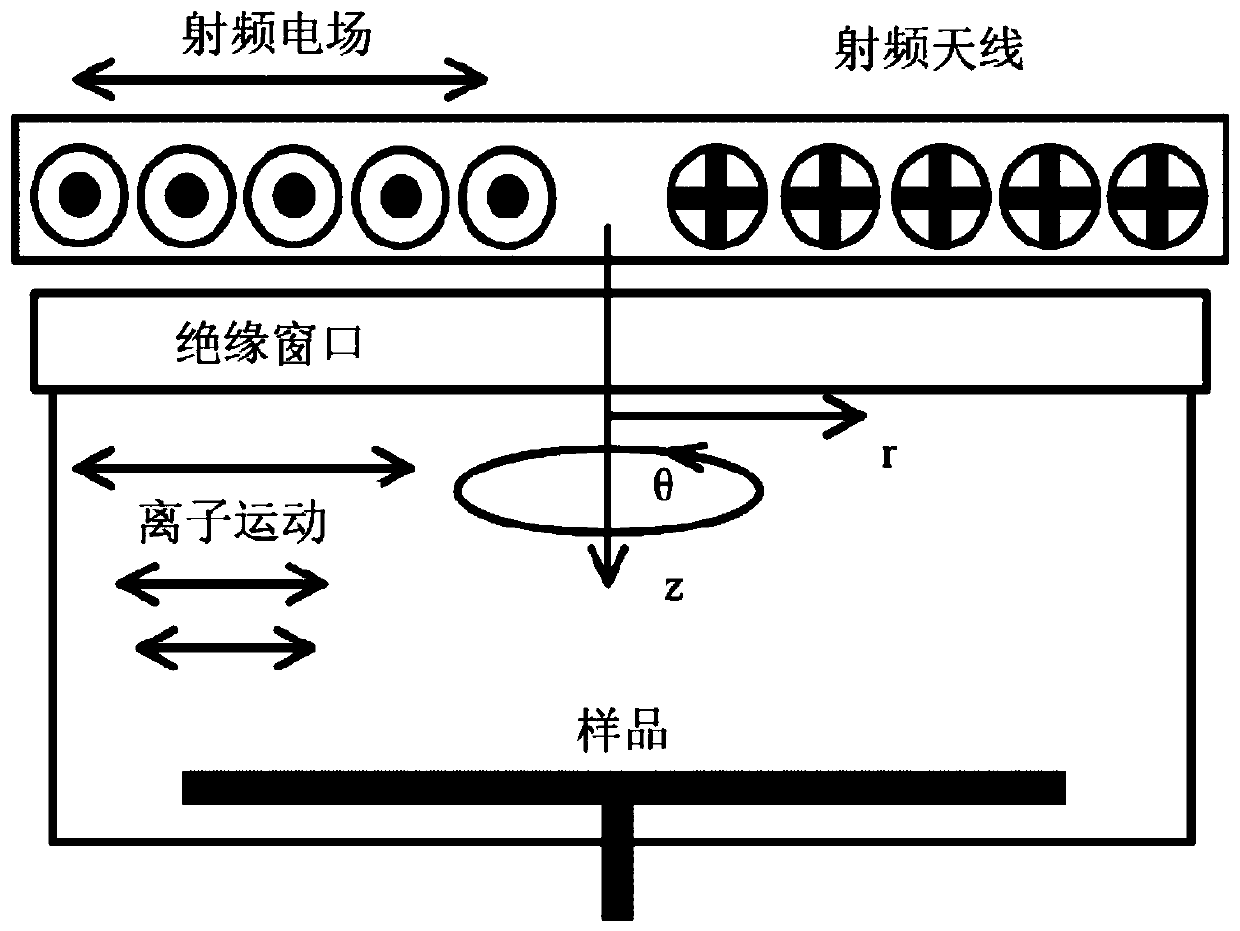

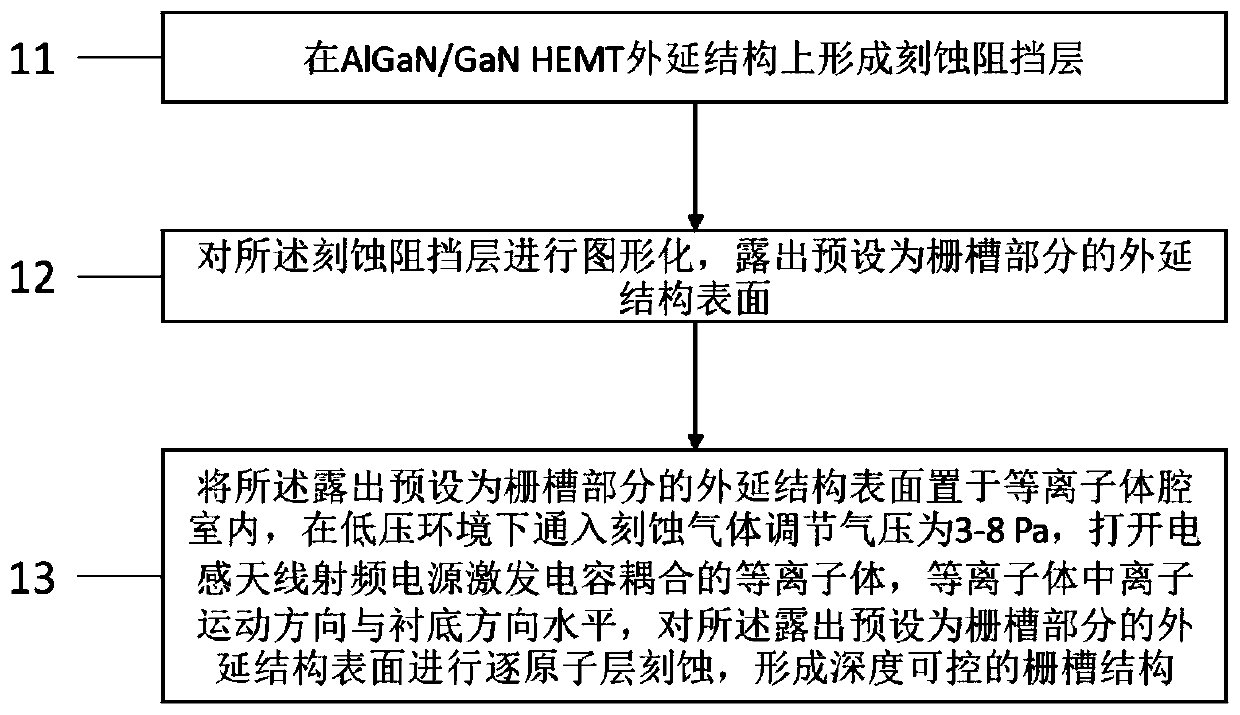

[0036] This embodiment provides a low-damage AlGaN / GaNHEMT gate groove etching method, see figure 1 , the method includes:

[0037] Step 11, forming an etching barrier layer on the AlGaN / GaN HEMT epitaxial structure;

[0038] Step 12, patterning the etching barrier layer to expose the surface of the epitaxial structure preset as the gate groove;

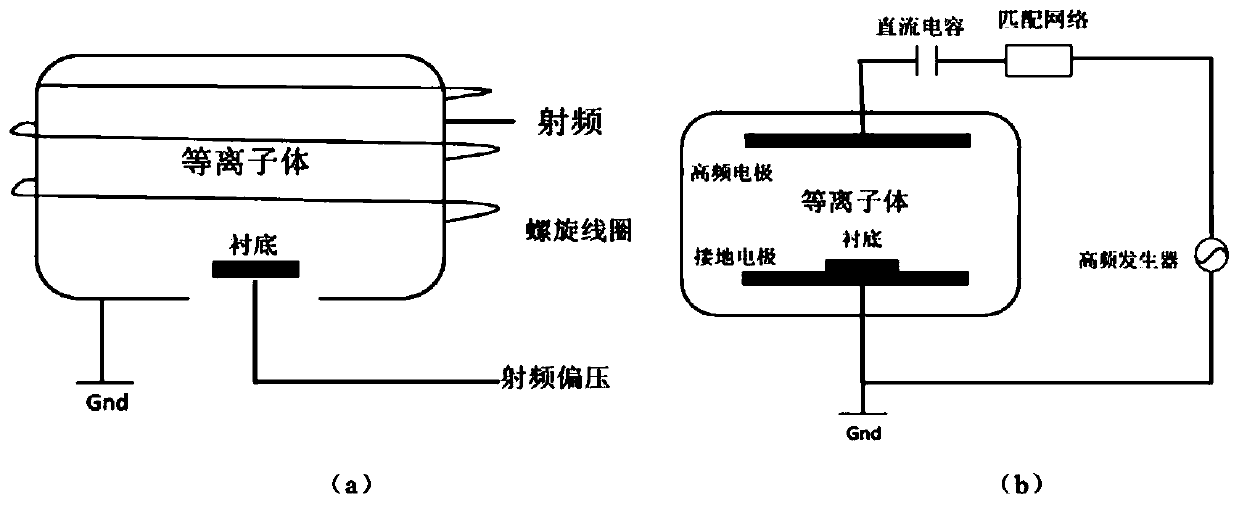

[0039] Step 13, placing the surface of the epitaxial structure exposed and preset as the gate groove in the plasma chamber, feeding etching gas in a low-pressure environment to adjust the pressure to 3-8Pa, and turning on the radio frequency power supply of the inductive antenna to excite capacitively coupled plasma , the moving direction of ions in the plasma is parallel to the direction of the substrate, and the surface of the epitaxial structure that is exposed and preset as the gate groove is etched atomically layer by atom to form a gate groove structure with a controllable depth.

[0040]The low-damage AlGaN / GaN HEMT gate gro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More