A time-to-digital converter system and multiple delay phase-locked loop including the system

A delay-locked loop, time-to-digital technology, applied in time-to-digital converter, analog/digital conversion, analog conversion, etc., can solve the problem of in-band quantization noise determination, etc., to improve spurs, reduce quantization noise, and reduce consumption The effect of power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below through specific embodiments in conjunction with the accompanying drawings. These embodiments are only used to illustrate the present invention, and are not intended to limit the protection scope of the present invention.

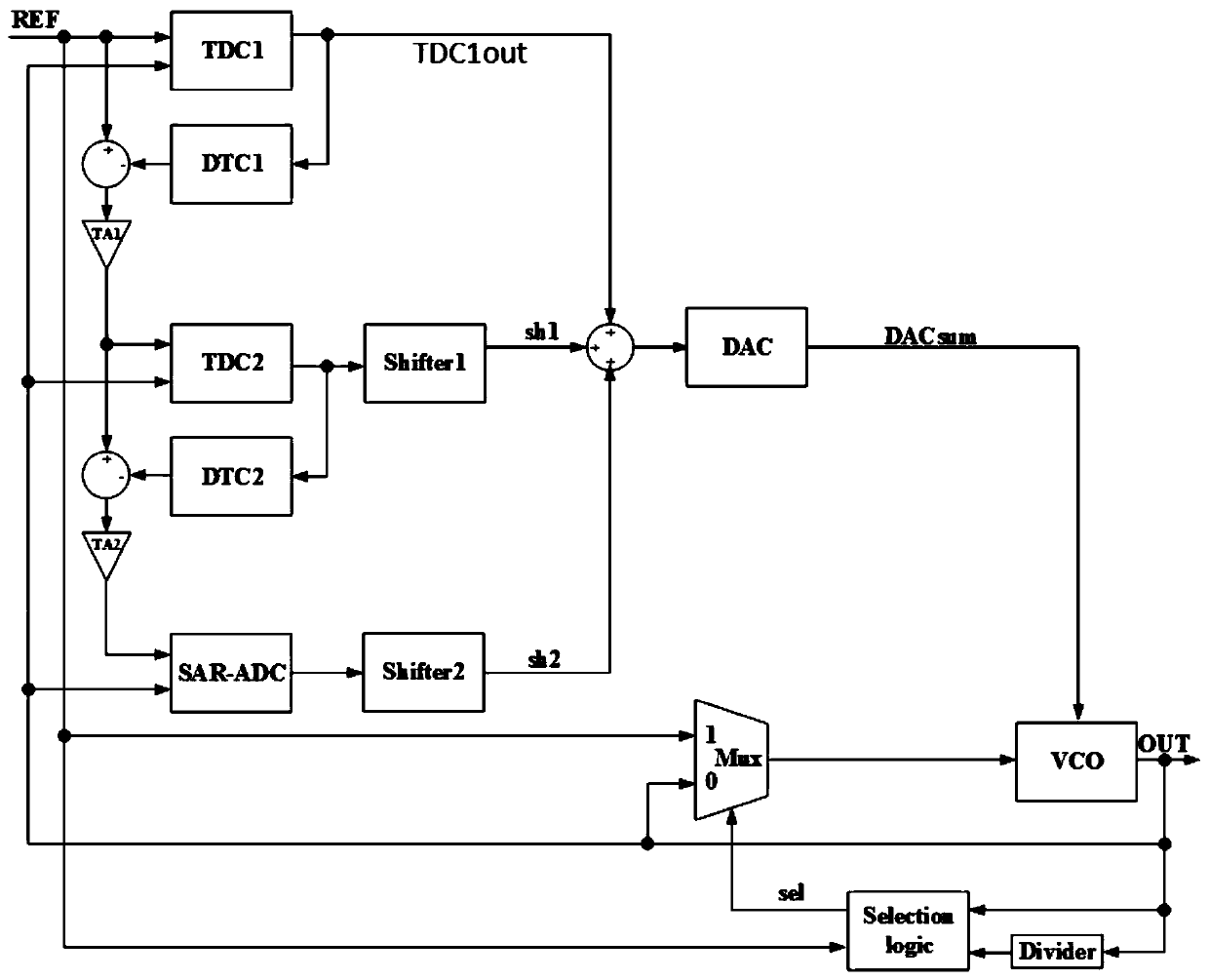

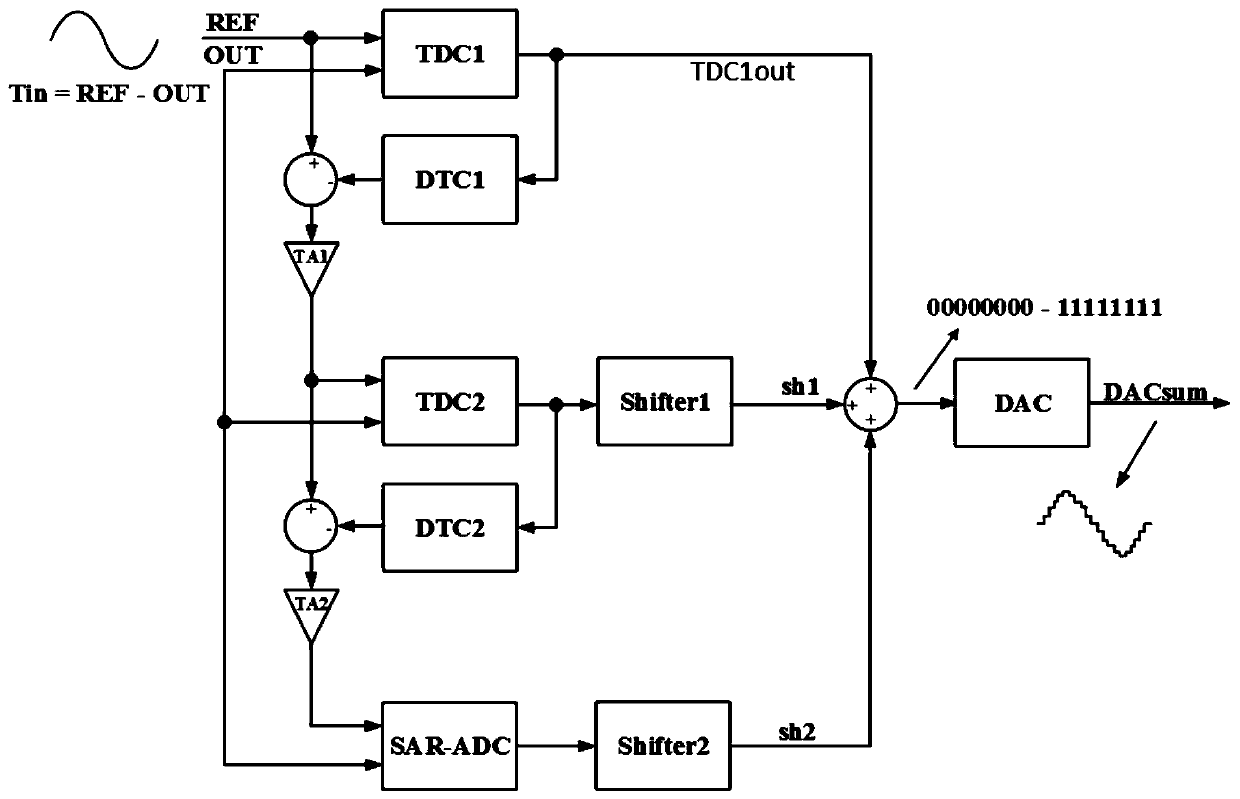

[0021] The present invention is a time-to-digital conversion system applied to a multiple delay phase-locked loop, mainly to realize innovation on the invention framework, and the time-to-digital converter, digital-to-time converter, time amplifier, digital-to-analog converter, successive approximation used in the present invention Register-type analog-to-digital converters and shifters are also commonly used circuit architectures. The two main circuits are time-to-digital converters and digital-to-time converters. The core architecture of time-to-digital converters is commonly used high-speed time-to-digital converters. , the digital time converter is mainly composed of a delay chain and a data se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More