Switched capacitor integrator offset voltage elimination circuit and elimination method thereof

A technology of offset voltage and switched capacitors, applied in the direction of eliminating voltage/current interference, electronic switches, instruments, etc., can solve the problem of low precision of the integrator, achieve a wide range of applications, realize the effects of simple structure and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

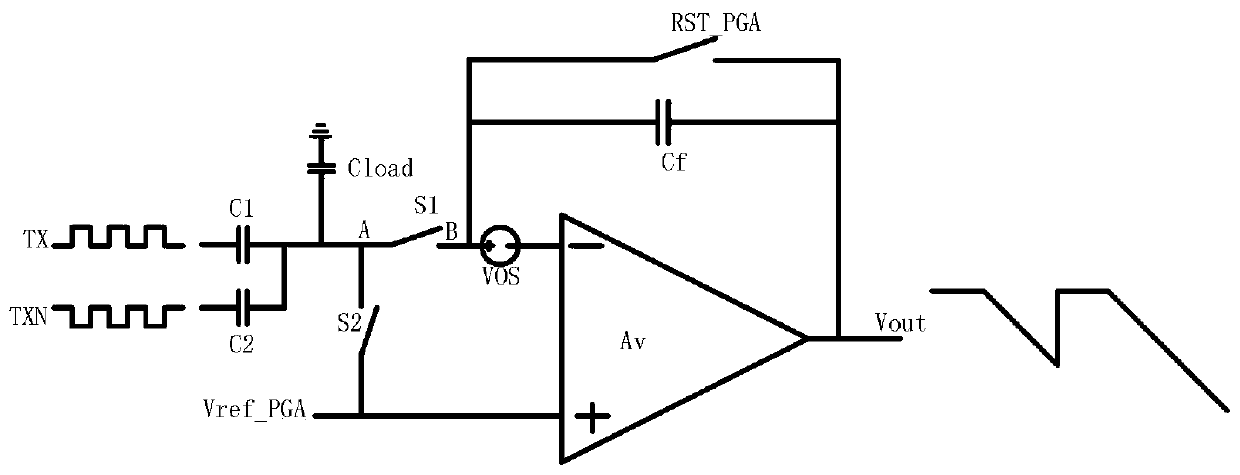

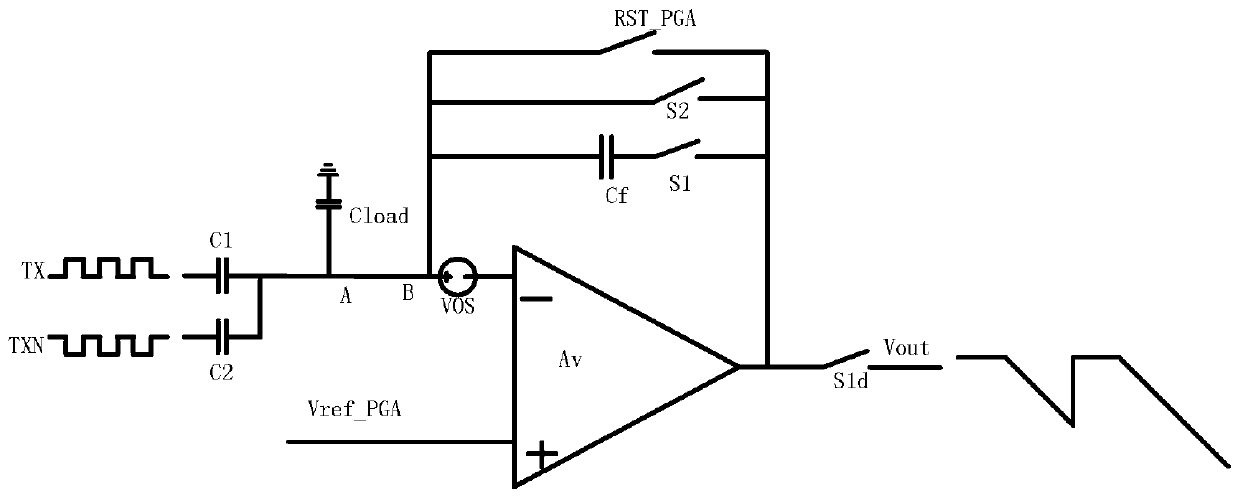

[0055] like figure 1 , figure 2 , image 3 As shown, a switched capacitor integrator offset voltage elimination circuit includes a first capacitor, a second capacitor, a third capacitor, a fourth capacitor, a first switch, a second switch, a third switch, a fourth switch, a reference voltage, VOS offset voltage source, integrator, one end of the first capacitor C1 is connected to the input signal, the second end is connected to the second end of the second capacitor C2, the first end of the third capacitor Cload, and the first end of the fourth capacitor Cf , the first end of the second switch S2, the first end of the third switch RST_PGA, and the first end of the VOS offset voltage source; one end of the first capacitor C2 is connected to the compensation signal, and the second end is connected to the second end of the first capacitor C1 Two terminals, the first terminal of the third capacitor Cload, the first terminal of the fourth capacitor Cf, the first terminal of the ...

Embodiment 2

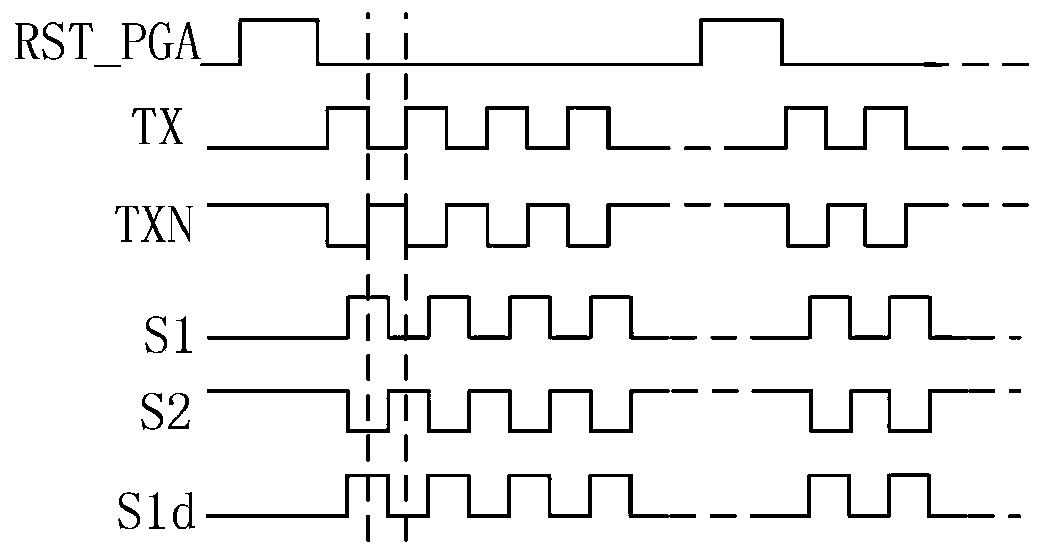

[0082] A method for eliminating a switched capacitor integrator offset voltage eliminating circuit, comprising the following specific steps:

[0083] S100: Carry out overall reset through the switch, so that the integral circuit has an integral initial voltage;

[0084] S200: TX transmits continuous pulses, the integrator integrates on the falling edge of TX (the rising edge of TXN) through the switch control, and resets on the rising edge (the falling edge of TXN);

[0085] S300: In the process of integration and reset, keep the DC point of the input capacitor close to the operational amplifier unchanged, and there is an offset voltage of VOS at the DC point;

[0086] S400: Through correlated double sampling technology, two integral subtractions are performed to eliminate the DC point VOS offset voltage.

[0087] Wherein, in the step S200, TX transmits continuous pulses, the integrator is controlled by the second switch to integrate at the rising edge of TXN, and reset at the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More