Asymmetric SAR ADC capacitor switch time sequence circuit and method

A technology of capacitive switching and switching timing, applied in electrical components, electrical signal transmission systems, signal transmission systems, etc., can solve the problems of reducing the layout area of SAR ADC switching power consumption, unable to meet the increasingly high requirements of ADC, and achieving area Saving, switching power consumption reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

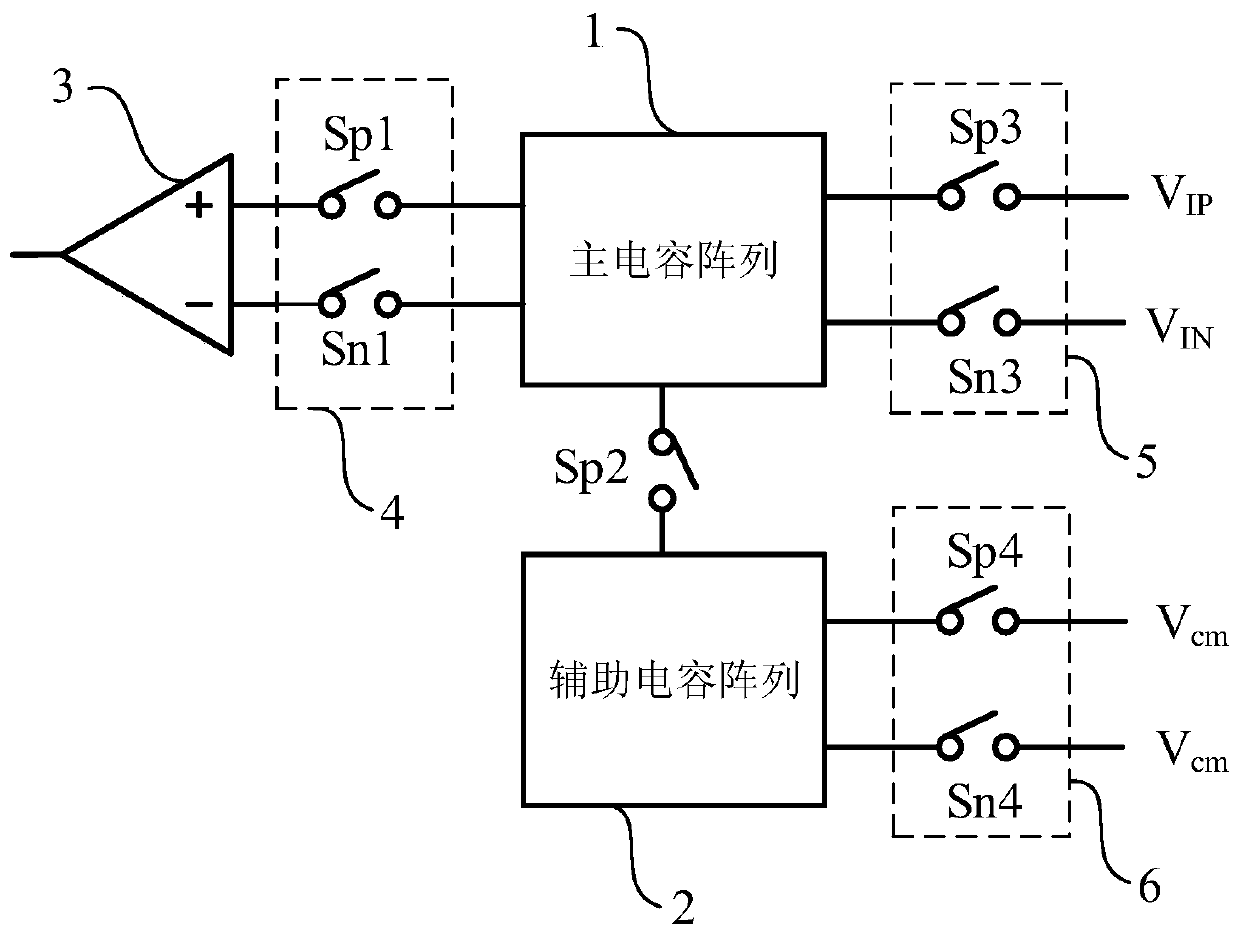

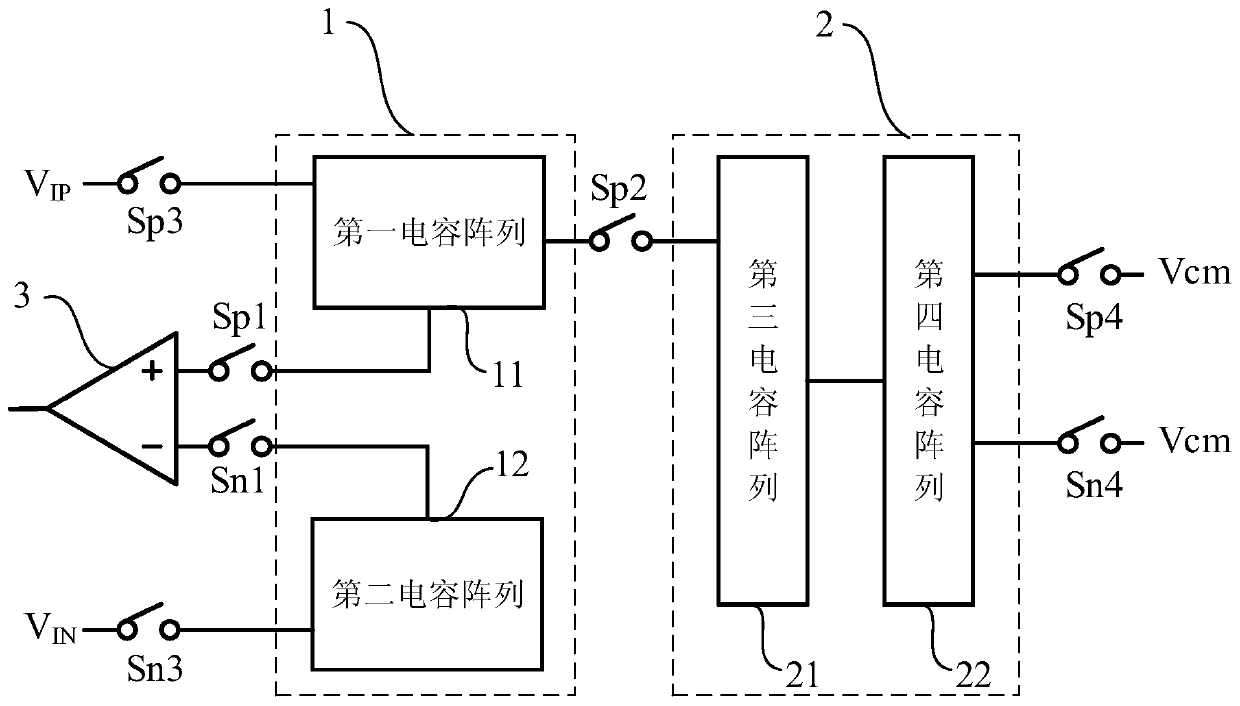

[0046] See figure 1 , figure 1 It is a structural schematic diagram of a novel low power consumption asymmetrical SAR ADC capacitor switching sequential circuit provided by an embodiment of the present invention.

[0047] A novel low-power asymmetrical SAR ADC capacitor switching sequential circuit provided by the present invention includes: a main capacitor array 1, an auxiliary capacitor array 2, a comparator 3, a first switch group 4, a second switch group 5, and a third switch Group 6, first input V IP and the second input V IN ;in,

[0048] The main capacitor array 1 is connected to the comparator 3 through a first switch group 4;

[0049] The first input V IP and the second input V IN Connect the main capacitor array 1 through the second switch group 5;

[0050] The main capacitor array 1 is connected to the auxiliary capacitor array 2 through a switch Sp2;

[0051] The auxiliary capacitor array 2 is connected to V through the third switch group 6 cm end.

[0052...

Embodiment 2

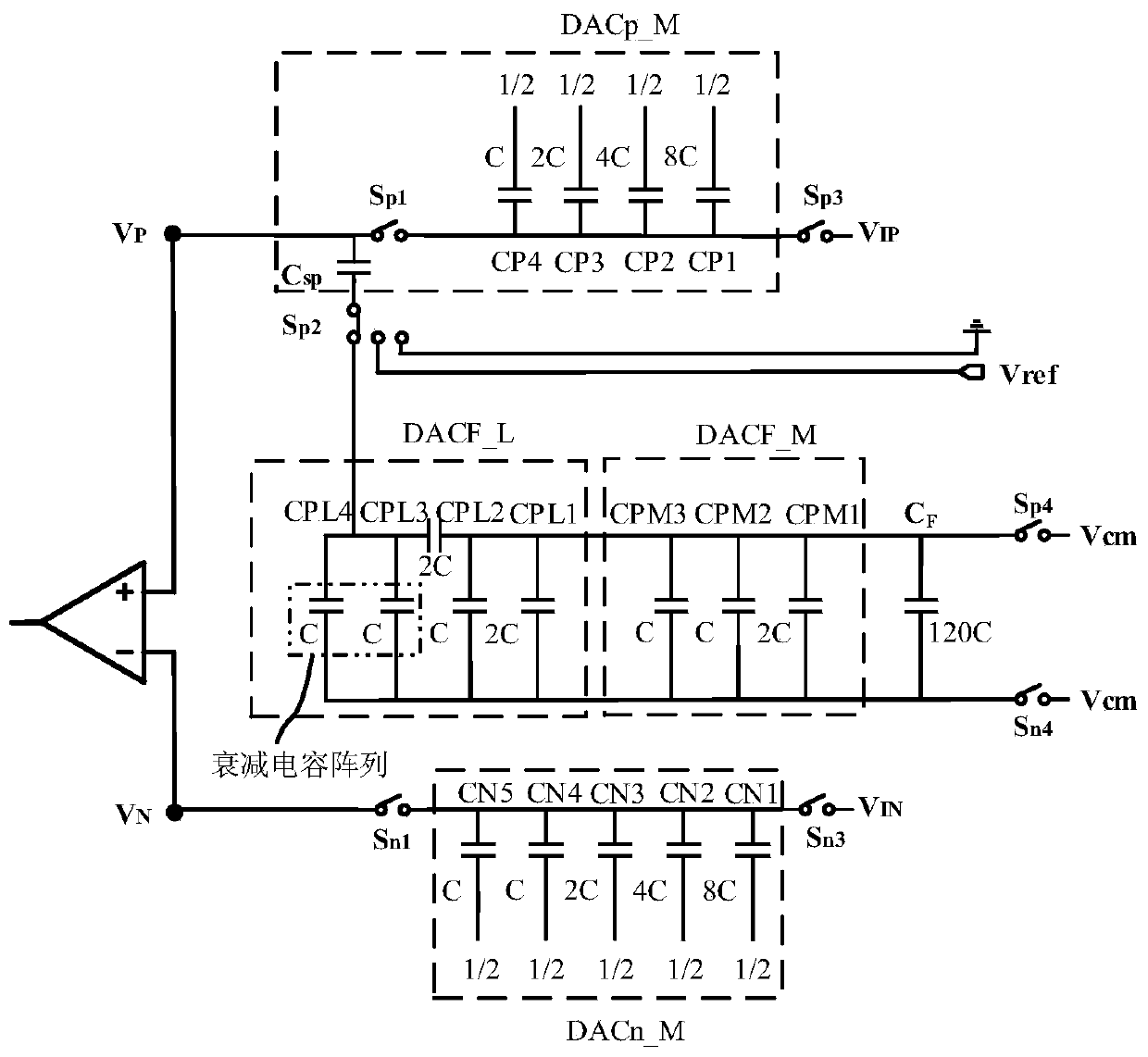

[0076] The timing steps are introduced below taking the capacitor array of the improved 10-Bit successive approximation analog-to-digital converter as an example.

[0077] In this embodiment, the main capacitor array adopts the novel switching sequence provided by the present invention to compare the six digital codes, the comparison of the first and second digits does not consume energy, and the monotonic capacitor switching sequence is used when comparing the sixth digit, only for The dummy capacitor of the DACn_M capacitor array operates, so that the dummy capacitor C of the DACp_M capacitor array sp Constantly connected to V cm The level ensures that the voltage change of the DACp_M capacitor array can be correctly coupled to the auxiliary capacitor array so that it can produce correct binary level changes. In the auxiliary array, the maximum capacitance is split and the improved V cm -based switching timing comparison of the lower four bits, segment capacitance C sr Af...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com