Method and system for repairing time sequence violations in chip design

A chip design and timing technology, applied in computing, special data processing applications, instruments, etc., can solve the problems of not being able to guarantee complete timing analysis, lack of control of results, and failure to meet design requirements, so as to save design time, Reduce design cost and save area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

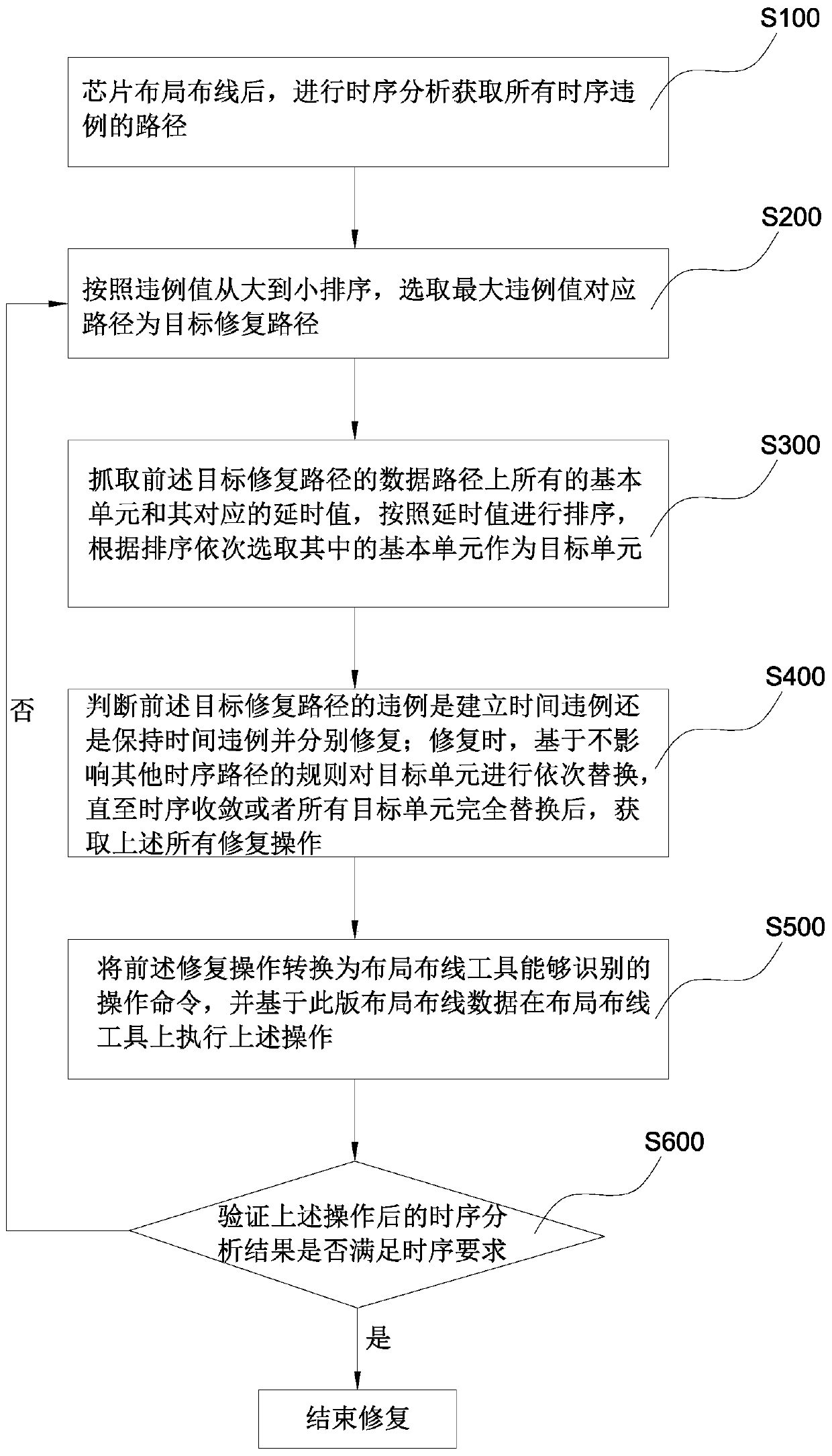

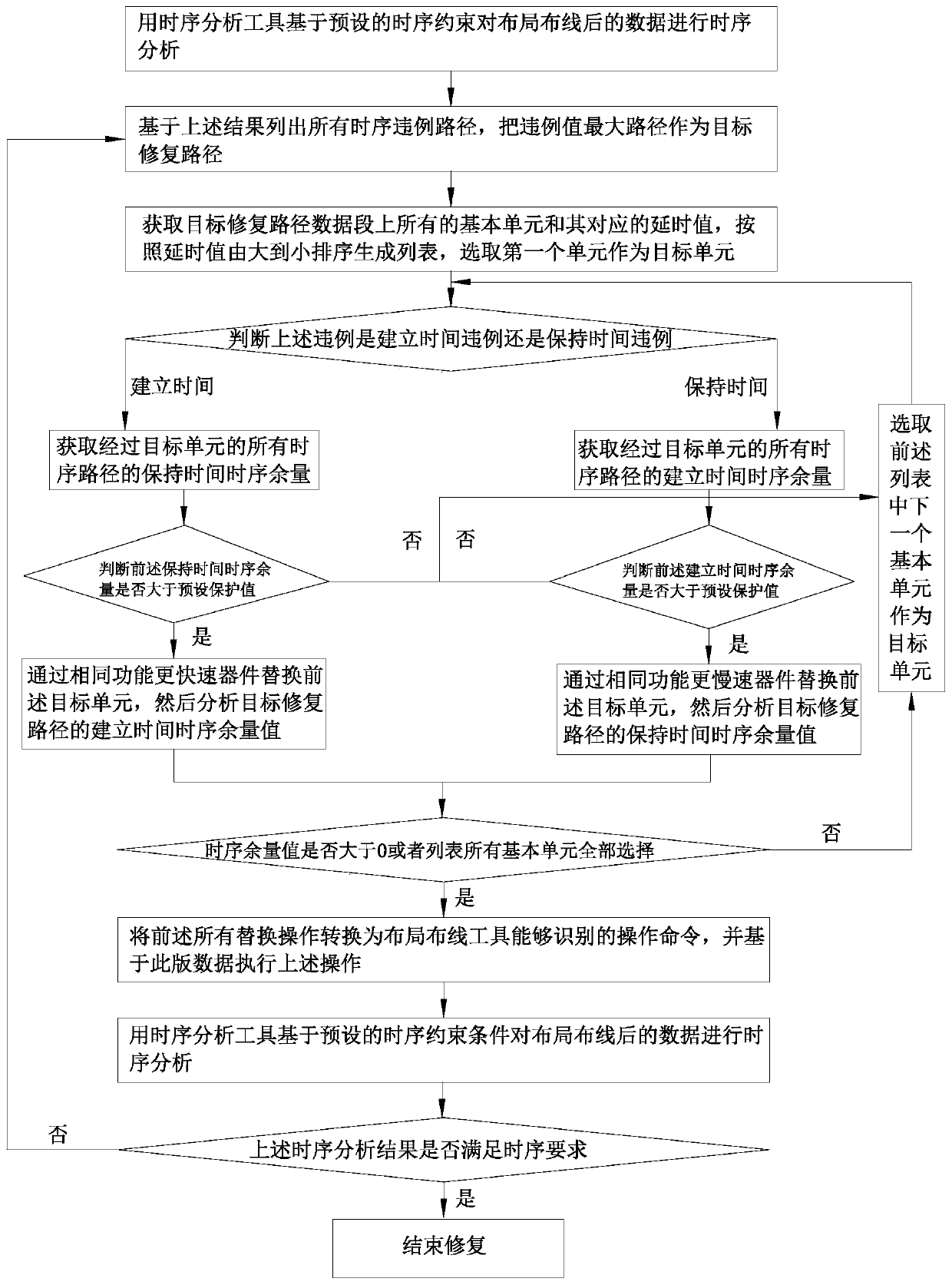

[0066] see figure 2 As shown, a method for repairing timing violations in chip design is provided, including the following steps:

[0067] Step 100, after the chip layout and routing, perform timing analysis based on timing analysis tools to obtain all timing violation paths.

[0068] After completing the chip layout and routing, extract the netlist information and SPEF (Standard Parasitic Parameter Exchange Format) information of the chip layout and routing, perform timing analysis based on the preset timing constraints under the timing analysis tool, and list according to the results of the aforementioned timing analysis Paths for all timing violations.

[0069] The preset timing constraint condition, as an example rather than limitation, may come from a timing constraint file in a design specification, for example.

[0070] Step 200, sort the violation values in descending order, and select the path corresponding to the largest violation value as the target repair path...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More