Method for generating filling graph of FDSOI standard unit and layout method

A standard cell and standard cell library technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve problems such as area waste and achieve the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0052] Image 6 It is a method for generating a filling pattern of an FDSOI standard cell provided in an exemplary embodiment of the present application. The method is applied to semiconductor manufacturing, and the method includes:

[0053] Step 601, acquire the parameters of the FDSOI standard cell in the standard cell library.

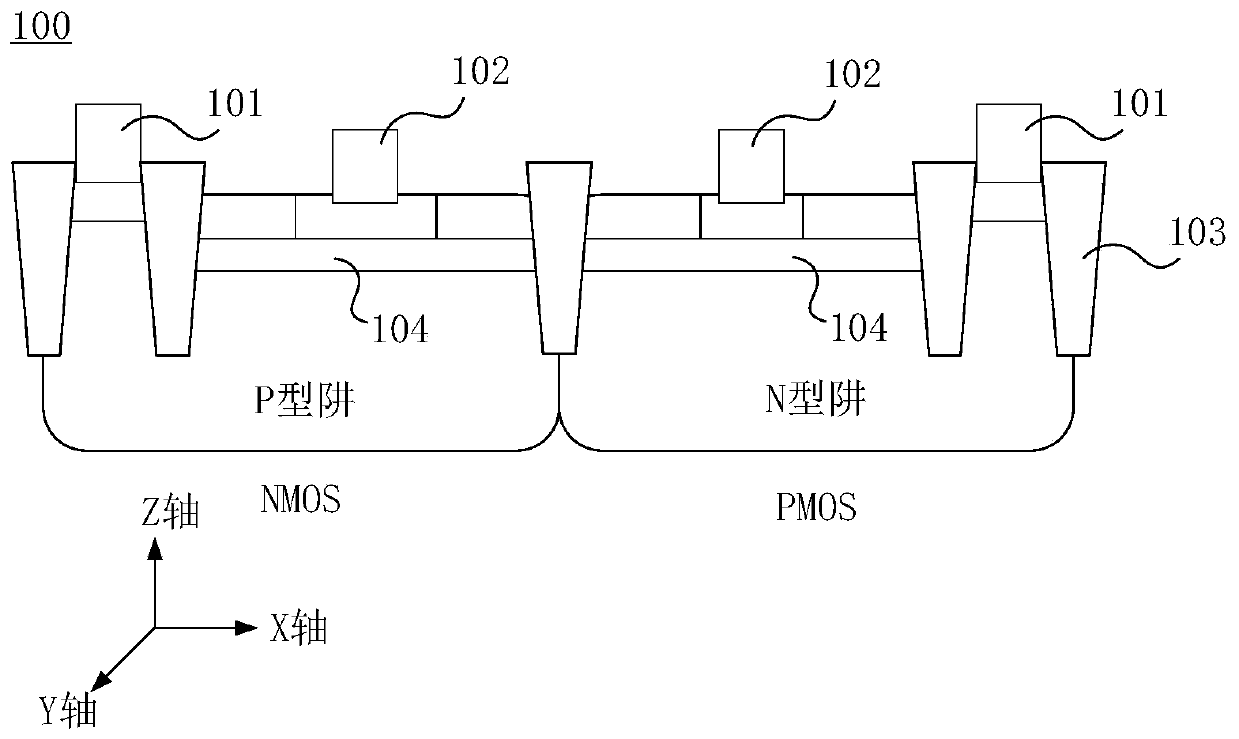

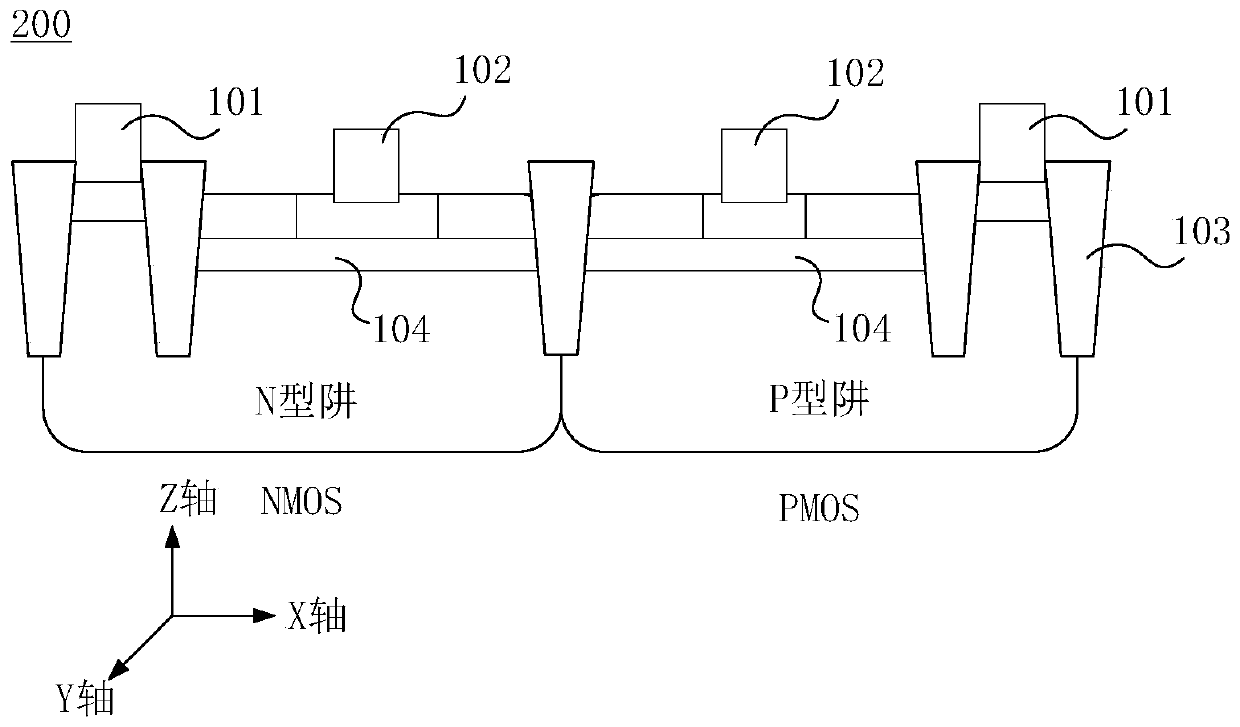

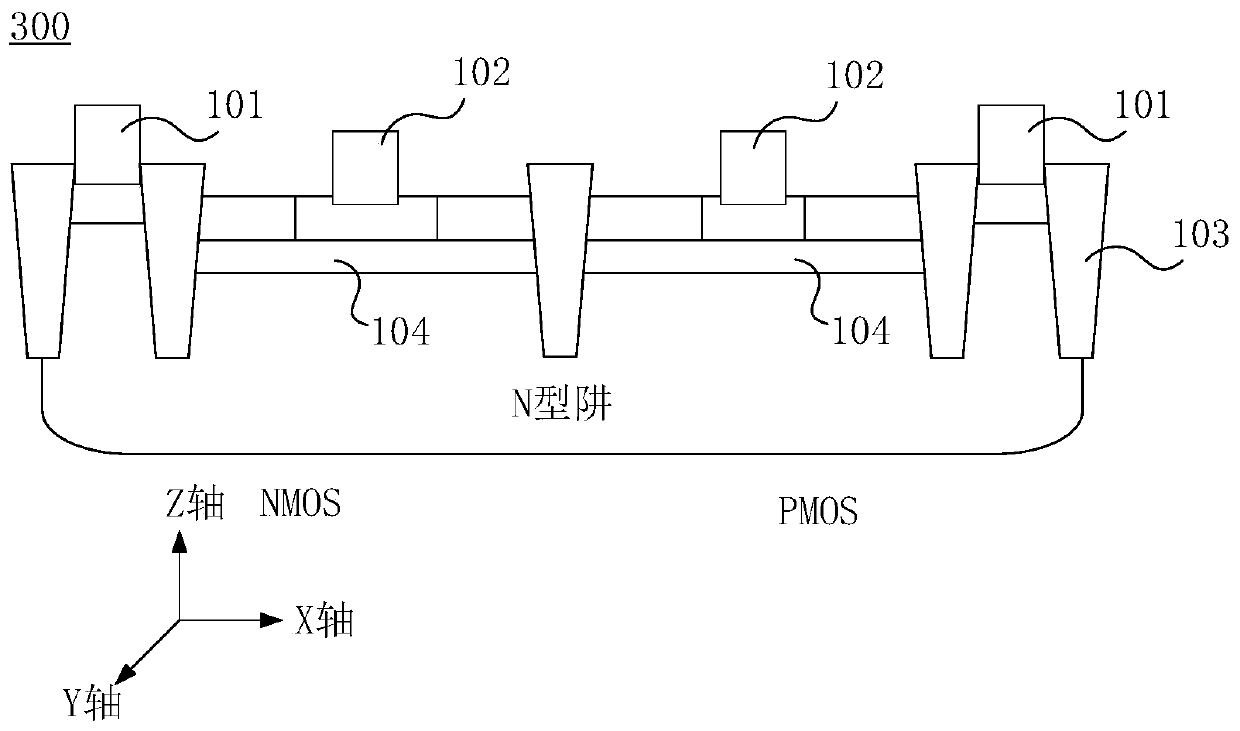

[0054] Among them, the parameters of the FDSOI standard cell include at least one of the height of the FDSOI standard cell, the N-type well (Well) edge, the well identification layer (Well-Reverse) edge, the horizontal wiring pitch and the vertical wiring pitch; the FDSOI standard cell includes RVT device, LVT device, SNW device, and SPW device at least two.

[0055] Step 602, determine the parameters of the filling unit according to the parameters of the FDSOI standard unit.

[0056] Among them, the filling unit is a structure arranged between FDSOI standard units; the parameters of the filling unit include the height of the filling unit, the N-t...

Embodiment 2

[0060] With reference to Example 1, the difference between Example 2 and Example 1 is: for "determining the parameters of the filling unit according to the parameters of the FDSOI standard unit" in step 602, it includes: determining the height of the filling unit as the height of the FDSOI standard unit .

[0061] That is, in this embodiment, the filling cell height is the same as the relative height of all FDSOI standard cells in the standard cell library, and the relative height is the height relative to the origin.

Embodiment 3

[0063] Referring to Embodiment 1 or Embodiment 2, the difference between Embodiment 3 and Embodiment 1 and Embodiment 2 is that: for "determining the parameters of the filling unit according to the parameters of the FDSOI standard unit" in step 602, it may also include: according to the FDSOI standard The N-type well edge of the cell defines the N-type well region that fills the cell.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More