Low-voltage crystal oscillator circuit compatible with GPIO

A crystal oscillator and circuit technology, applied in power oscillators, electrical components, output stability, etc., can solve problems such as failure to meet CMOSIIH leakage current specifications and insufficient isolation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

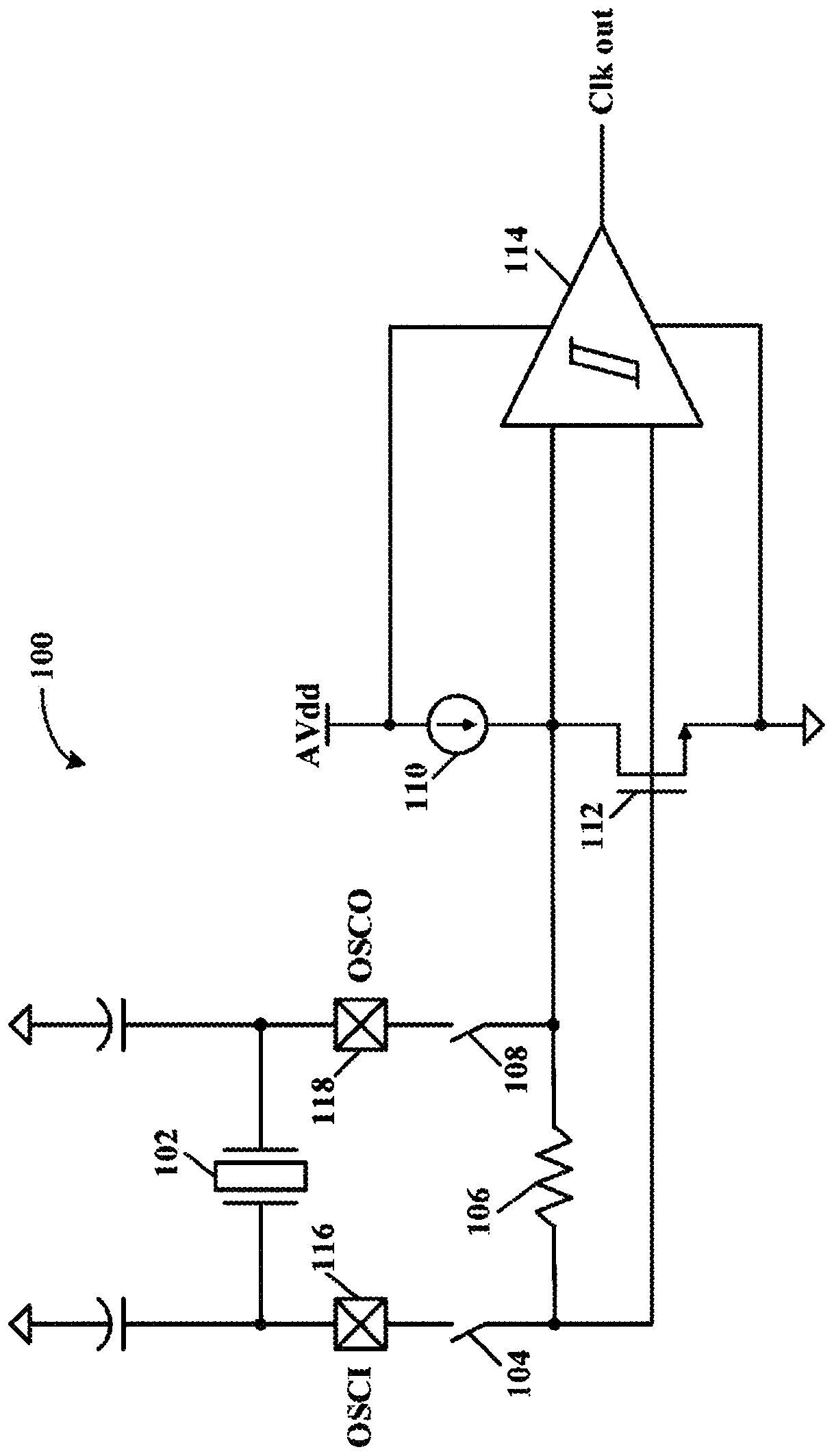

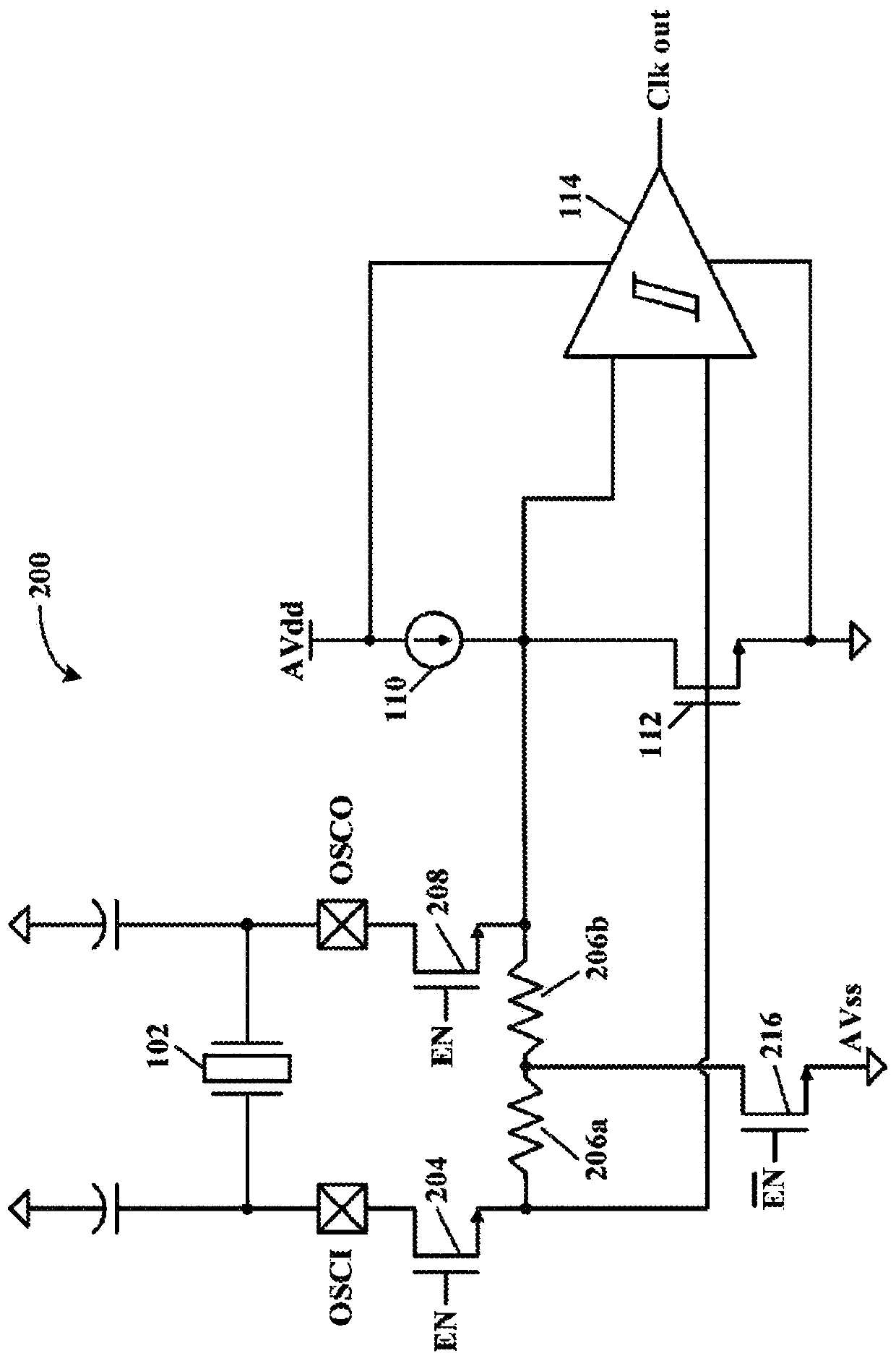

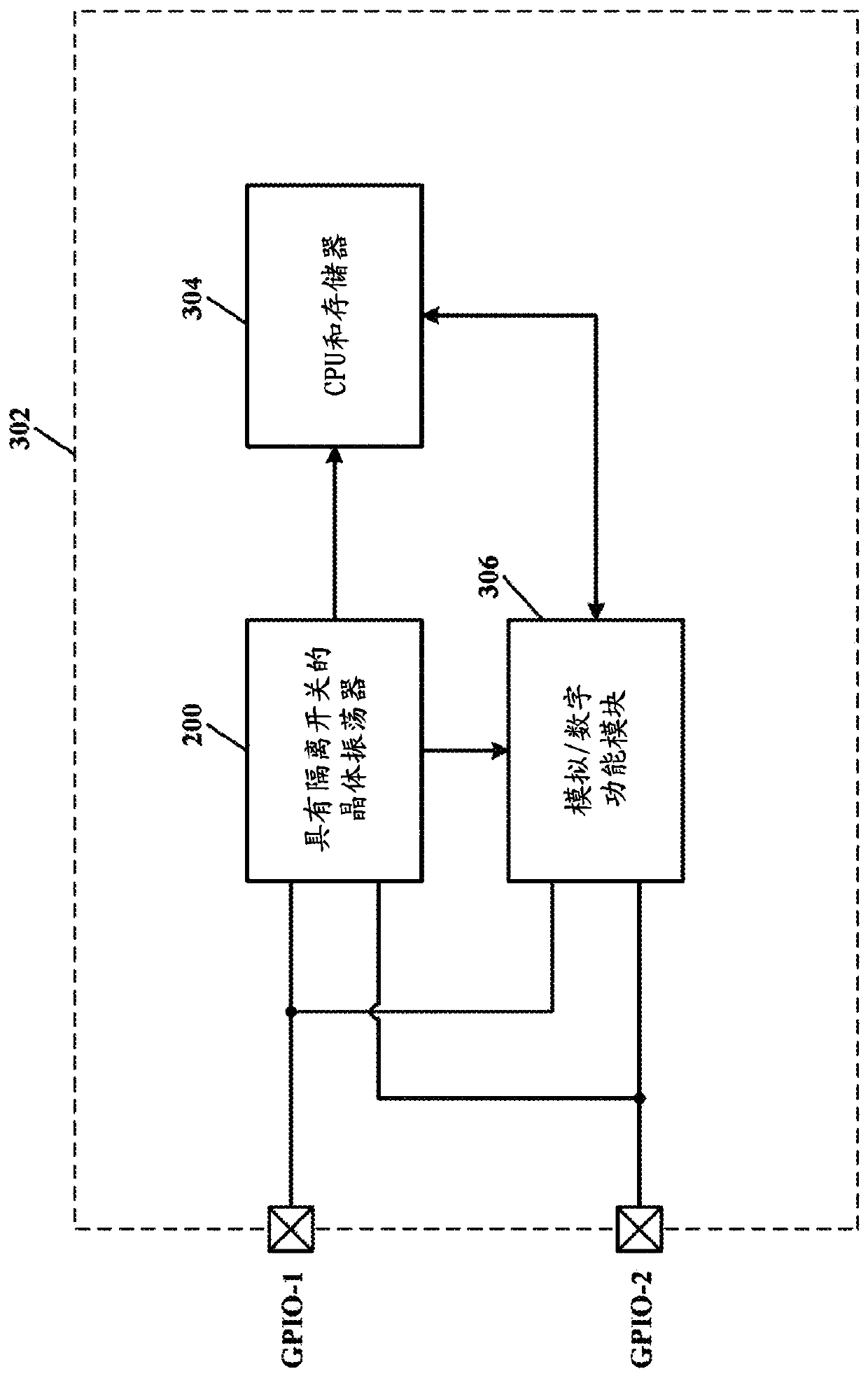

[0019] Various embodiments of the present disclosure can be configured to enable crystal oscillator functionality at a supply voltage (Vdd) that is less than a field effect transistor (FET) threshold (2-Vt). The FET threshold (2-Vt) may be the minimum gate-source voltage required to create a low resistance path between the source and drain of the FET. In some implementations, the crystal oscillator function can be enabled at Vdd less than the FET threshold. In another embodiment, the crystal oscillator function can be enabled at Vdd less than the FET threshold while maintaining the shared GPIO feature. Vdd and AVdd (analog Vdd) will be used interchangeably herein. The Gm (transconductance) of a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is the change in drain current divided by the smaller change in gate / source voltage, where the drain / source voltage is constant.

[0020] Referring now to the drawings, details of example embodiments are schematically shown. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More