Storage chip fault-tolerant device based on LDPC codes and fault-tolerant error correction method

An LDPC code and memory chip technology, which is applied in the field of memory chip fault-tolerant devices and new-type memory chip fault-tolerant devices, can solve the problems of low error correction performance of memory chips, reduced access speed, low space utilization, etc., to improve data throughput. rate and access speed, improve reliability, reduce the effect of faulty platforms

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below with reference to the drawings and embodiments.

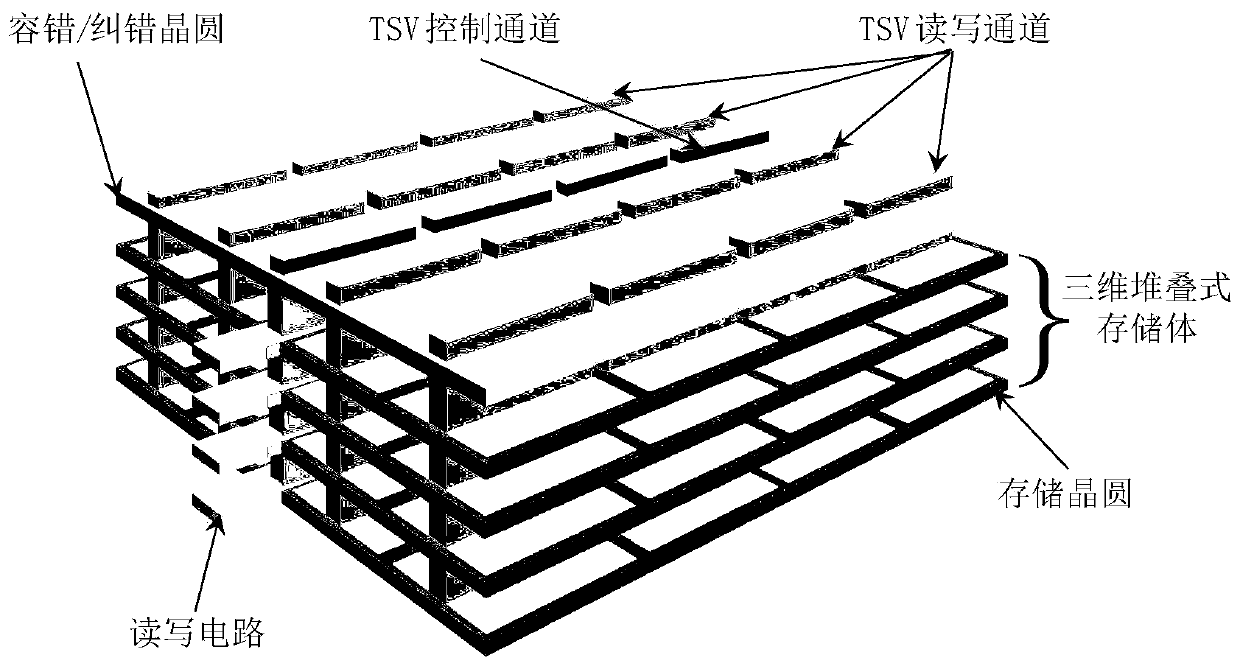

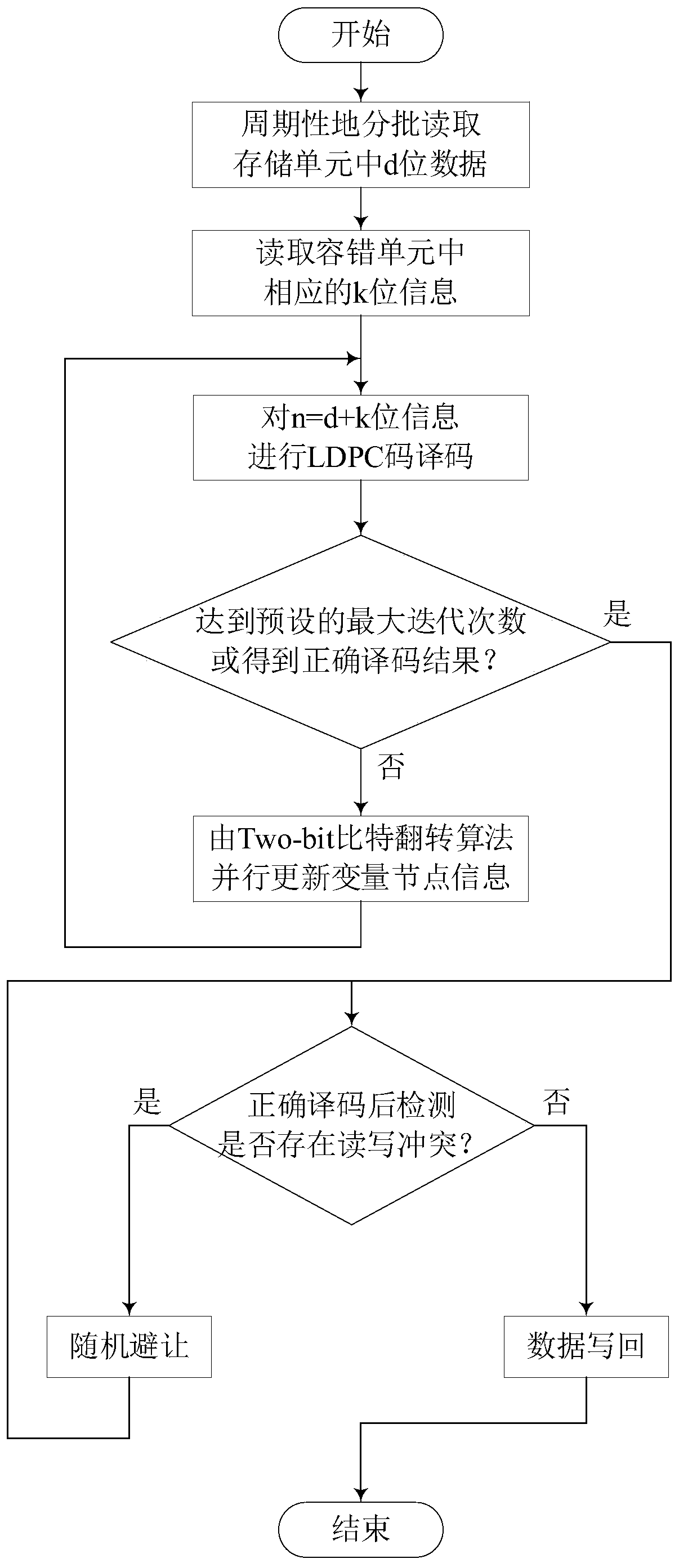

[0029] The technical idea given by the present invention is: (1) The device adopts TSV vertical vertical integration technology to form a three-dimensional stacked storage unit by using the normal data storage carrier wafer and the error correction control carrier wafer, and the error correction control wafer carries the fault tolerance verification Data and error correction control unit, and share the address, data and control bus of the normal data storage bank; (2) The method is that the error correction controller regularly reads normal data and error-tolerant data, and performs Two-bit bit flip translation based on LDPC code If the decoding is successful, the error correction data write-back operation will be performed, otherwise the decoding will end; (3) Read and write conflict detection will be performed, and if there is no conflict, the correct data after er...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More