Preparation method of bonding mark, wafer bonding method, bonding mark and semiconductor device

A wafer bonding and marking technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as bonding void risks, and achieve the effect of improving bonding quality and identification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

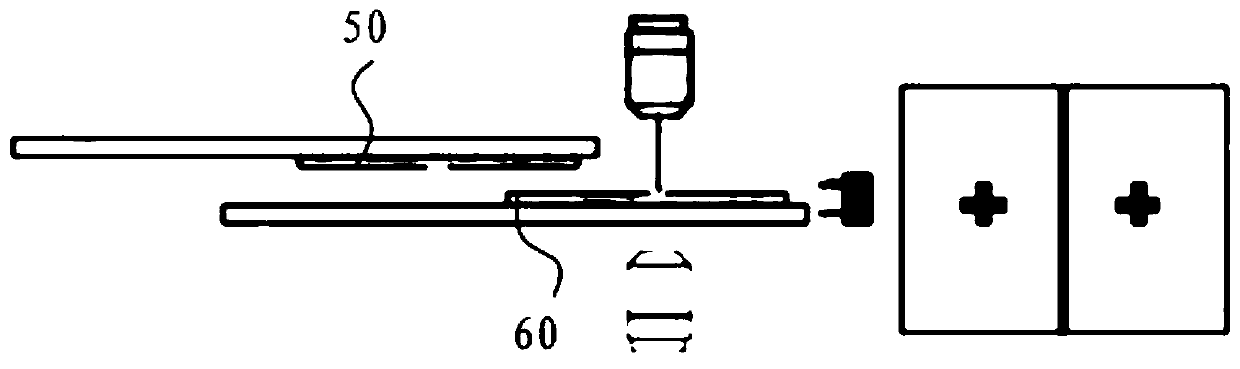

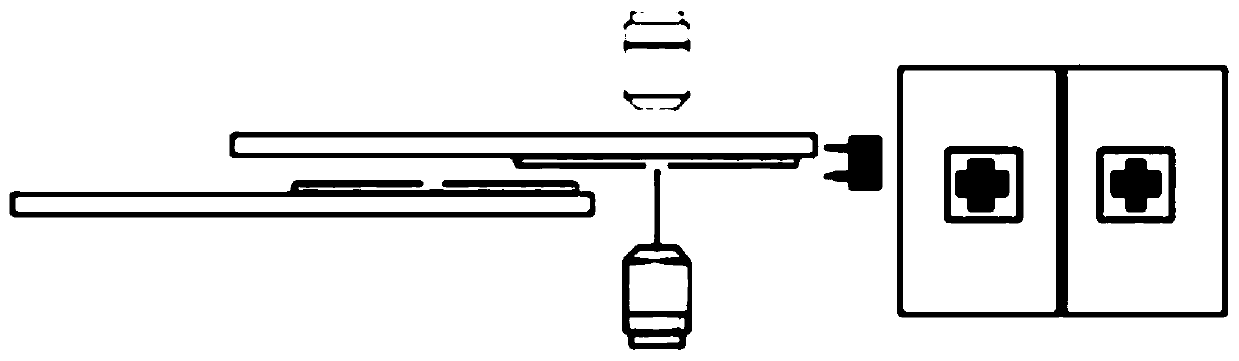

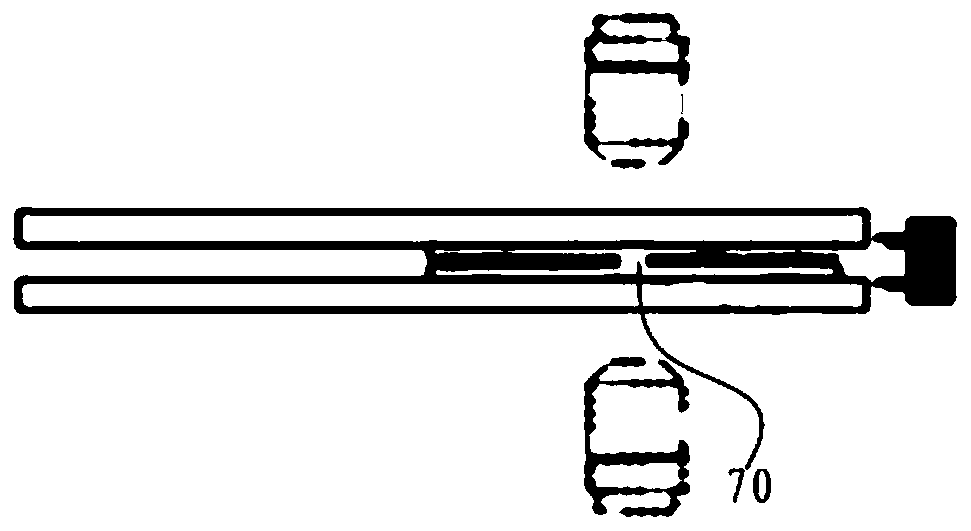

[0039] Figures 1A-1C For the process of wafer bonding alignment, first use the upper target to locate the position of the mark on the lower wafer 60 (i.e. the device wafer), digitally image and save the position; then use the lower target to adjust the upper wafer 50 (i.e. the carrier wafer) and digitally image it; finally restore the position of the lower wafer 60 and contact the upper wafer 50 to form overlay alignment marks 70 .

[0040] The process flow of wafer bonding is as follows: figure 2 with 3 As shown, first, a dry etching process is used on the carrier wafer (ie, the upper wafer) to etch a groove with a depth of 100nm as a bonding mark (ie, the upper wafer is used for bonding alignment and alignment testing. alignment marks). The carrier wafer is preferably a silicon wafer, and may include a silicon substrate 20 and a pad oxide layer 10 thereon, that is, a trench with a depth of 100 nm is etched on the pad oxide layer 10 and the silicon substrate 20 by dry etc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More