Integrated circuit memory and preparation method thereof

An integrated circuit and memory technology, applied in the field of integrated circuit memory and its preparation, can solve the problems of DRAM data access errors, increase coupling noise, affect component performance and reliability, etc., to improve device performance and reliability, and reduce coupling effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

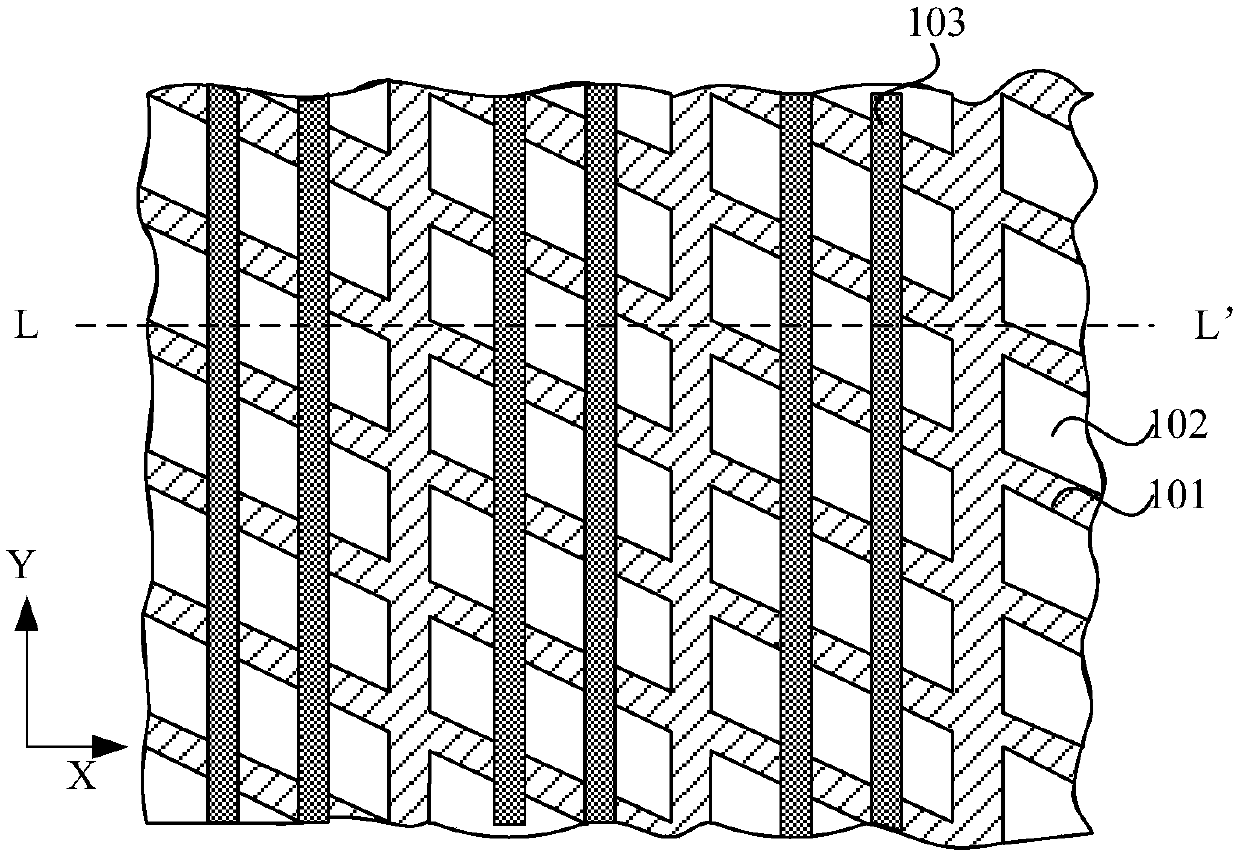

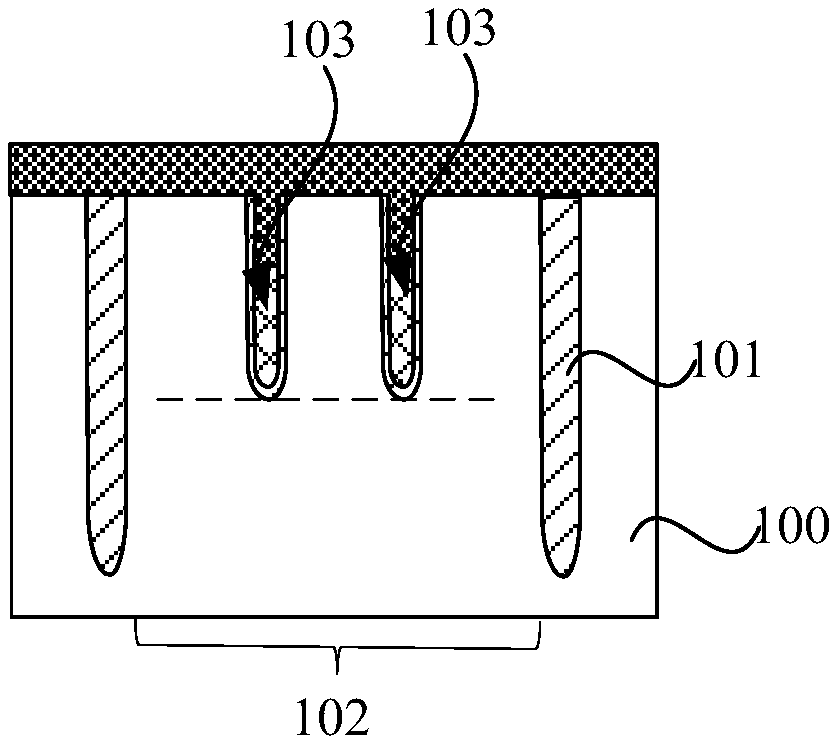

[0074] Continuing from the above, the electrical characteristics of a buried channel array transistor (BCAT) in a dynamic random access memory (DRAM) may vary depending on the depth from the upper surface of the semiconductor substrate to the bottom surface of its buried word line, for example, The magnitude of the coupling effect between two adjacent buried word lines in a dynamic random access memory (DRAM) can vary with the depth.

[0075] Based on this, the present invention provides an integrated circuit memory and a manufacturing method thereof, so that two adjacent buried word lines are arranged asymmetrically, and there is a certain height difference between the bottom surfaces of the two buried word lines The height difference is used to constrain and reduce the coupling effect between two adjacent buried word lines, thereby improving device performance and reliability.

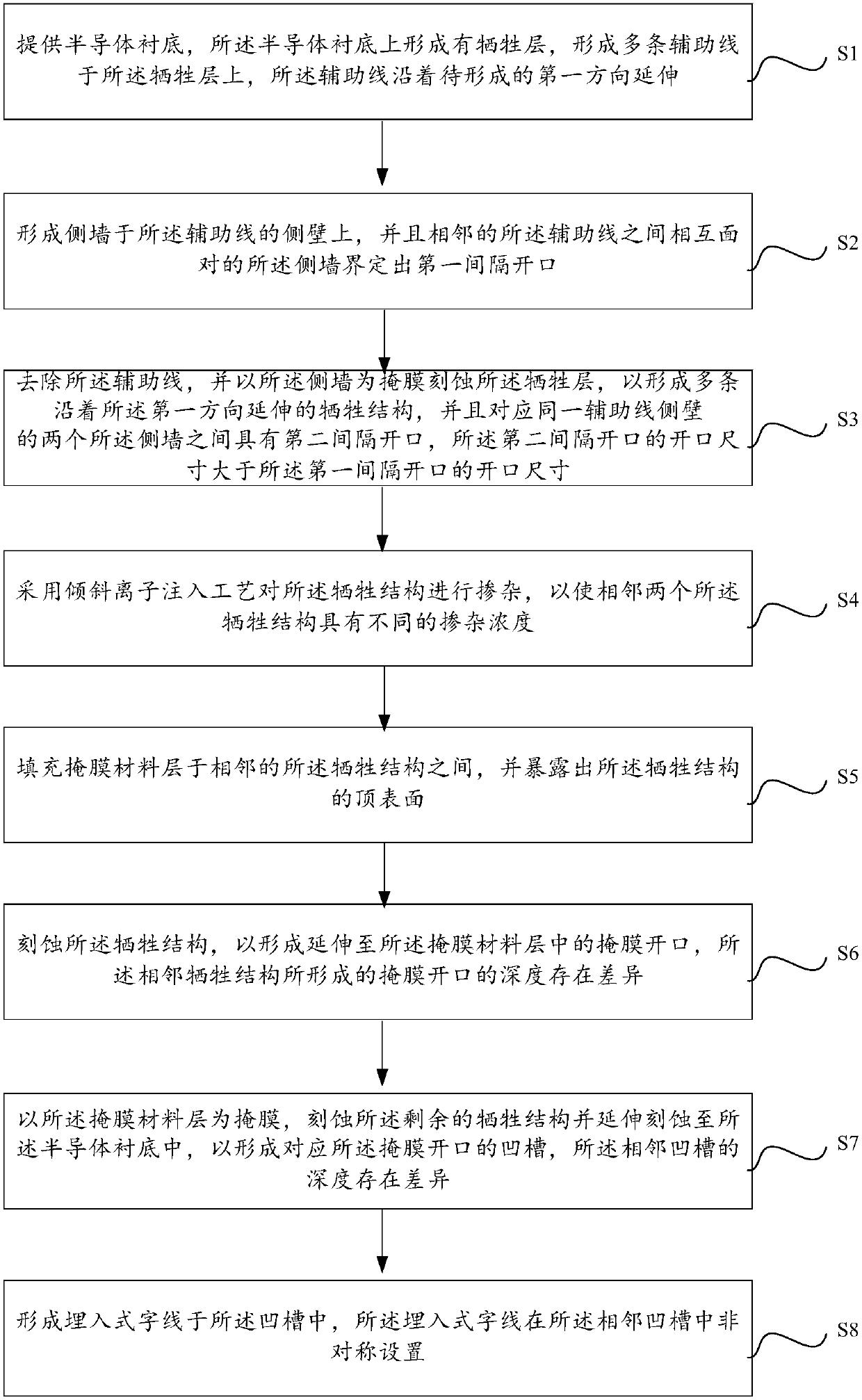

[0076] The following is attached figure 2 , Figure 3A to Figure 3H The integrated circuit mem...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com