Semiconductor interconnection structure and preparation method thereof

An interconnect structure and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as large contact resistance conductive plugs, increased conductive plug resistance, and affecting device electrical performance , to achieve the effect of increasing the contact surface, reducing the contact resistance and reducing the resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

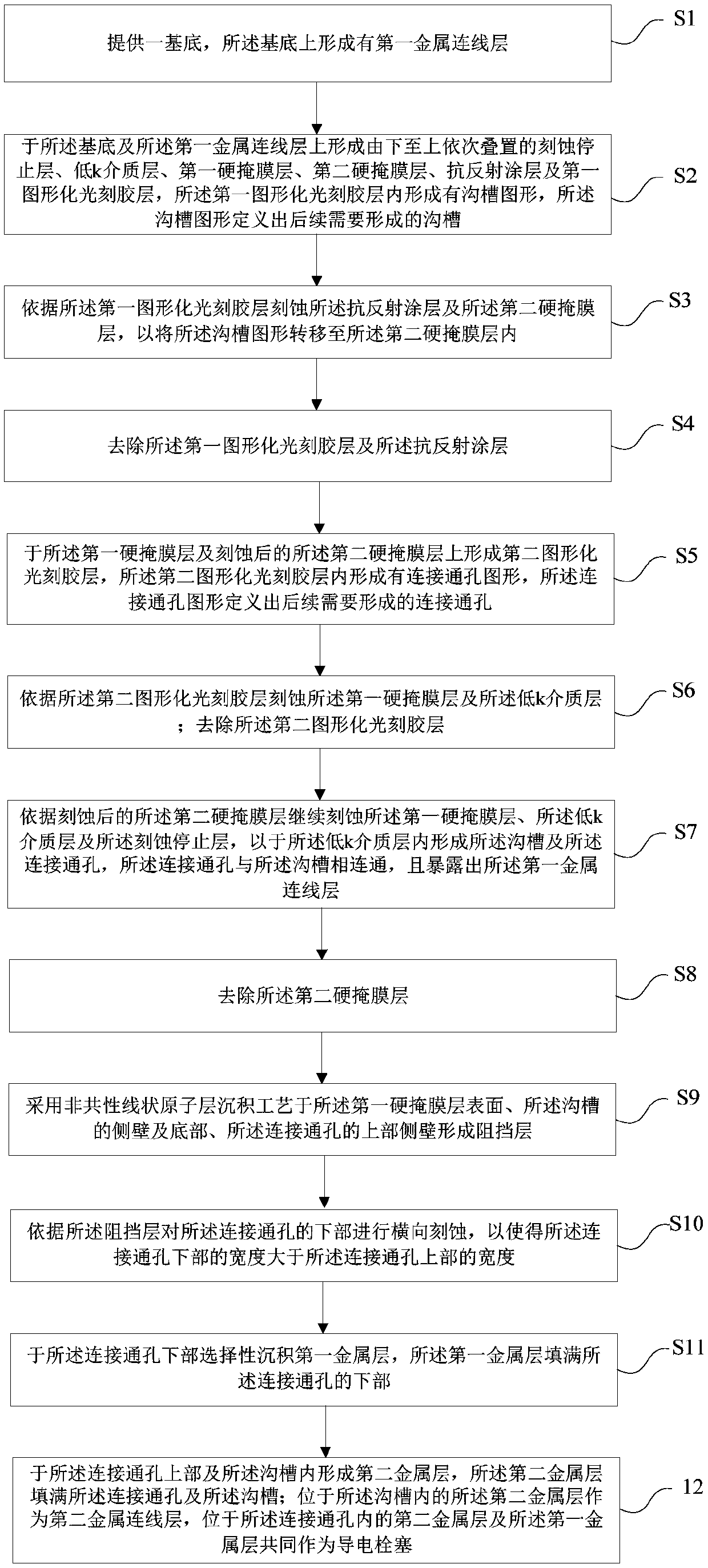

[0071] see figure 1 , the present invention provides a method for preparing a semiconductor interconnection structure, the method for preparing a semiconductor interconnection structure includes the following steps:

[0072] 1) providing a base, on which a first metal wiring layer is formed;

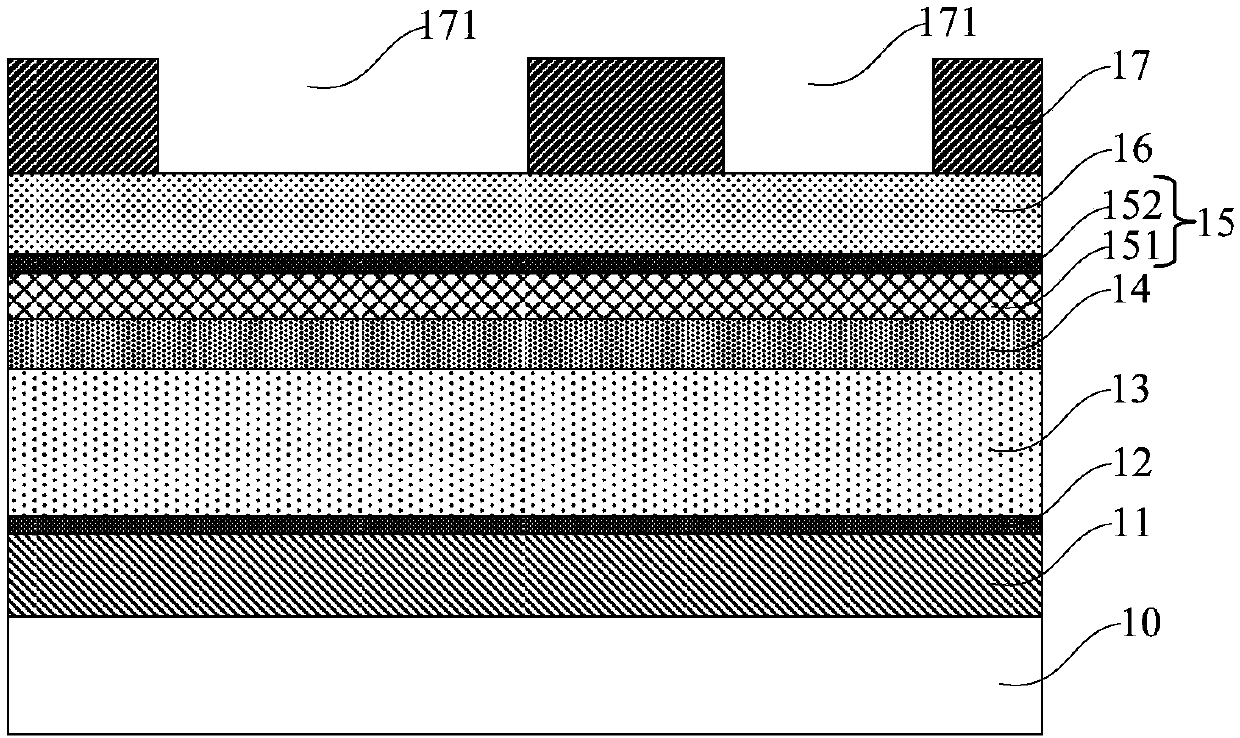

[0073] 2) Forming an etch stop layer, a low-k dielectric layer, a first hard mask layer, a second hard mask layer, an anti-reflection layer stacked sequentially from bottom to top on the base and the first metal wiring layer A coating layer and a first patterned photoresist layer, wherein groove patterns are formed in the first patterned photoresist layer, and the groove patterns define grooves to be formed subsequently;

[0074] 3) etching the anti-reflection coating and the second hard mask layer according to the first patterned photoresist layer, so as to transfer the groove pattern into the second hard mask layer;

[0075] 4) removing the first patterned photoresist layer and the a...

Embodiment 2

[0125] Please combine Figure 1 to Figure 15 refer to Figure 16 , the present invention also provides a semiconductor interconnection structure, which can be prepared by using but not limited to the preparation method described in Embodiment 1. The semiconductor interconnection structure includes:

[0126] A first metal wiring layer 11; the first metal wiring layer 11 may be formed on a substrate 10;

[0127] an etch stop layer 12, the etch stop layer 12 is located on the first metal wiring layer 11;

[0128] a low-k dielectric layer 13, the low-k dielectric layer 13 is located on the etching stop layer 12;

[0129] A conductive plug 22, the conductive plug 22 is located in the low-k dielectric layer 13 and the etching stop layer 13, the conductive plug 22 includes a first metal layer 221 and a second metal layer 222; the first metal layer The bottom of the layer 221 is in contact with the first metal wiring layer 11, and the width of the first metal layer 221 is greater t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com