Embedded processor of storage and calculation integrated chip, instruction set and data processing method

An embedded processor and instruction technology, applied in the direction of electrical digital data processing, register devices, instruments, etc., can solve the problem of no control logic circuit, unfavorable storage and calculation integrated chip development and integration, low efficiency of embedded central processor control, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] The technical solutions in the embodiments of the present invention will be described in more detail below in conjunction with the accompanying drawings in the embodiments of the present invention. It can be understood that the described embodiments are only part of the embodiments of the present invention, not all of them. Example. Based on the embodiments of the present invention, all other embodiments obtained by those skilled in the art without making creative efforts belong to the protection scope of the present invention.

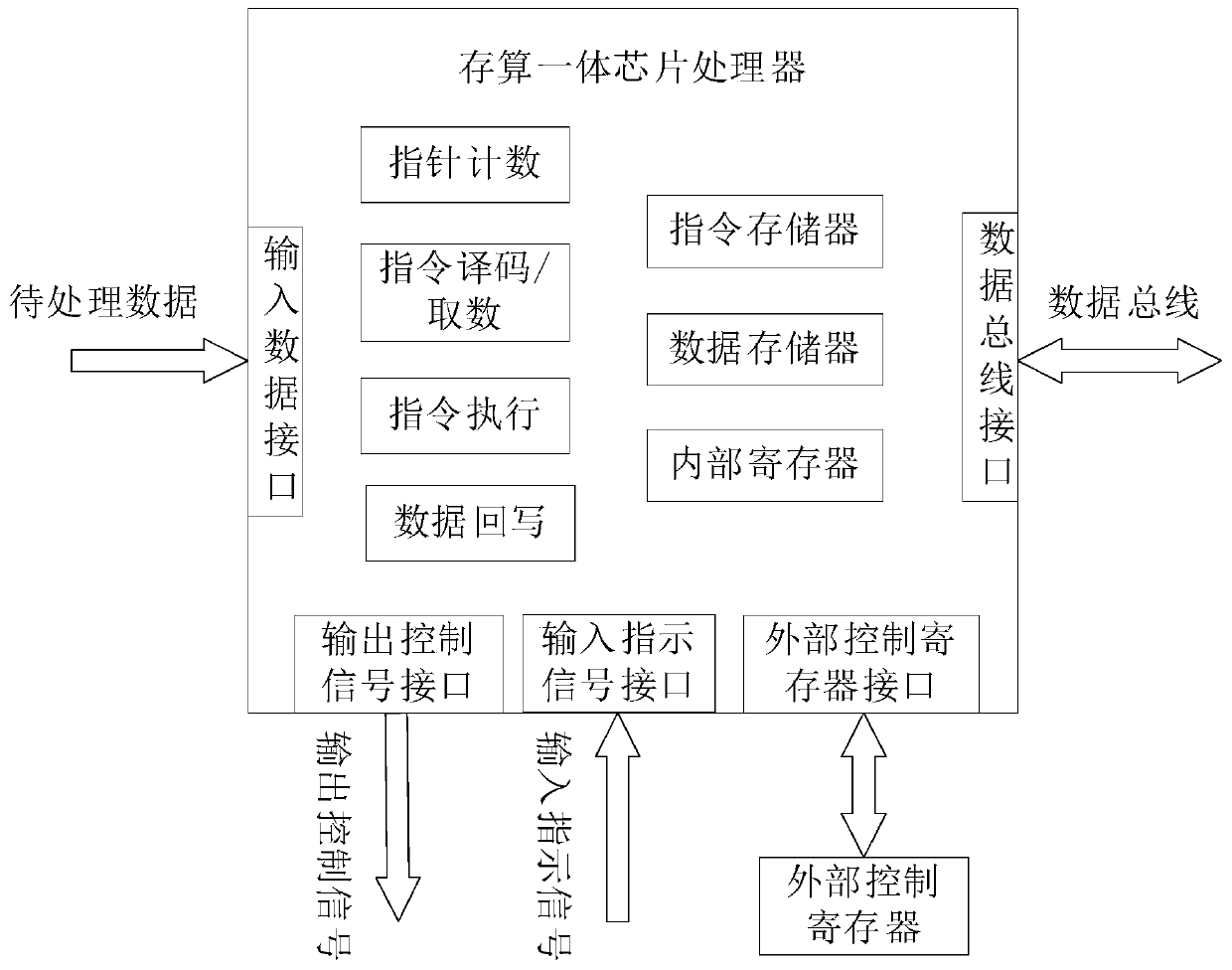

[0068] refer to figure 1 As shown, the embodiment of the present invention provides a basic architecture of an embedded processor of a memory-computing integrated chip, which is mainly divided into common internal instruction processing related parts of a general-purpose embedded processor and a special part for the application of a memory-calculating integrated chip. The relevant parts of the external interface are set, and the relevant parts...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More