Forming method of semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as increasing the difficulty of process control, reducing production efficiency, and increasing the probability of open circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The specific implementation manner of the present invention will be described in more detail below with reference to schematic diagrams. The advantages and features of the present invention will be more apparent from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

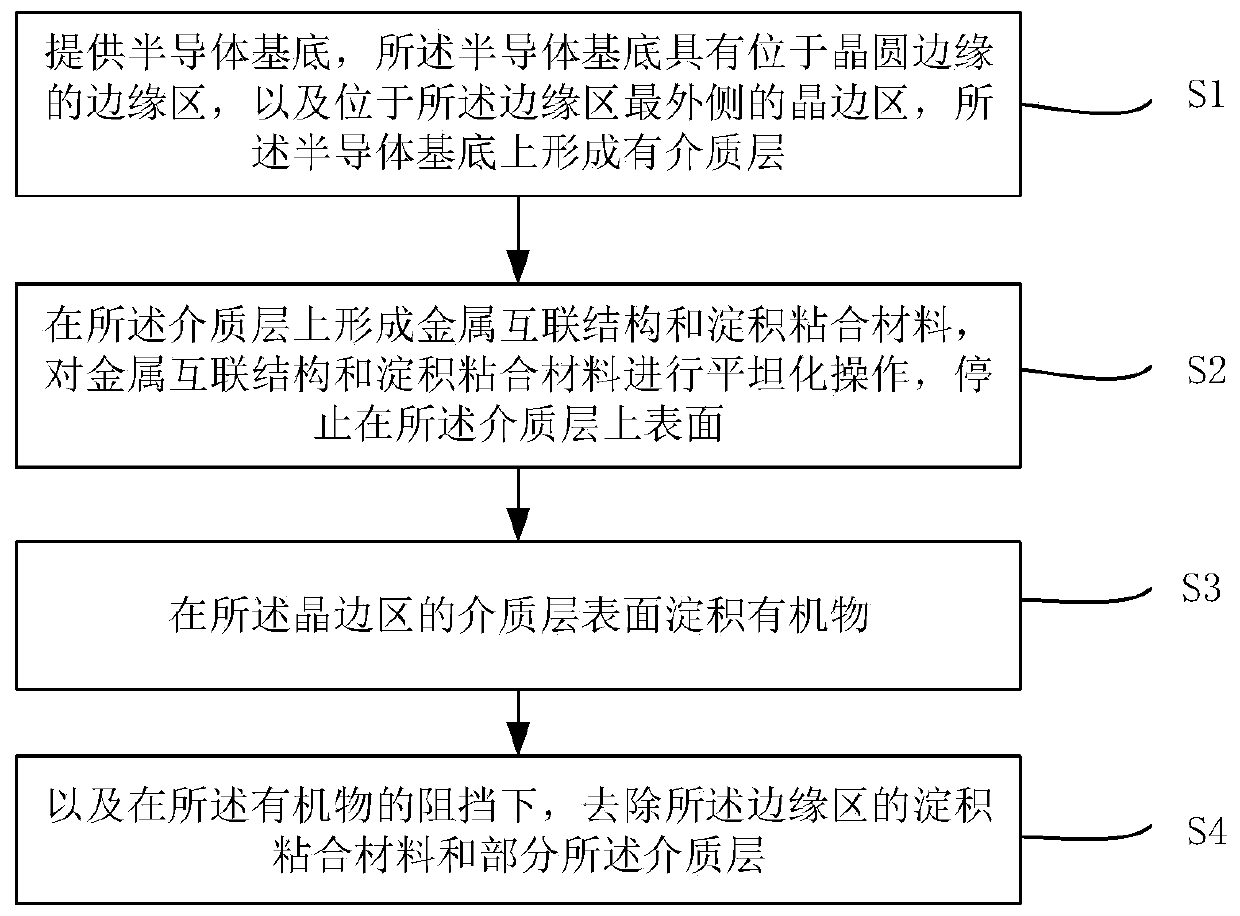

[0027] In order to increase the uniformity of film thickness in the edge region of the interlayer dielectric layer, the invention provides a method for forming a semiconductor device. figure 2 A process flow chart of a method for forming a semiconductor device provided by an embodiment of the present invention. Such as figure 2 As shown, the method for forming a semiconductor device according to the embodiment of the present invention includes the following steps:

[0028] Step S1: providing a semiconductor su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com