Semiconductor structure and forming method thereof

A semiconductor and dummy gate technology, applied in the field of semiconductor structures and their formation, can solve problems such as poor performance of semiconductor structures and occupy space, and achieve the effects of solving the problem of etching residues, saving lateral space, and large process space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be seen from the background art that the devices formed so far still have the problem of poor performance. Combining with a method of forming a semiconductor structure, the reason for the poor performance of the device is analyzed.

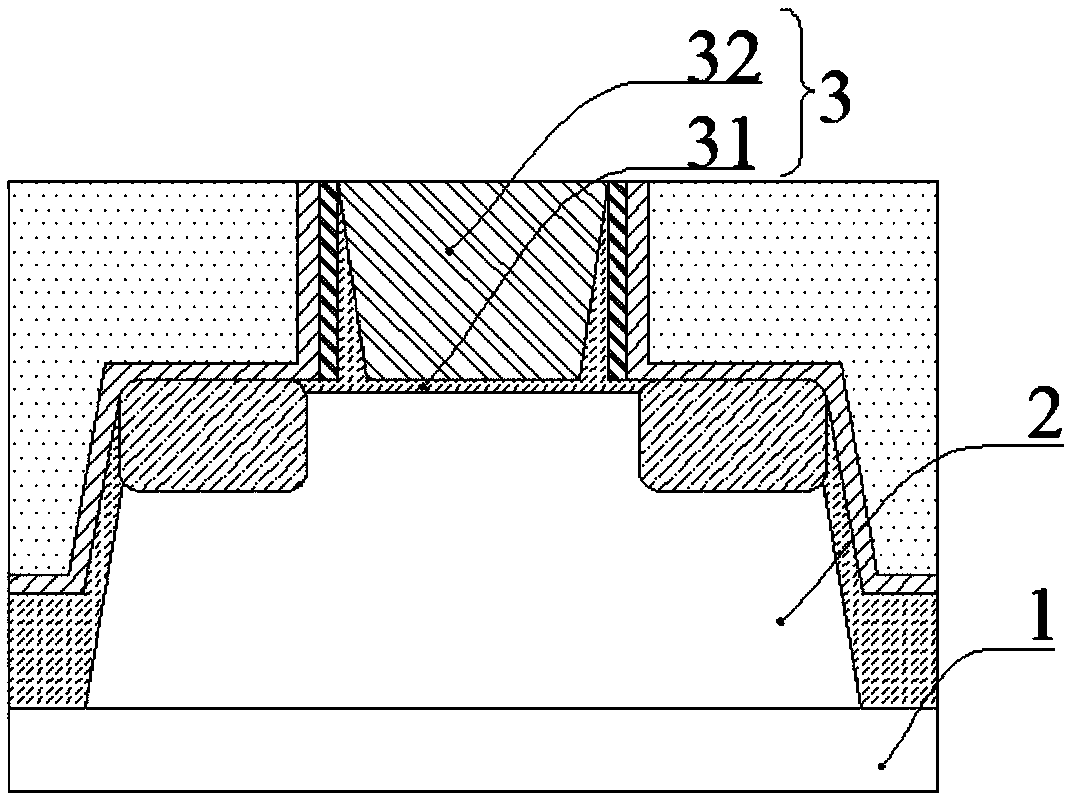

[0033] Reference 1 shows a schematic structural diagram corresponding to a method for forming a semiconductor structure.

[0034] refer to figure 1 , providing a base, the base includes a substrate 1, a discrete fin 2 protruding from the substrate 1, and a dummy gate structure 3 across the fin 2, the dummy gate structure 3 covers the fin Part of the top wall and part of the side wall of part 2.

[0035] The dummy gate structure 3 includes a dummy gate oxide layer 31 conformally covering part of the top wall and sidewall of the fin, and a dummy gate layer 32 located on the dummy gate oxide layer 31 . In the dummy gate layer 32, the length perpendicular to the sidewall direction of the dummy gate structure 3 is taken as the width, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More