Network-on-chip topological structure and implementation method thereof

An on-chip network and topology technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as physical design and back-end implementation difficulties, large switching matrix scale, hardware resource expansion, etc. Optimize, ensure PPA, ensure the effect of normal work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The implementation mode of the present invention is illustrated by specific specific examples below, and those who are familiar with this technology can easily understand other advantages and effects of the present invention from the contents disclosed in this description. Obviously, the described embodiments are a part of the present invention. , but not all examples. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

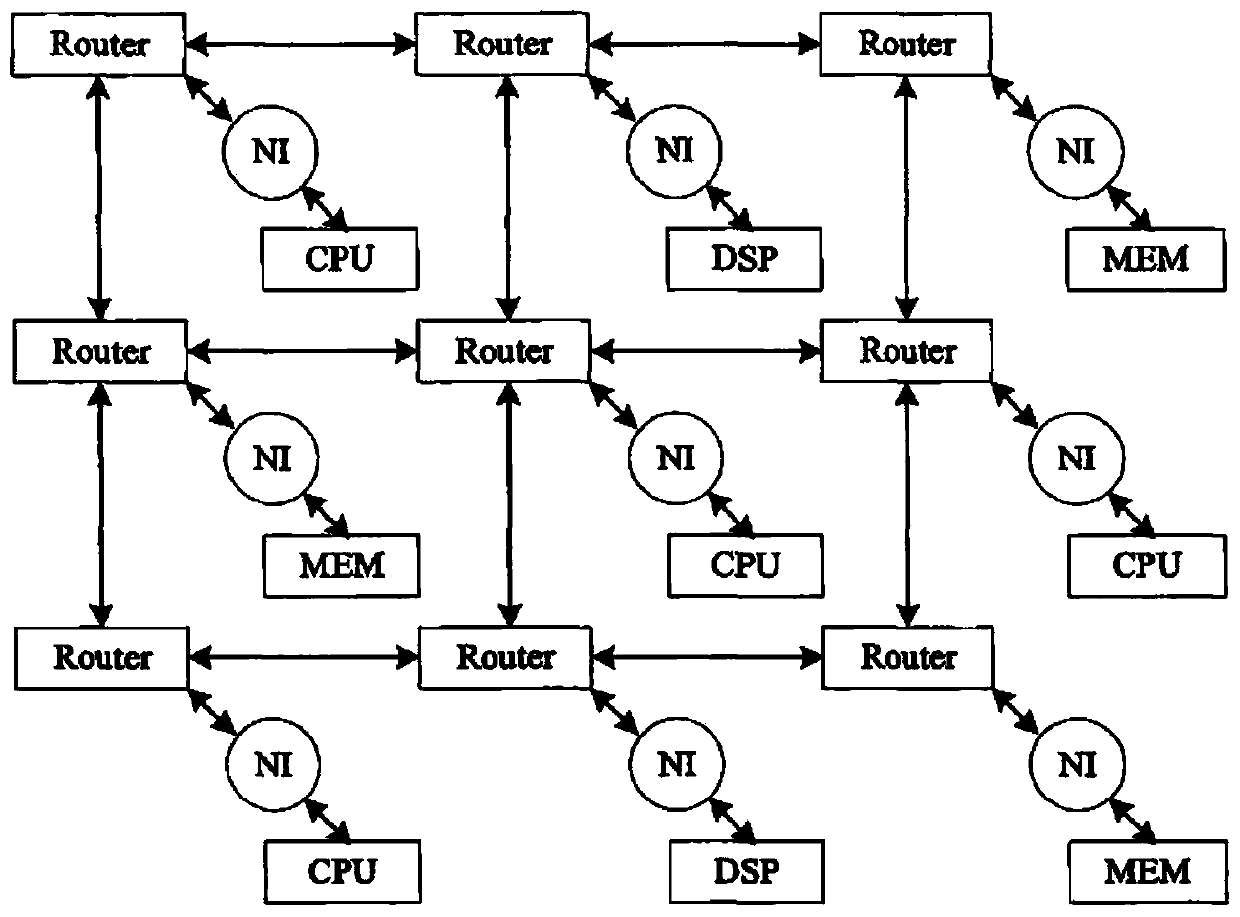

[0031] Although the traditional Mesh topology has the advantages of good scalability, regularity, simple structure, and easy implementation, such as figure 1As shown, due to the symmetry of the structure and the relative occlusion of edge nodes, the traditional Mesh structure tends to cause unbalanced load distribution and the formation of hotspots in the central area, resulting in network conges...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More