DSP processor, system and external storage space access method

An external memory and processor technology, applied in memory systems, memory architecture access/allocation, electrical digital data processing, etc., can solve problems such as low efficiency of DSP systems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

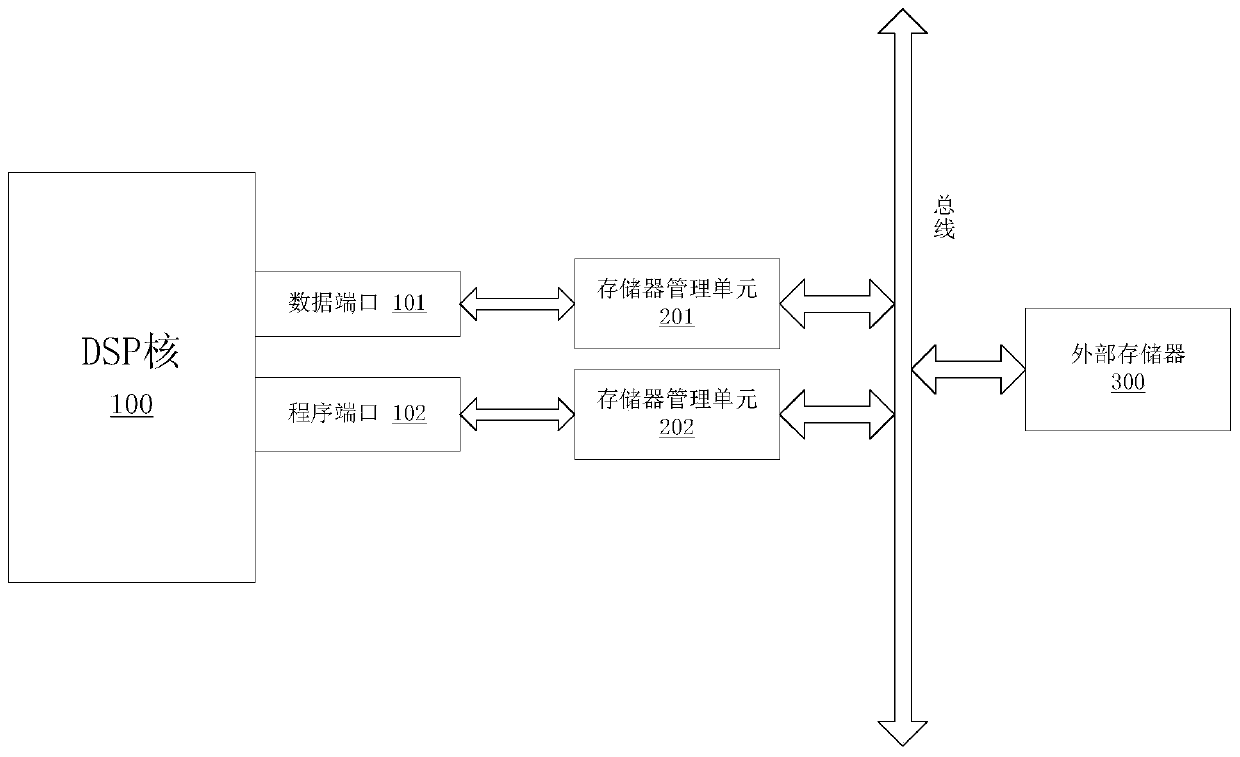

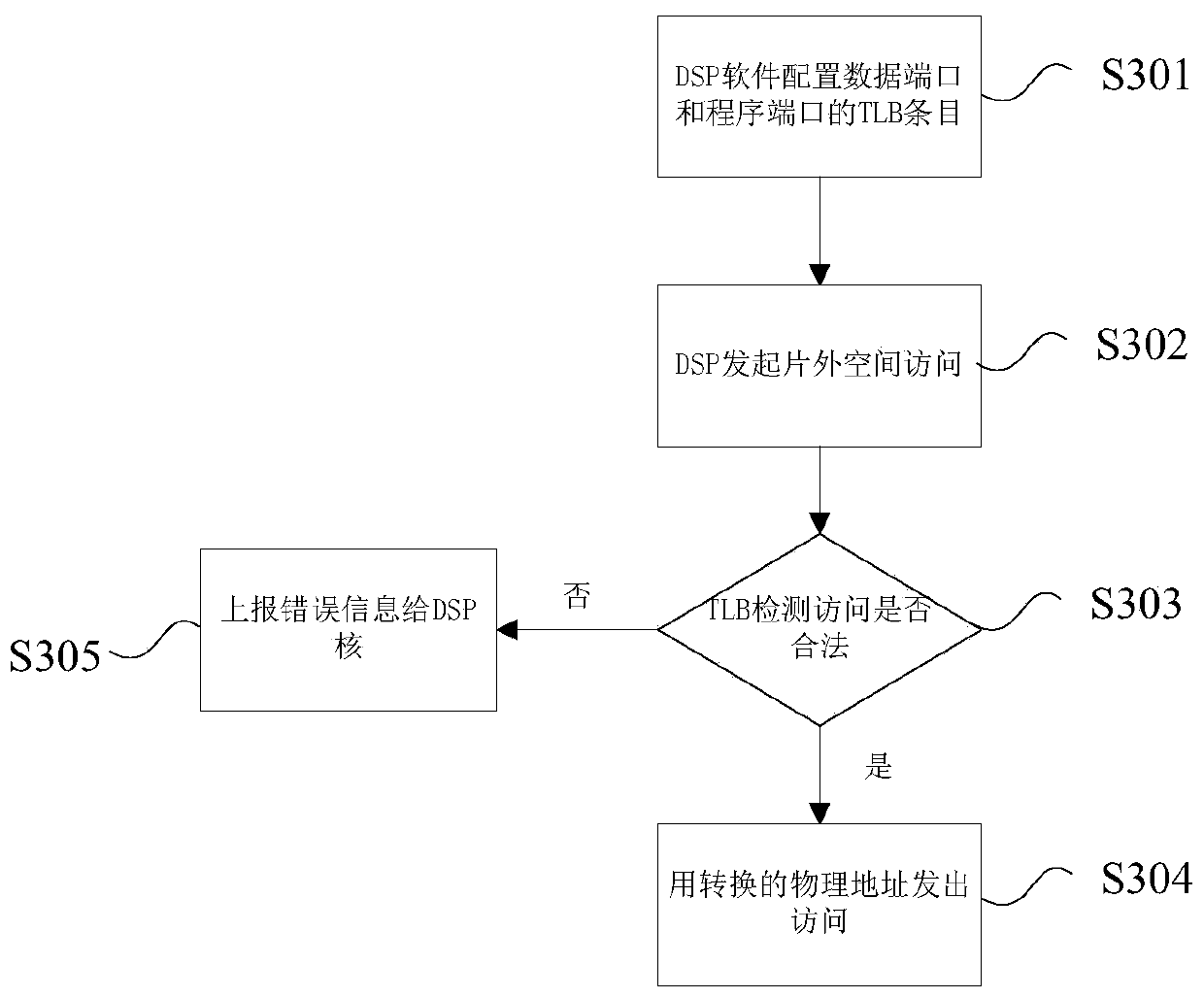

[0048] Such as Figure 4 As shown, in this embodiment, the DSP system includes multiple DSP cores, and each DSP core has multiple program ports and data ports for accessing off-chip memory space, where each program port and data port is configured There is a TLB unit.

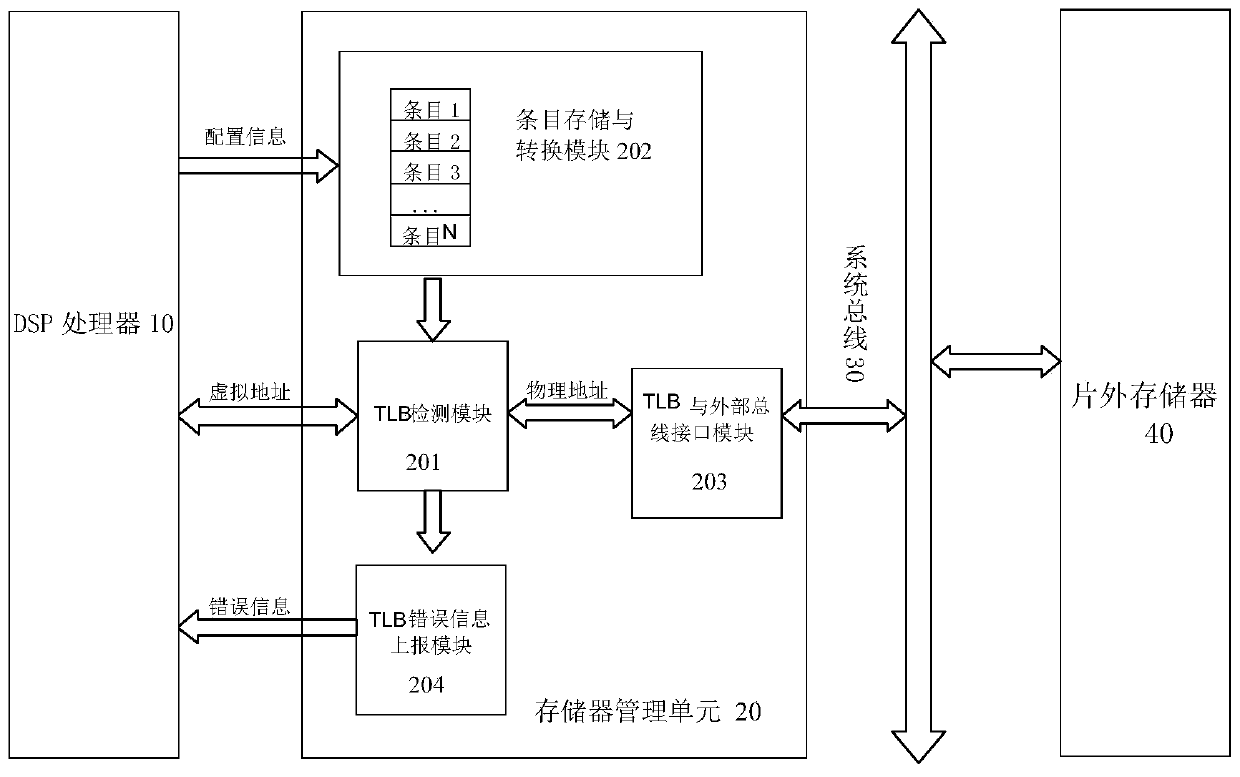

[0049] The entry table of the TLB unit can be configured through software before the DSP core accesses the off-chip memory. Configuration items can include virtual addresses and corresponding physical addresses, access length, memory access permissions, etc. It can also set the readable, writable, and valid attributes of a certain address.

[0050] When the DSP core issues an access, the TLB unit detection module parses out the address signal, which is a virtual address for the TLB unit.

[0051] The TLB unit queries whether the virtual address is within a certain entry range of the entry table, if it hits, it is translated into a physical address, and the access is issued through the interface between the TLB unit ...

Embodiment 2

[0053] Such as Figure 5 As shown, in this embodiment, when some ports do not require address translation, the TLB unit can be set to a bypass mode (bypass).

[0054] First, according to actual needs, set certain port TLB units to bypass mode (the LTB unit shown by the dotted line in the figure).

[0055] The software configures the entry table of each port TLB unit before the DSP core accesses the off-chip space. The configuration items include virtual addresses and corresponding physical addresses, access lengths, memory access permissions, etc.

[0056] When the DSP core issues an access (each data port and program port can issue access requests in parallel), the TLB detection unit parses out the address signal, which is a virtual address for the TLB unit.

[0057] The TLB unit queries whether the virtual address is within an entry range of the entry table, and if it hits, it is converted into a physical address, and an access is issued through the interface between the TLB unit and...

Embodiment 3

[0059] Such as Image 6 As shown, in this embodiment, the DSP processor has multiple data ports, and the bus bit width of each data port is different. Some data ports are connected to low-speed storage. For example, DDR memory, Flash memory, or L3 memory, etc. Some data ports are connected to high-speed memory, such as L2 cache. The TLB unit can be set to adapt to different bit widths.

[0060] The software configures the entry table of each port TLB unit before the DSP core accesses each memory. The configuration items include virtual addresses and corresponding physical addresses, access lengths, memory access permissions, etc.

[0061] When the DSP core issues an access (each data port and program port can issue access requests in parallel), the TLB detection unit parses out the address signal, which is a virtual address for the TLB unit.

[0062] The TLB unit queries whether the virtual address is within an entry range of the entry table, and if it hits, it is converted to the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com