High-performance approximate full adder gate-level unit

A full adder, high-performance technology, applied in the field of high-performance approximate full adder gate-level units, can solve the problems of large area occupied by hardware circuits, large power consumption, etc., and achieve fast speed, low power consumption, and small area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

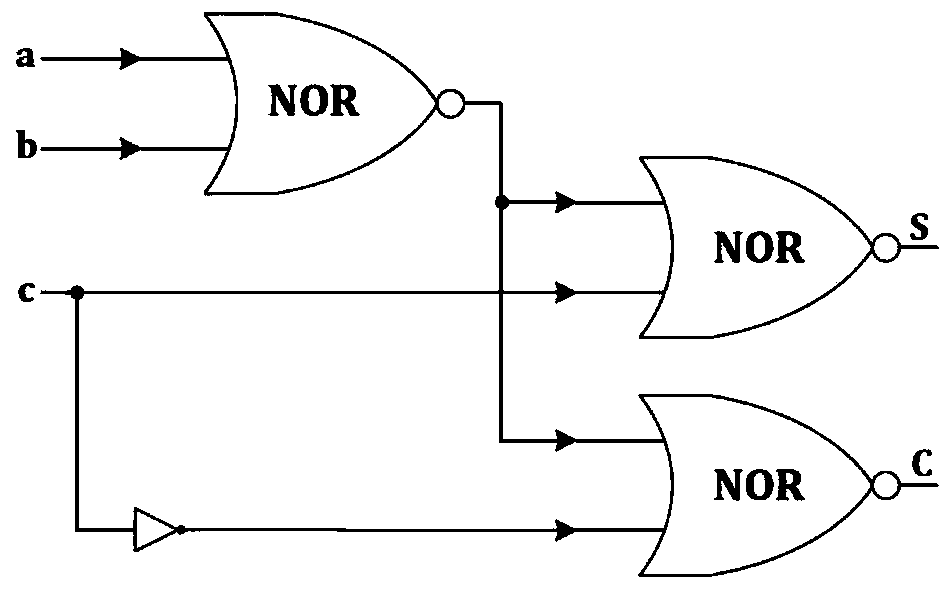

[0019] Example: such as figure 1 Shown is the structural diagram of the high-performance approximate full adder gate-level unit of the present invention, comprising: the first NOR gate, the second NOR gate, the third NOR gate and the NOT gate; the first NOR gate of the first NOR gate One input end is the addend input end, the second input end is the summand input end, the output end connects the first input end of the second NOR gate and the first input end of the third NOR gate; the second NOR gate The second input terminal of is the low carry input terminal, and the low carry input terminal is connected with the high carry output terminal of the previous gate level unit in the approximate full adder constituted by the gate level unit, the second NOR gate The output end of the NOR gate is the sum output end of this gate-level unit; the second input end of the second NOR gate is also connected with the input end of the NOR gate, and the output end of the NOR gate is connected ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More