Display panel, display device and pixel driving method

A display panel and pixel technology, applied in static indicators, instruments, etc., can solve problems such as affecting the screen display effect, increasing the power consumption of light-emitting diodes, and OLED current instability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

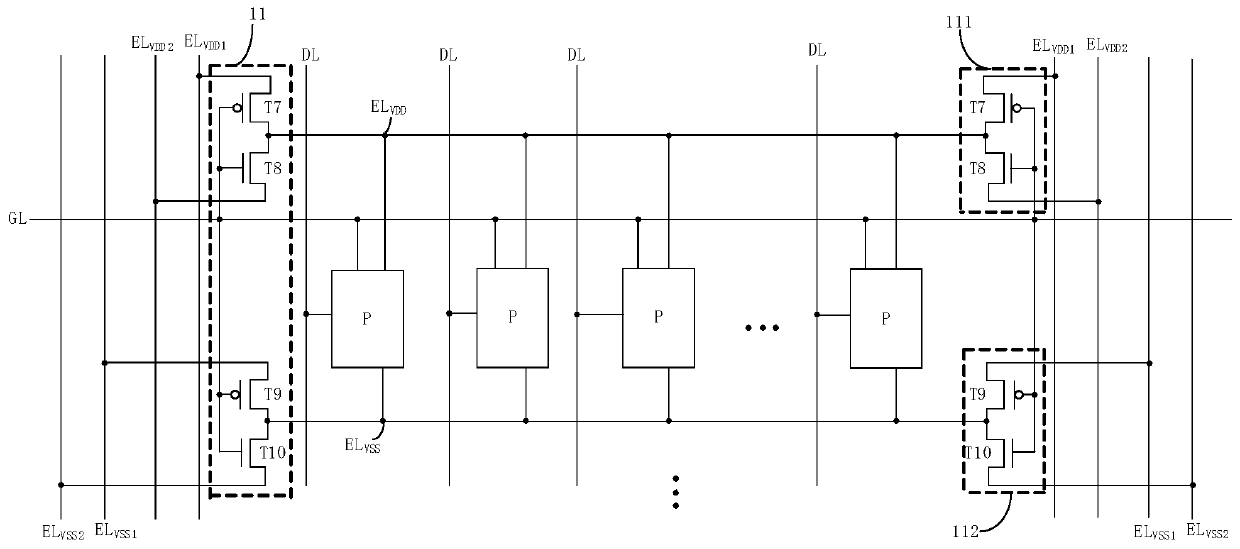

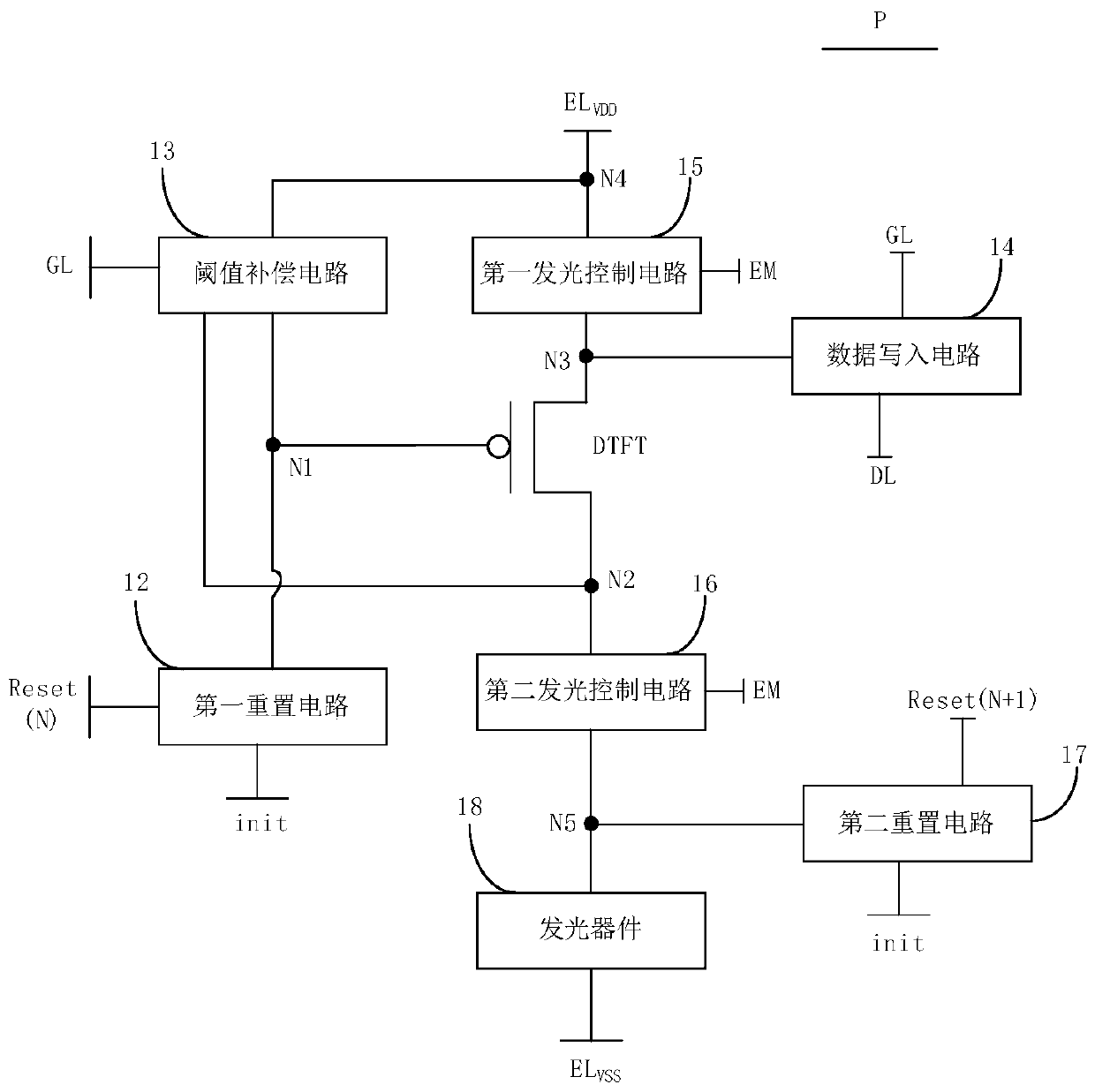

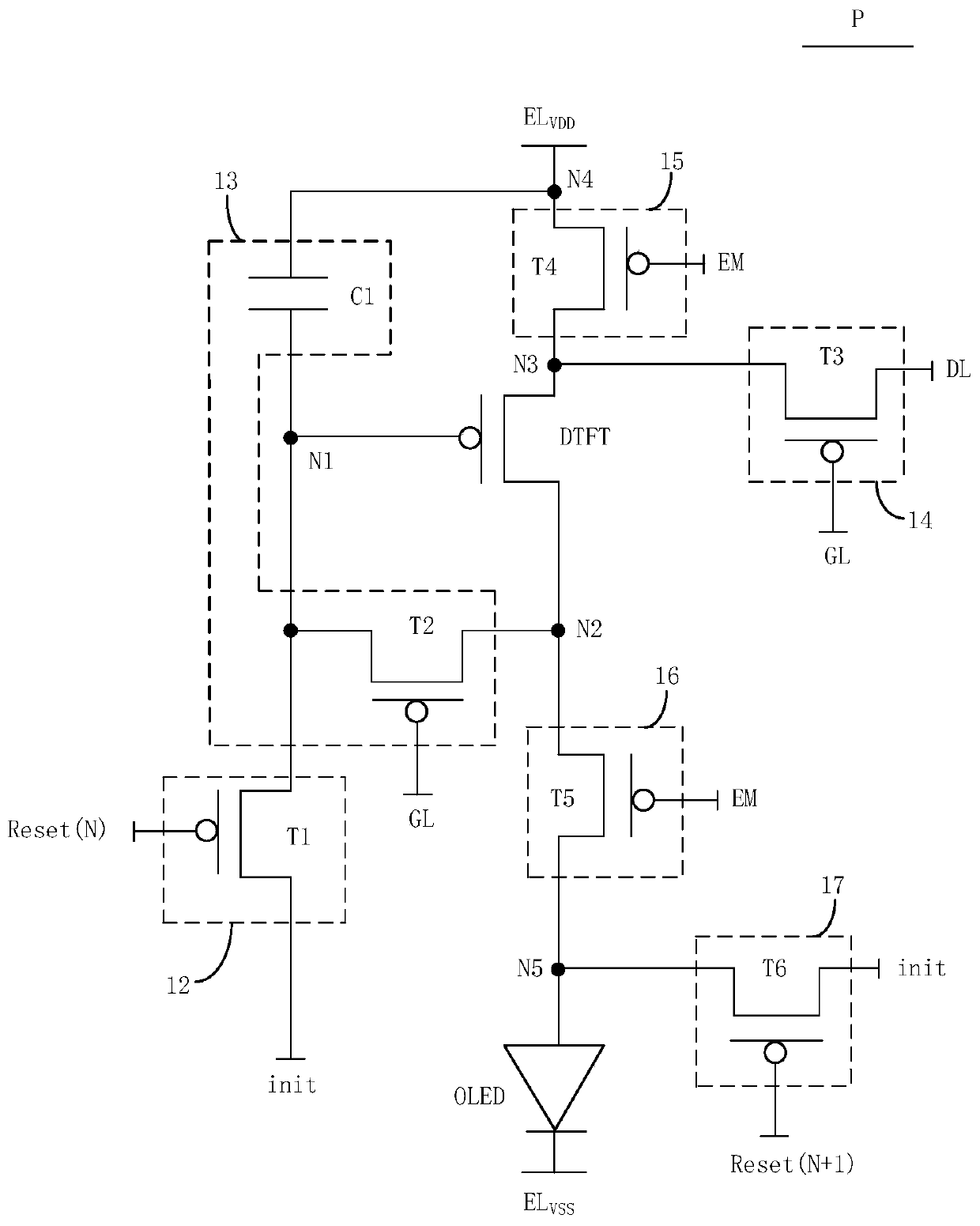

[0042] In order for those skilled in the art to better understand the technical solutions of the embodiments of the present disclosure, the technical solutions of the display panel, the display device, and the pixel driving method provided by the embodiments of the present disclosure will be clarified below in conjunction with the drawings of the embodiments of the present disclosure , fully describe.

[0043] Example embodiments will be described more fully hereinafter with reference to the accompanying drawings, but may be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the disclosure to those skilled in the art.

[0044] The terminology used herein is for describing particular embodiments only and is not intended to limit the present disclosure. As used herein, the singular forms "a" and "th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More