Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of difficulty in controlling the filling rate of the top interconnect layer, failure of metal interconnection of stacked wafers, and mutual Interruption of layer growth, etc., to achieve the effect of ensuring insulation, increasing area, and increasing filling rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

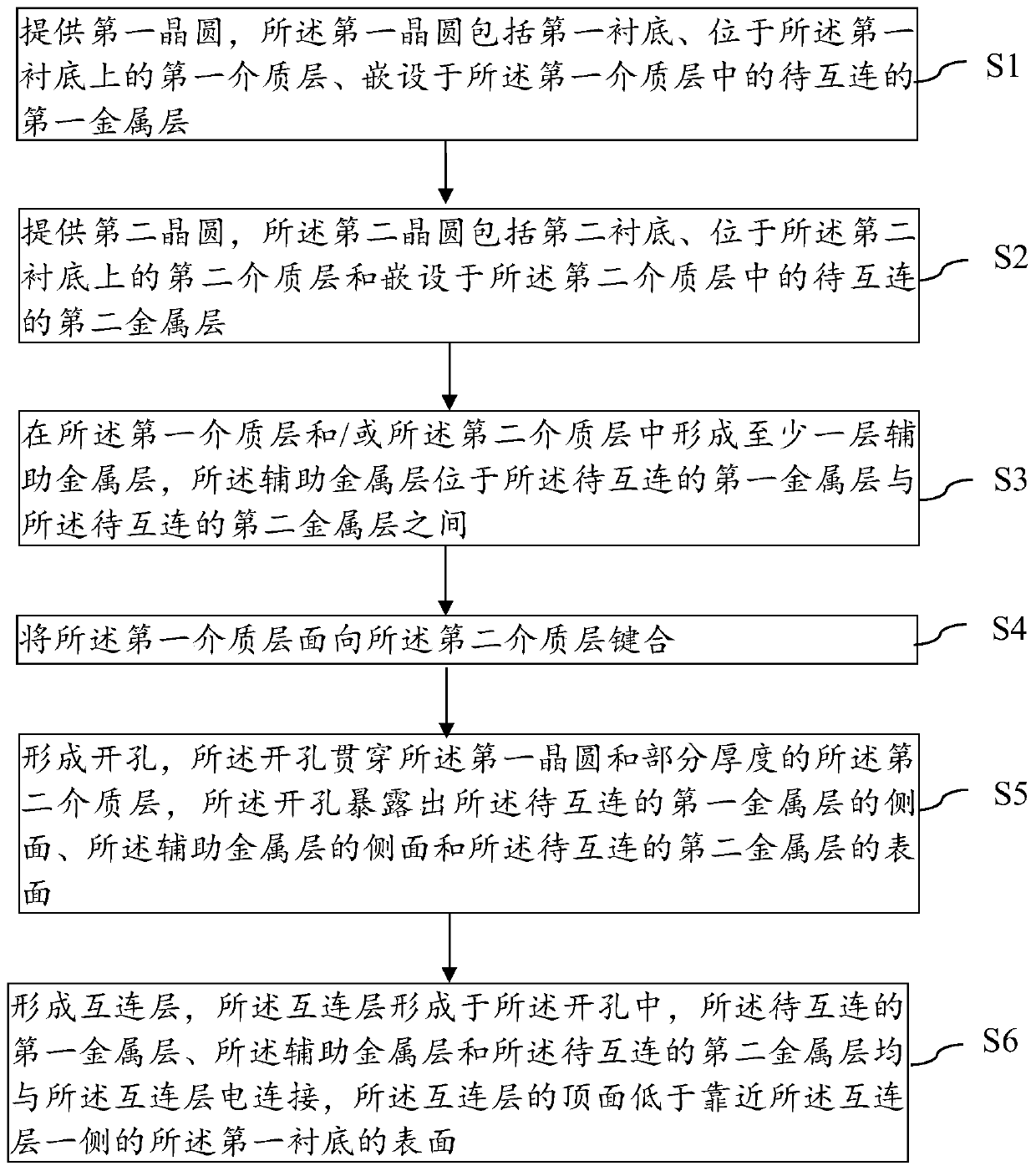

Method used

Image

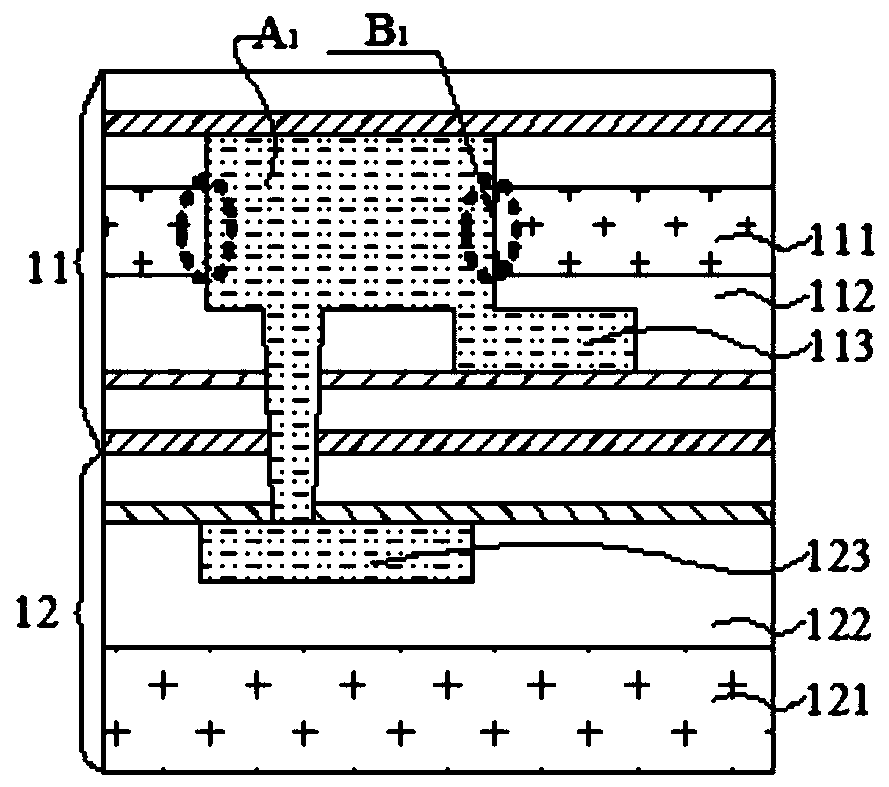

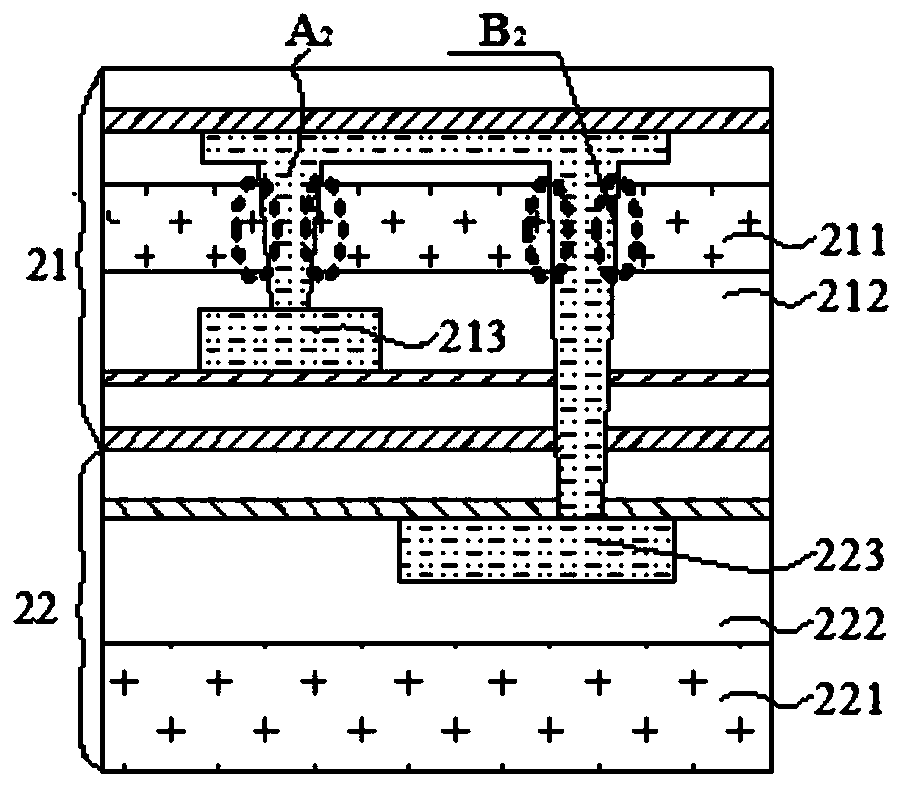

Examples

example 2 ,( example pic 8a),( example 316b and 316c)V and Z。 example 3

[0060] The auxiliary metal layer 316 has a cross-sectional shape parallel to the first substrate 311 (transverse direction), and its cross-sectional shape is any one of circular rings, square rings, or square arrays distributed at intervals, where the squares include rectangles and squares. The shape of the opening V corresponds to the shape of the auxiliary metal layer. Example 1: The transverse cross-sectional shape of the auxiliary metal layer is a circular ring, the transverse cross-sectional shape of the opening is circular, the opening exposes the annular inner wall of the auxiliary metal layer, and the auxiliary metal layer is The height in the Z direction is h, the cross-sectional shape of the layer where the auxiliary metal layer is located is circular (for example, the radius is a), and the side area of the auxiliary metal layer exposed by the opening is S=2πah. Example 2: The transverse cross-sectional shape of the auxiliary metal layer is a square ring, and the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More