Design method and system for reducing link loss of circuit board, and circuit board

A link loss and design method technology, applied in printed circuit components, computer-aided design, programmable/customizable/modified circuits, etc., can solve the problem of increased circuit board cost, occupied circuit board space, and increased circuit board cost High-level problems, to prevent circuit board delamination problems, reduce link loss, and avoid cost increases

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

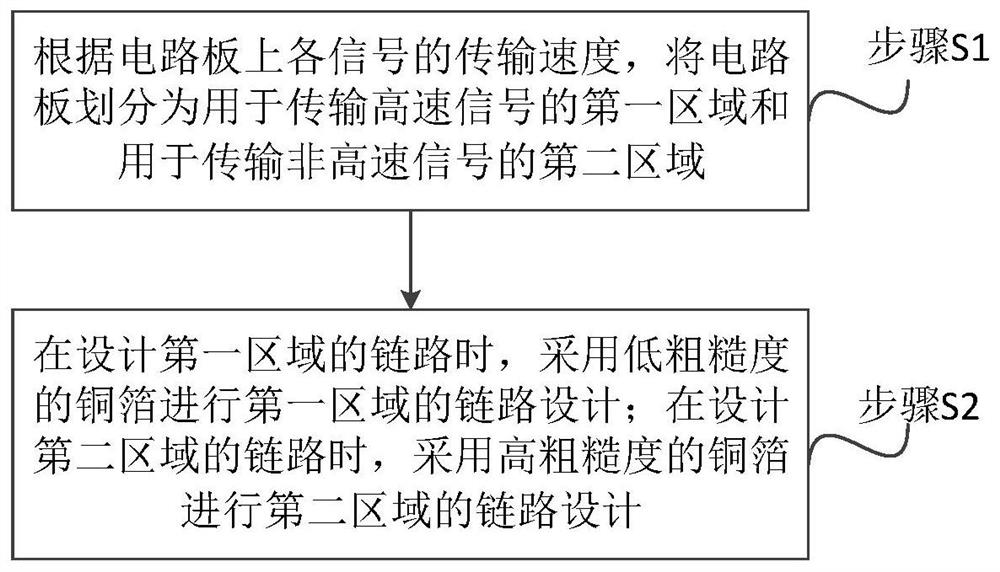

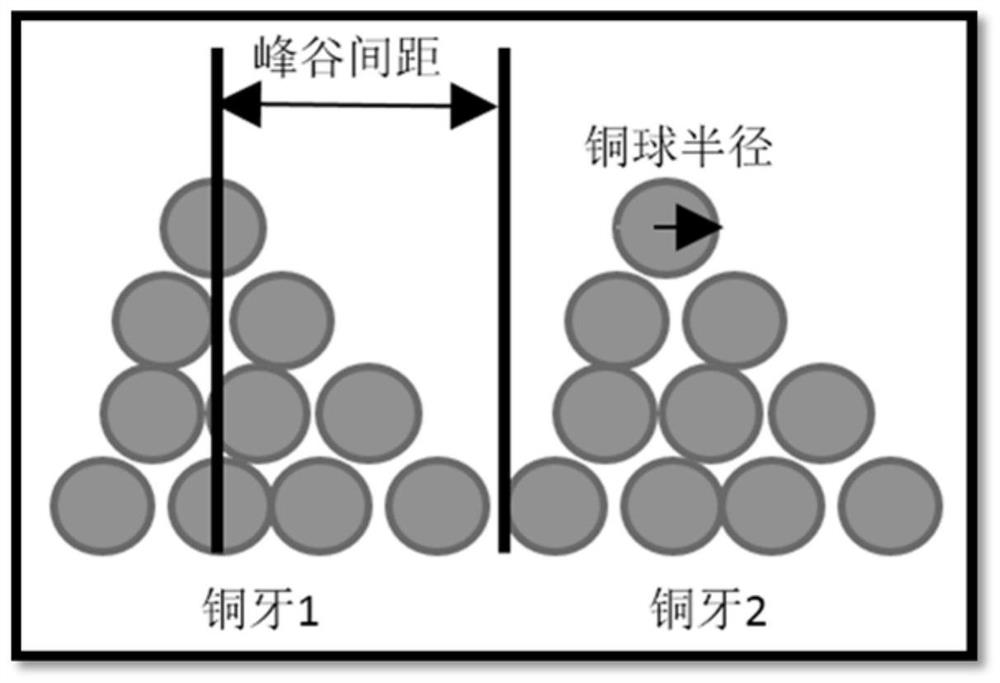

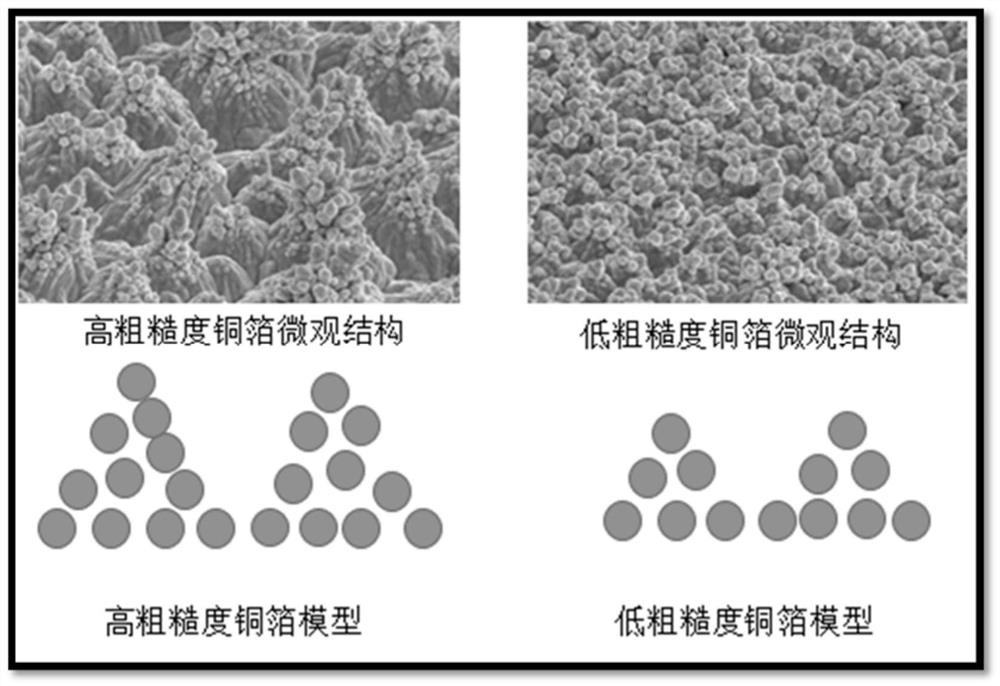

[0048] The core of the present invention is to provide a design method, system and circuit board for reducing the link loss of the circuit board. The link loss is reduced by reducing the roughness of the link copper foil, and the cost increase caused by upgrading the circuit board is avoided. problem and the problem of insufficient wiring space caused by additional driver chips; moreover, this application only reduces the copper foil roughness of high-speed signal links with high link loss requirements, and the copper foil roughness of non-high-speed signal links remains high. Roughness, in order to ensure the degree of bonding between the copper foil and the interlayer medium of the circuit board on the basis of meeting the circuit board link loss requirements, so as to prevent the problem of circuit board delamination caused by insufficient bonding.

[0049] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com