JTE and buried FLR composite terminal structure power device and preparation method thereof

A power device and compound terminal technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large chip area, affecting device breakdown voltage and reliability, and affecting device surface electric field distribution. The effect of simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will now be described more fully with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. This invention may, however, be embodied in many different forms and should not be construed as limited to the exemplary embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art.

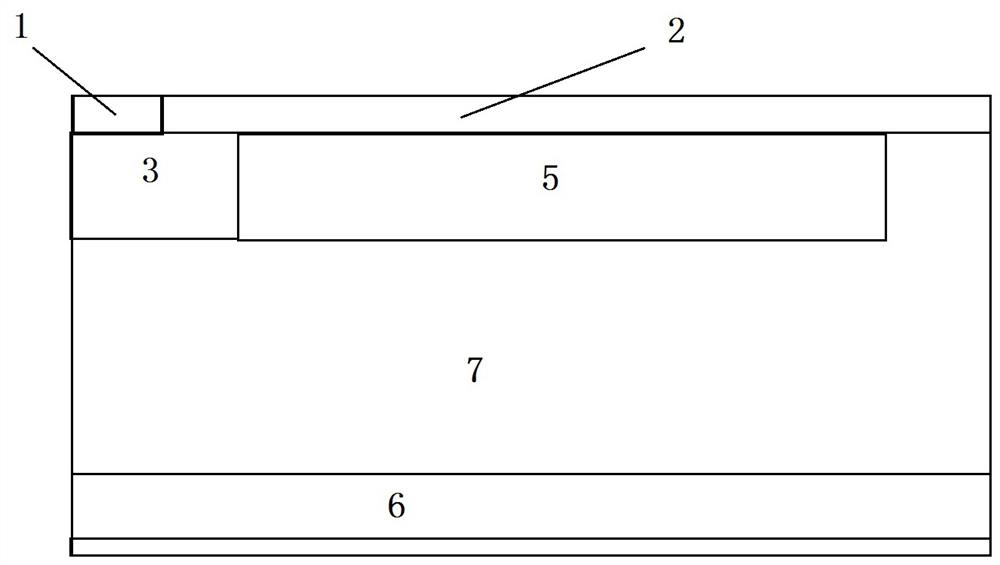

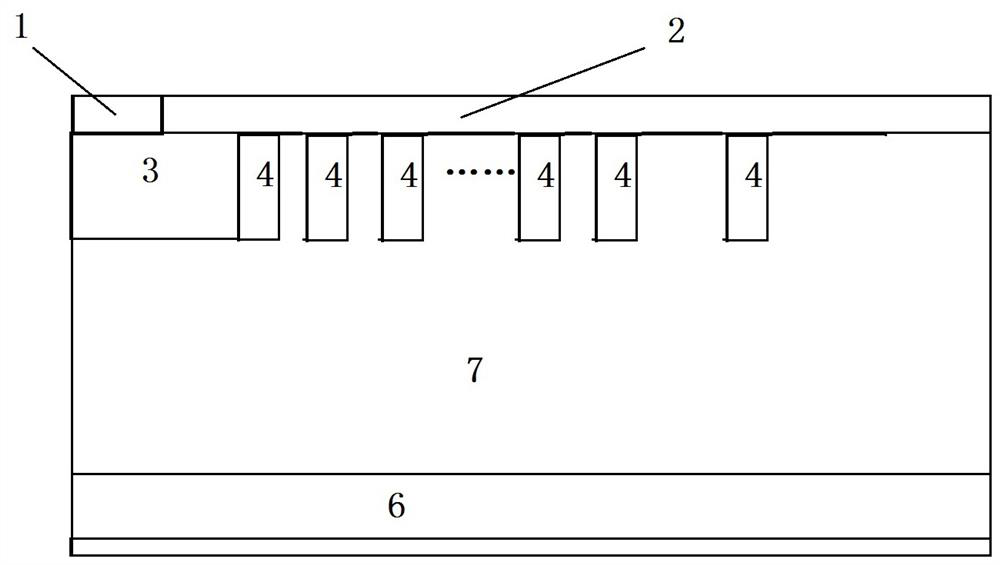

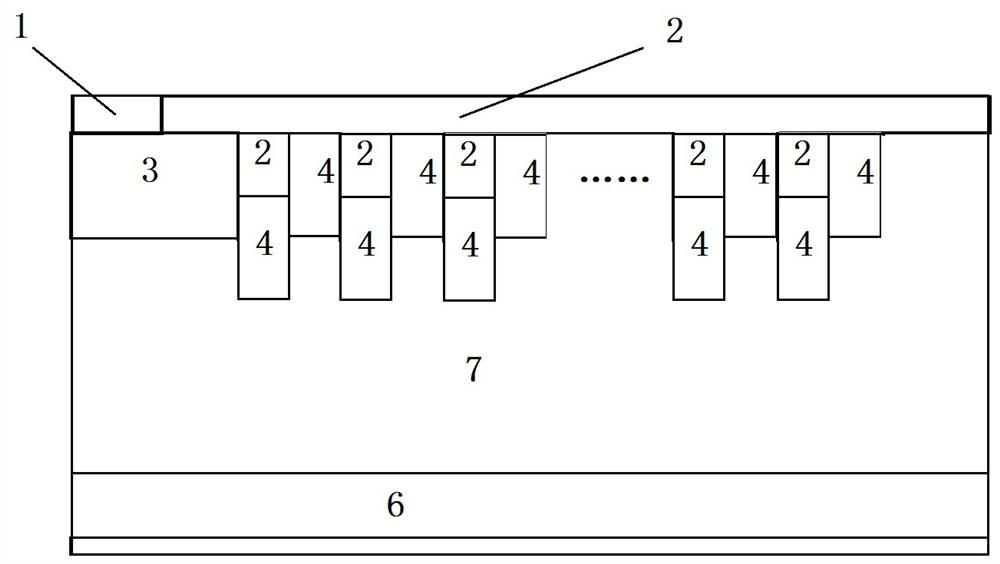

[0035] Such as image 3 As shown, the power device in the embodiment is composed of three structures: the upper layer of the junction terminal region of the N-type epitaxial voltage withstand layer is a P-type layer oppositely doped with the epitaxial layer 7, and at the same time in the upper P-type layer There are discrete multiple trench rings filled with SiO 2 or other High-K dielectrics 2; directly below each trench, there is a P-type ring buried field-limited ring structure oppositely do...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More