Pipeline scheduling method and device

A scheduling device and scheduling method technology, which is applied to multi-programming devices, machine execution devices, instruments, etc., can solve the problems of irrelevant service types, difficult to meet the ultra-low latency of 5G networks at the same time, and complex packet service processing pipelines, etc. The effect of flexible connection, strong scalability, and optimized transmission delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

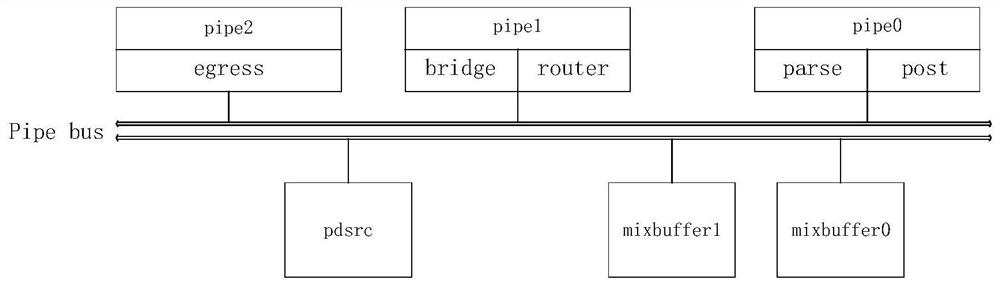

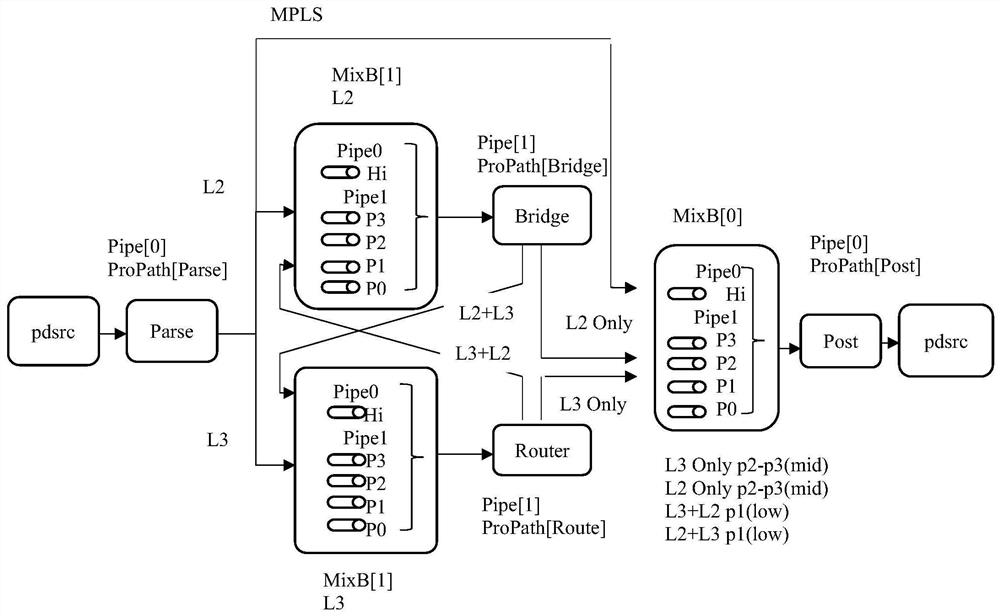

[0042] An embodiment of the present invention provides a pipeline scheduling device, including three physical pipelines, two mixbuffers and a bus pipe bus, wherein:

[0043] The three physical pipelines are logically divided into five pipelines, corresponding to the five stages of message processing in the chip: parse, bridge, router, post and egress;

[0044] The two mix buffers are used to schedule different services, and then send them into the corresponding logic pipeline;

[0045] Each pipeline unit pipe, mix buffer and pdsrc are connected to the bus pipe bus to complete the interaction between each pipeline unit.

[0046] Specifically, the new pipeline scheduling device changes the traditional two physical pipelines into three physical pipelines, and logically divides them into five pipelines, corresponding to the five stages of message processing in the chip: parse, bridge, router, post, egress.

[0047] Since the message jumps between the pipelines, the present inven...

Embodiment 2

[0050] Such as figure 1 As shown, various pipeline units are mounted on the bus pipe bus provided by the embodiment of the present invention, including pdsrc, two mix buffers and pipe, wherein:

[0051] Pdsrc mainly completes the packet descriptor generation of the message entering the pipeline, and the message descriptor enters the pipe for processing;

[0052] Mix buffer completes the processing instruction jump switching and scheduling of message descriptors between pipes;

[0053] Pipe completes specific message processing, and the specific processing process is filled by developers using microcode.

[0054] Further, in the embodiment of the present invention, the two mix buffers include a first mix buffer and a second mix buffer, wherein the first mix buffer includes high, medium, and low priority queues, and the second mix buffer includes high , medium, and low priority queues.

Embodiment 3

[0056] The embodiment of the present invention provides a logical division method of a physical pipeline, which logically divides three physical pipelines into five pipelines, specifically:

[0057] The first physical pipeline pipe0 is divided into two logical processing pipelines: parse and post;

[0058] The second physical pipeline pipe1 is divided into two logical processing pipelines, bridge and router;

[0059] The third physical pipeline Pipe2 corresponds to the egress logic pipeline.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More