Patents

Literature

30results about How to "Optimize transmission delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

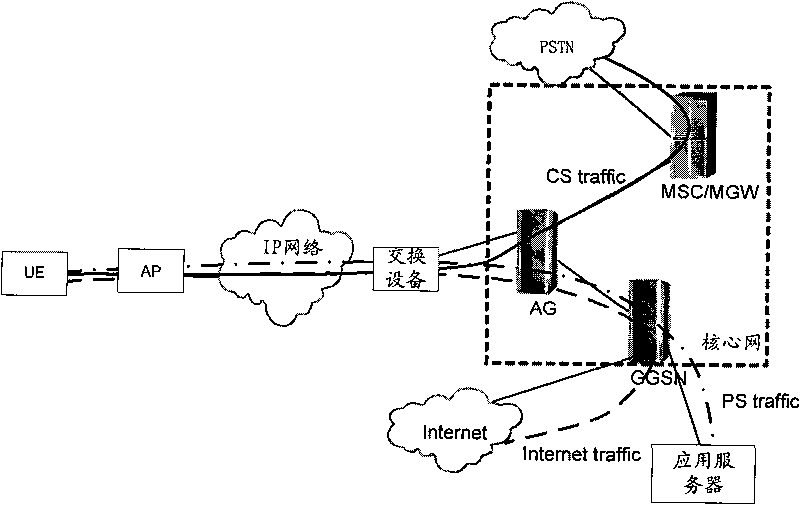

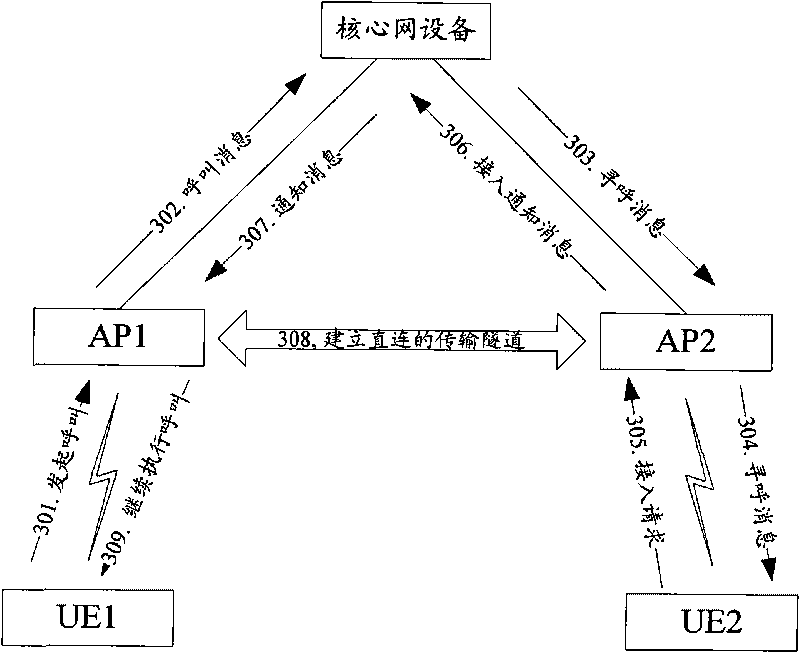

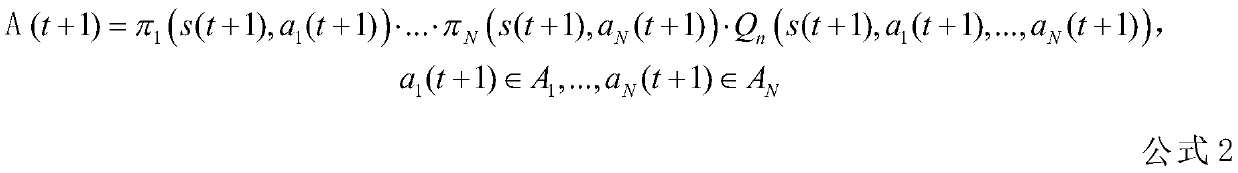

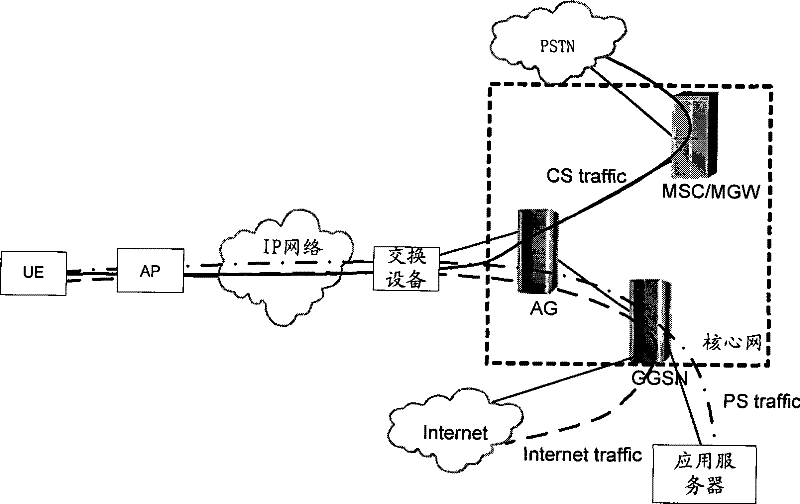

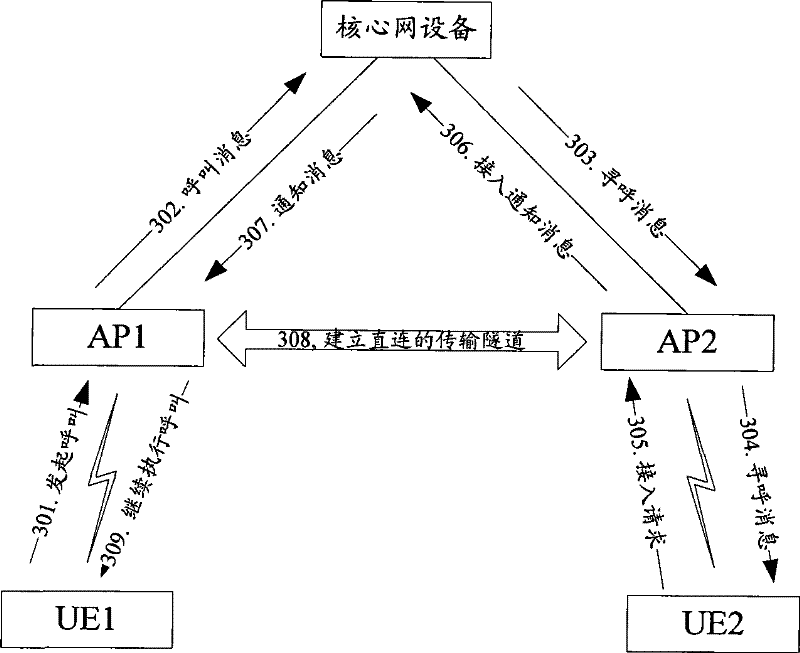

Transmission optimization method, system and equipment of AP network

ActiveCN101742690AOptimize the transmission pathEliminate Bandwidth BottlenecksConnection managementTransmission delayReal-time computing

The embodiment of the invention discloses a transmission optimization method of an AP network, a first access point receives a call message sent to a second user by a first user; the first access point acquires the communication address of a second access point belonging to the second user; and the first access point establishes a direct-connecting transmission tunnel between the first access point and the second access point to enable the first user to communicate with the second user by the direct-connecting tunnel. In the embodiment of the invention, the transmission path of the AP network can be optimized, the transmission delay is improved, the bandwidth bottleneck of a core network is eliminated and meanwhile, the cost of the core network is lowered.

Owner:HUAWEI TECH CO LTD

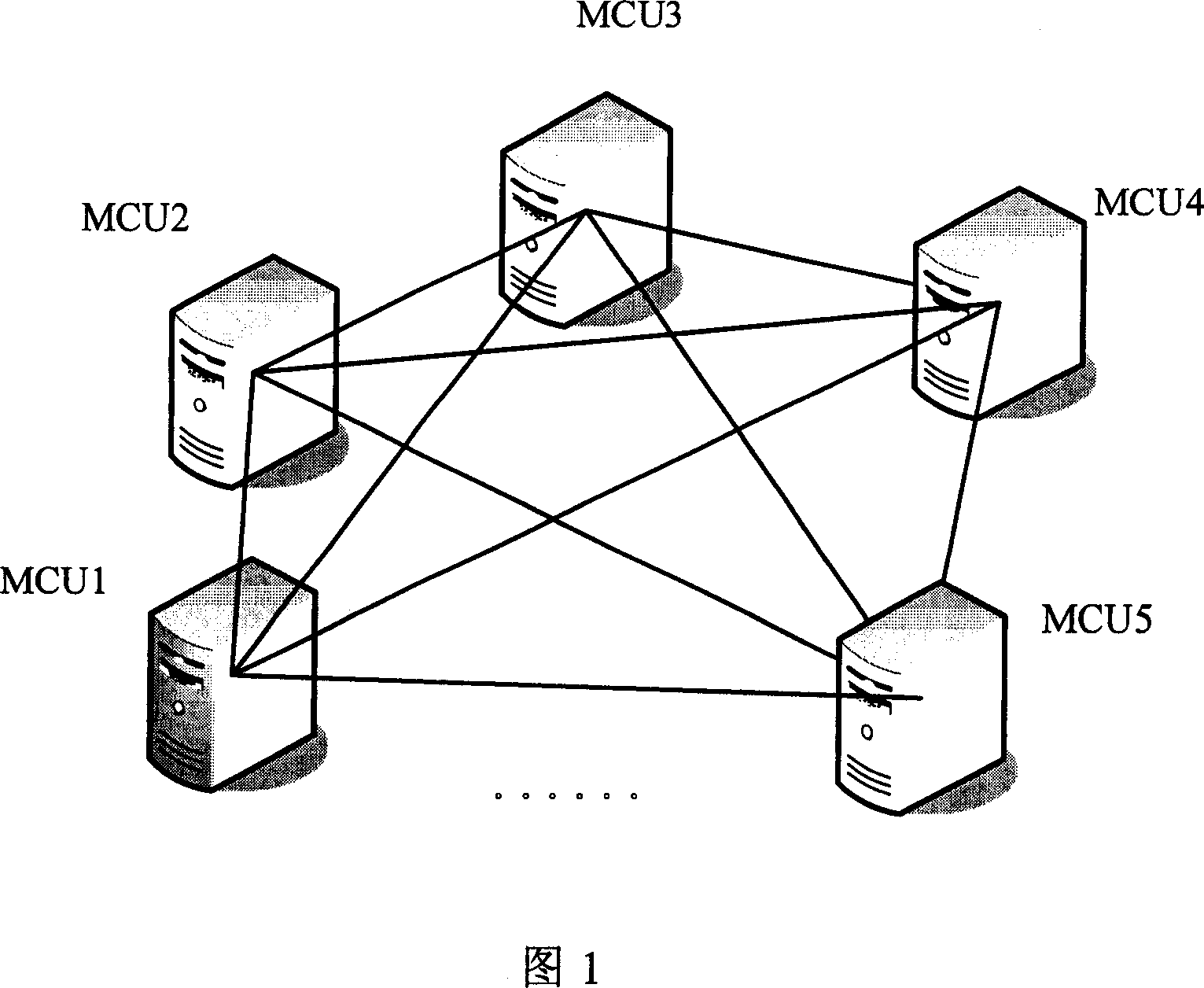

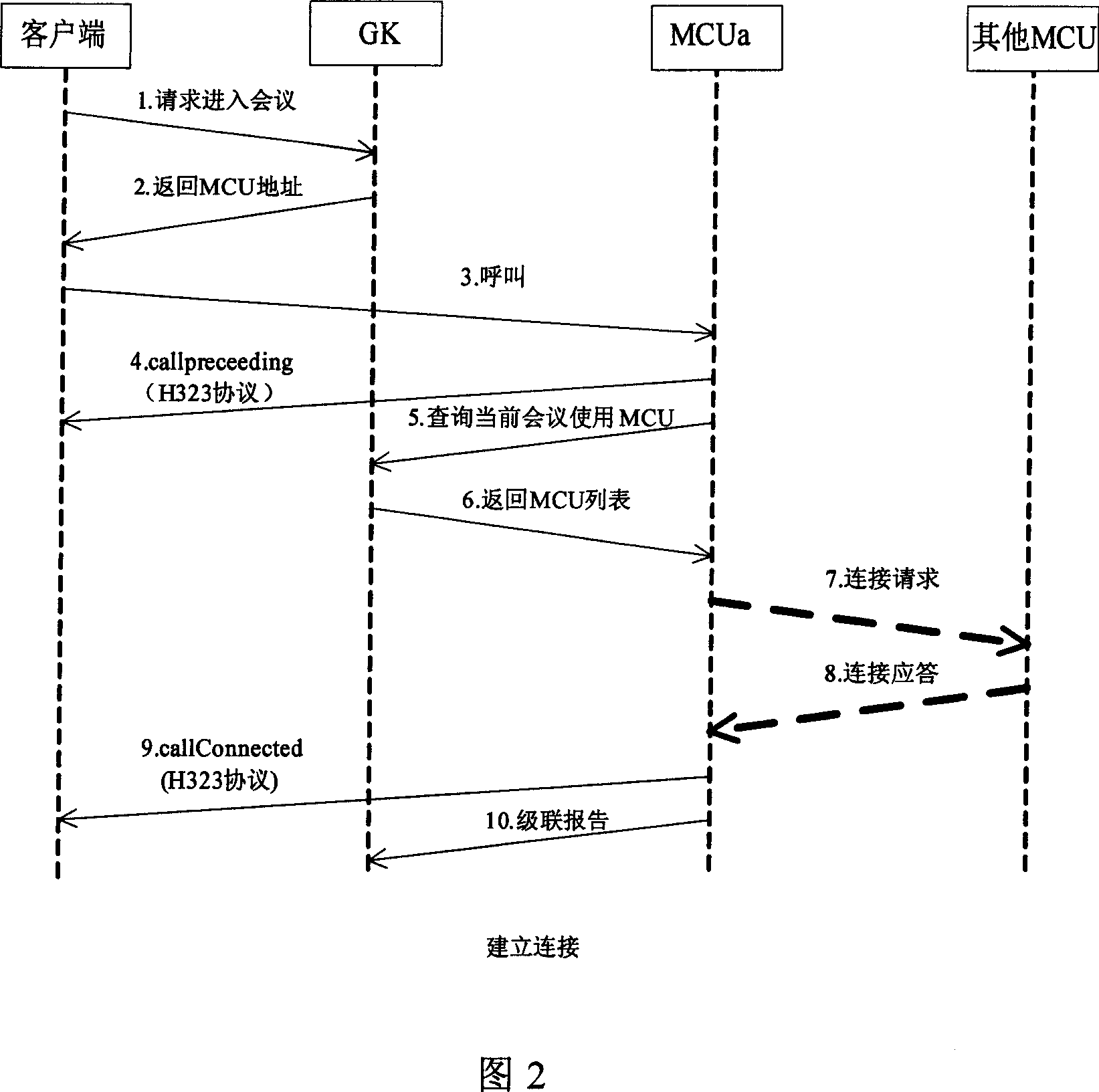

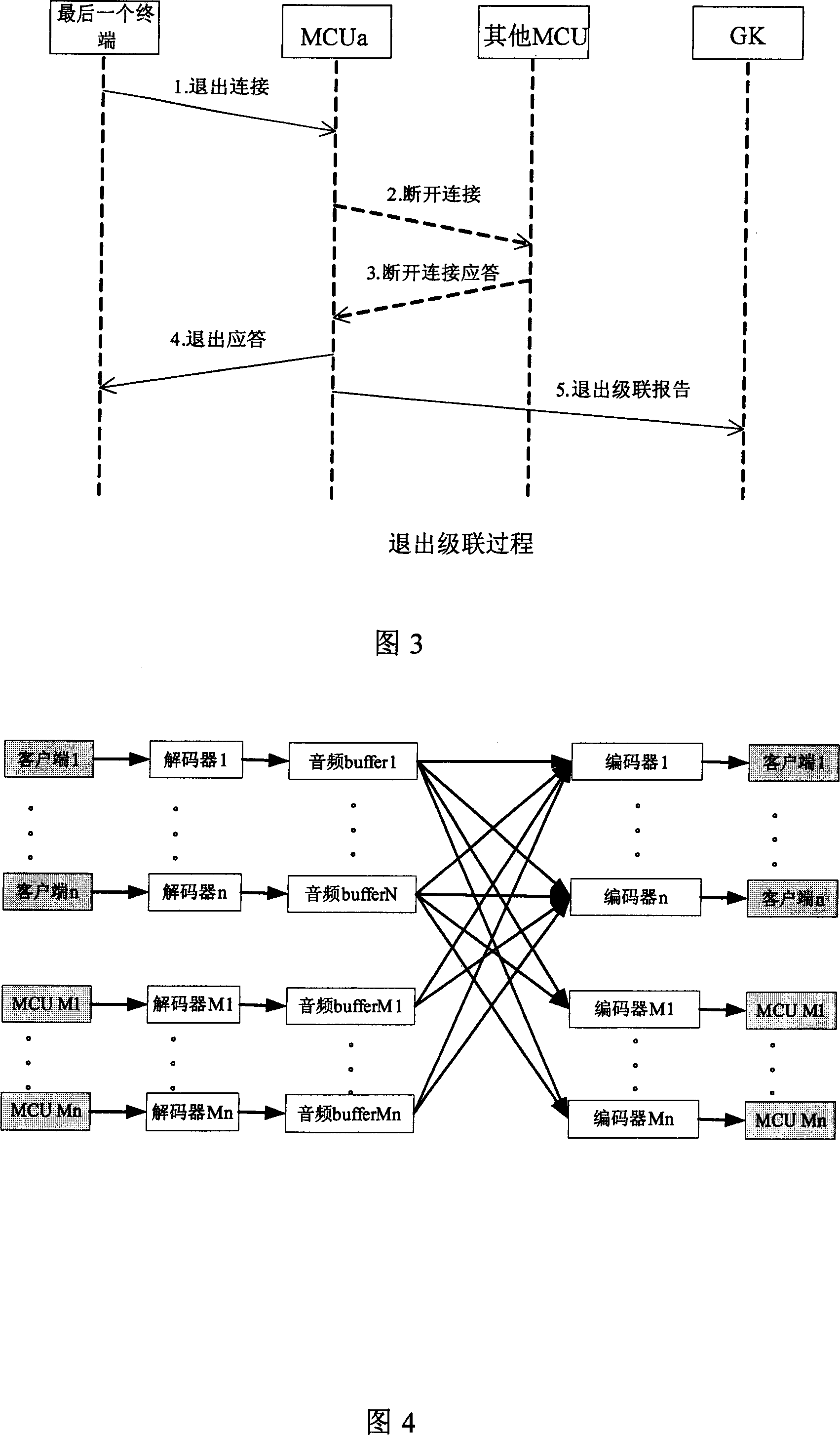

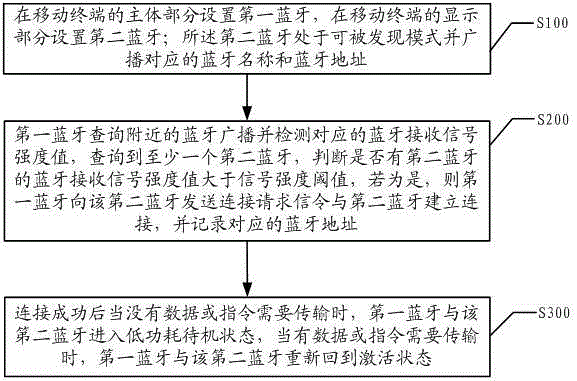

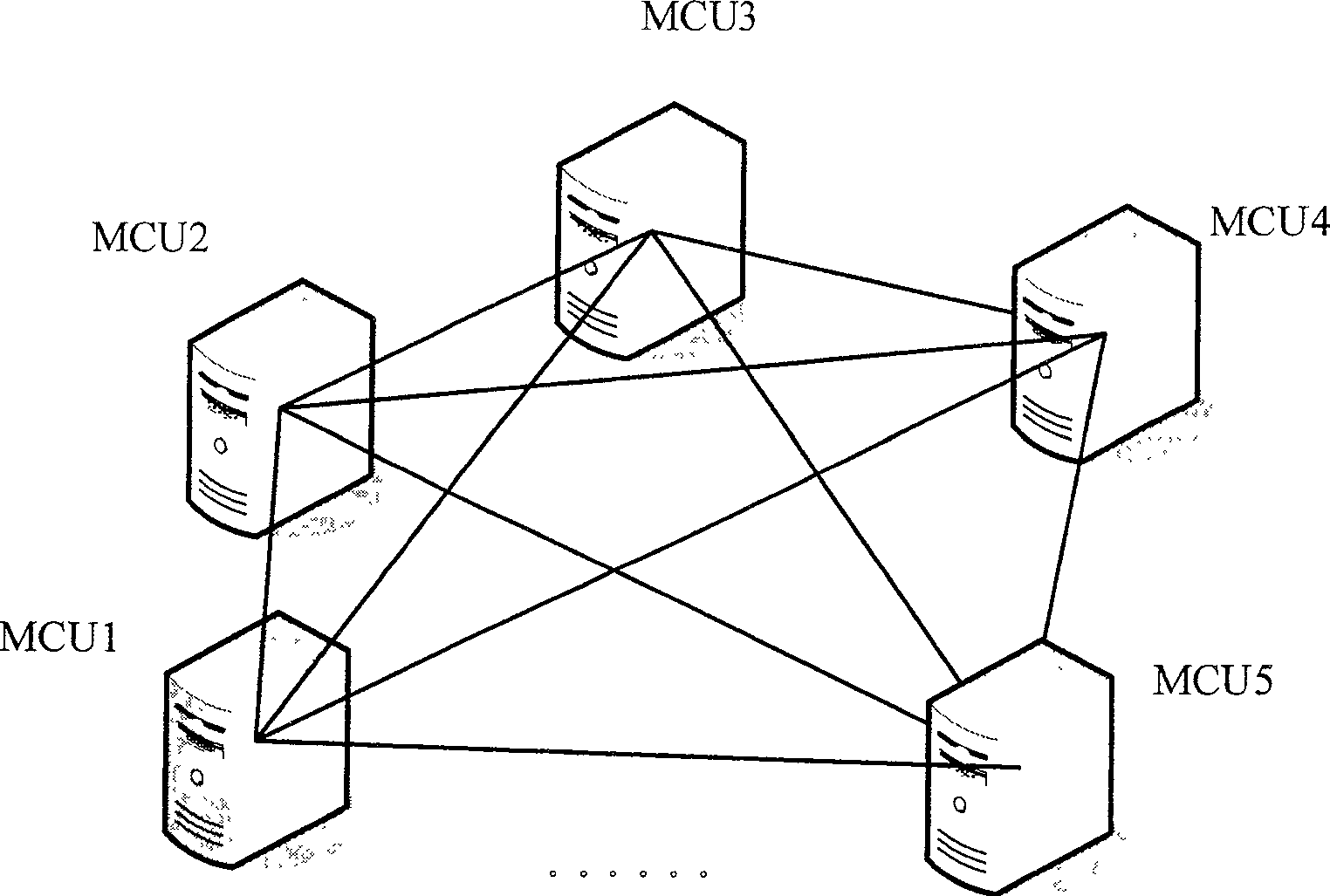

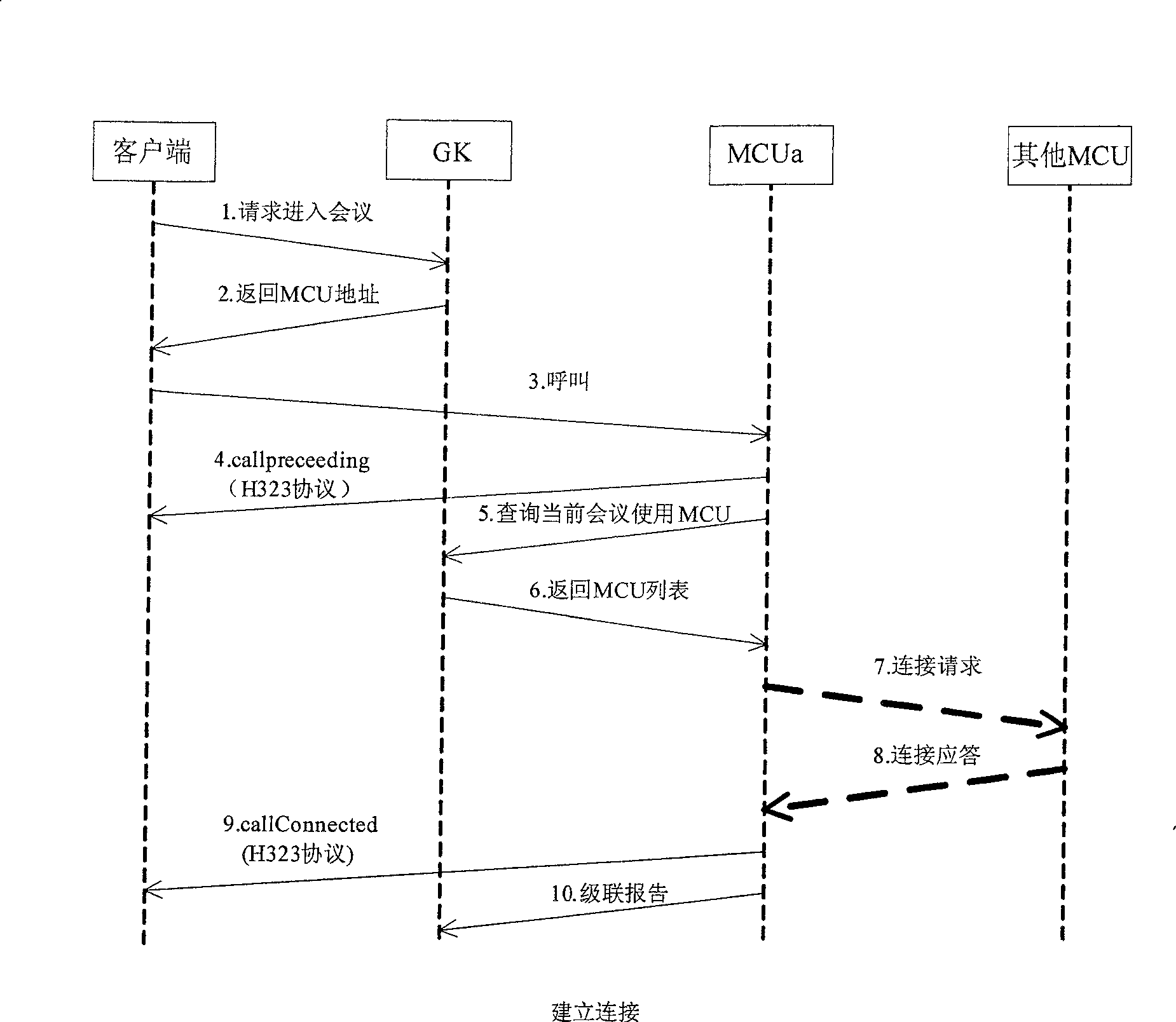

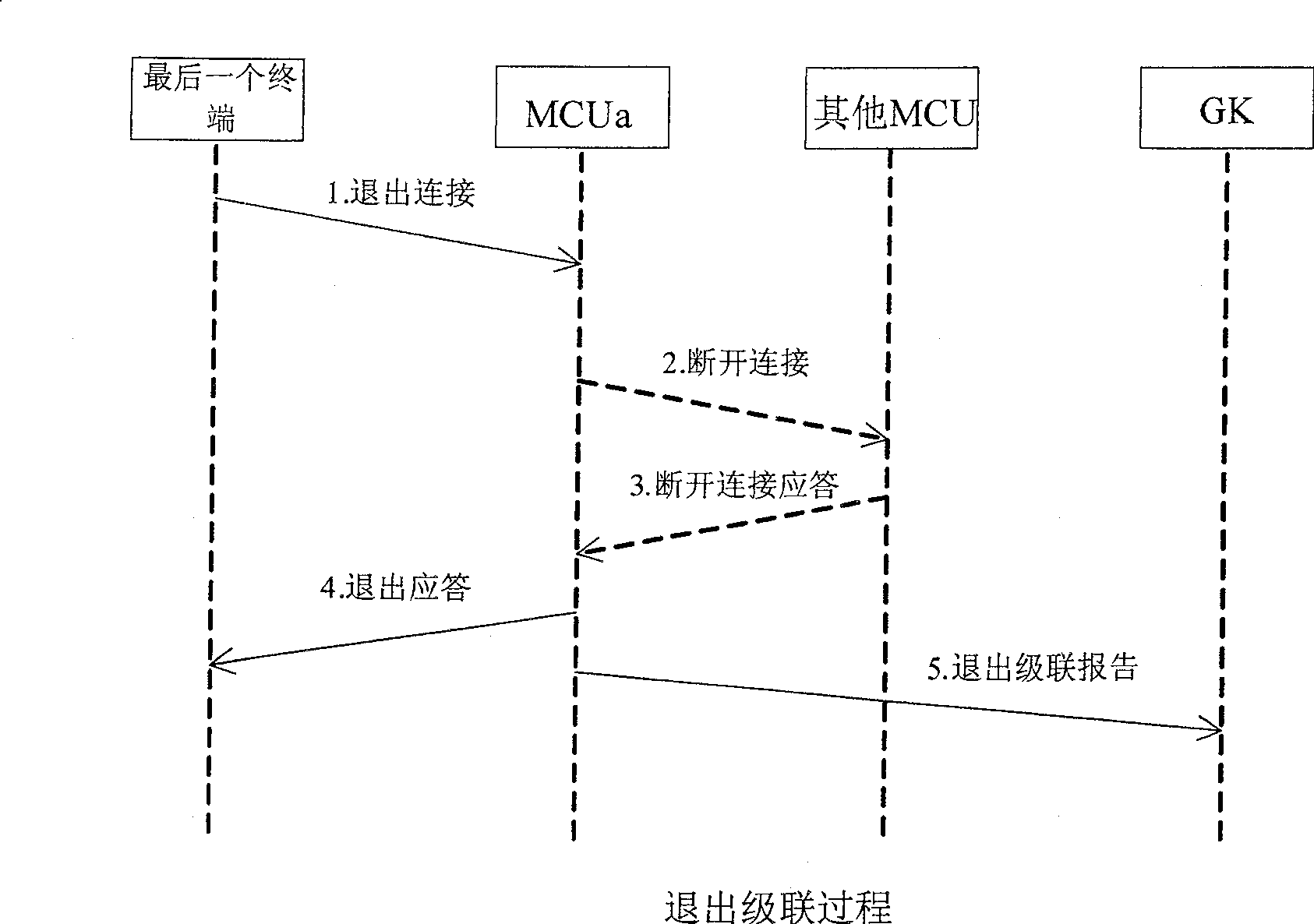

Audio mixing method in multiple-MCU video conference system

InactiveCN1953537AOptimize transmission delayAvoid system unavailabilityTelevision conference systemsTwo-way working systemsData transmissionClient-side

The invention relates to a mixing method in multi-MCU video conversation system. Wherein, (1), all MCU register to gatekeeper, while each MCU has one-to-one connection with other MCU and each MCU maintains one connection list with other MCU and one local client list with mixing demand; (2), MCU based on local mixing client list linearly layers the voice data sent from local client, and codes and sends result to each opposite MCU; (3), MCU reduces the sent voice data from mixed result to be mixed with the decoded voice from opposite MCU, to be coded and sent to target client. The invention can reduce the transmission jump number of voice data and avoid single-point accidence of main MCU, with high reliability.

Owner:BEIHANG UNIV

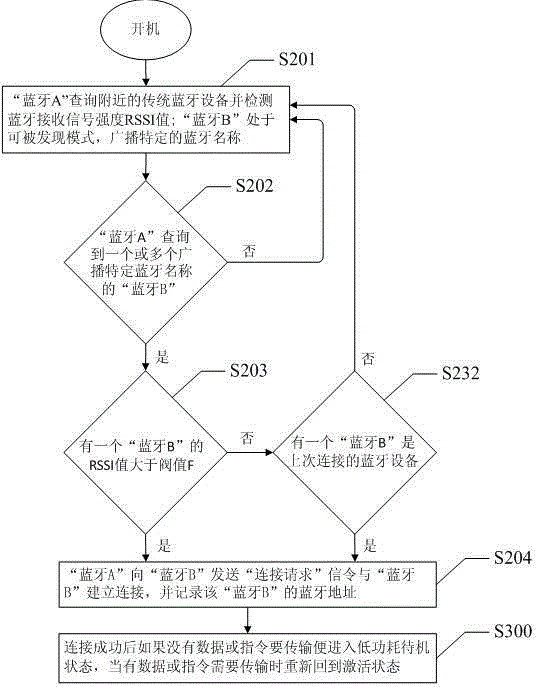

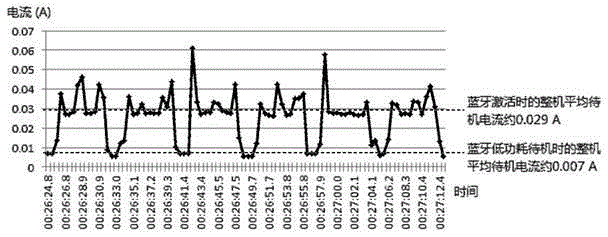

Bluetooth interconnection method and system for mobile terminal

ActiveCN105406923AImprove responsivenessReduce Bluetooth transmission delayConnection managementTransmission monitoringVIT signalsTransmission delay

The invention discloses a Bluetooth interconnection method and system for a mobile terminal. The Bluetooth interconnection method comprises the following steps: setting a first Bluetooth at a main body of the mobile terminal and setting a second Bluetooth at a display part of the mobile terminal; inquiring a nearby Bluetooth broadcast by the first Bluetooth and detecting a corresponding Bluetooth received signal strength value, querying to at least one second Bluetooth, and judging whether a Bluetooth received signal strength value of the second Bluetooth is greater than a signal strength threshold value, if so, then transmitting a connection request signaling to the second Bluetooth by the first Bluetooth to establish a connection with the second Bluetooth, and recording a corresponding Bluetooth address; after the connection is successful, when no data or instruction needs to be transmitted, entering a low power standby state by the first Bluetooth and the second Bluetooth; and when the data or instruction needs to be transmitted, returning to an activated state again by the first Bluetooth and the second Bluetooth; therefore, after startup, a Bluetooth chip is always under a low power connection state, thus the Bluetooth response speed can be effectively improved and the Bluetooth transmission delay can be reduced.

Owner:雷鸟创新技术(深圳)有限公司

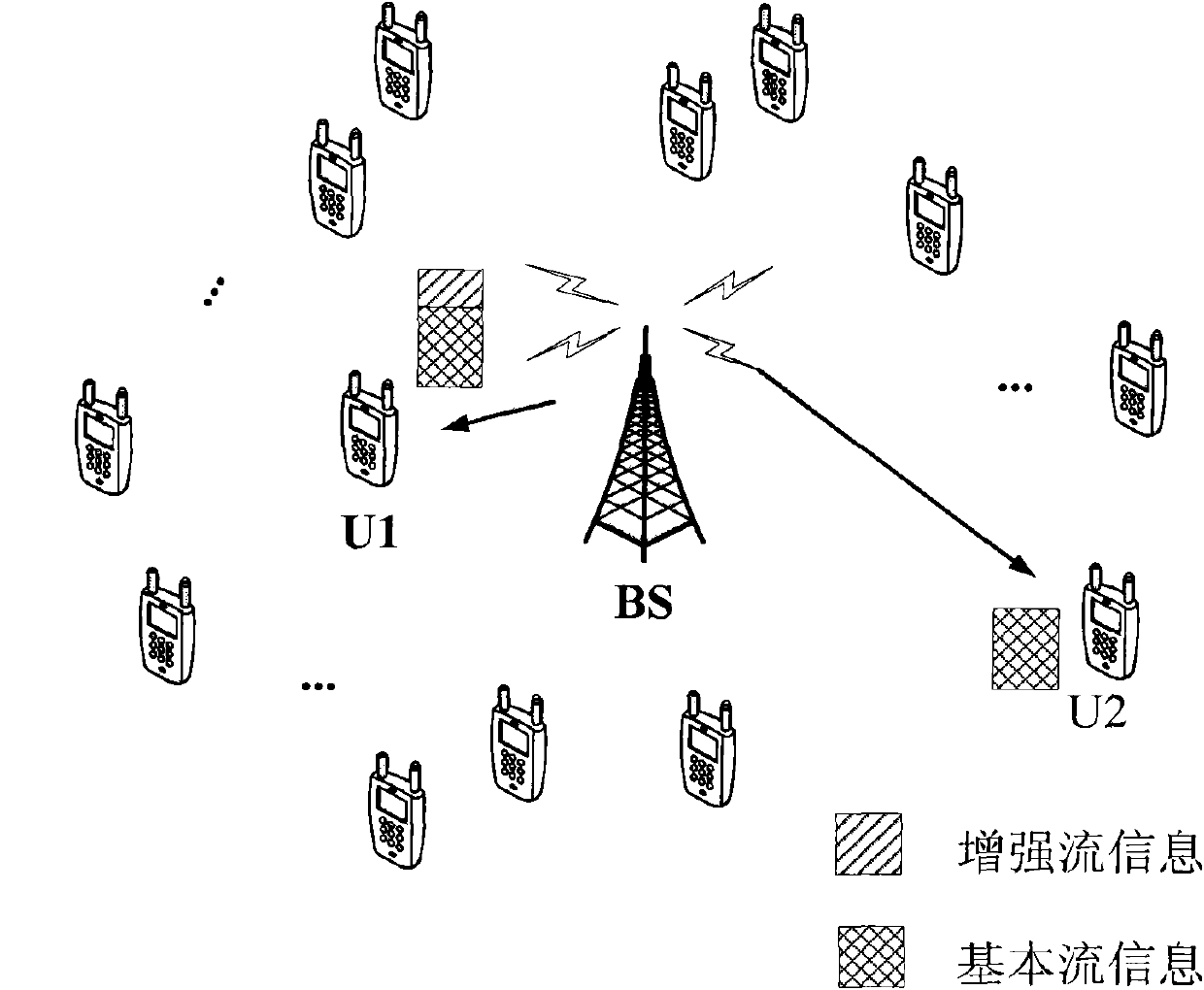

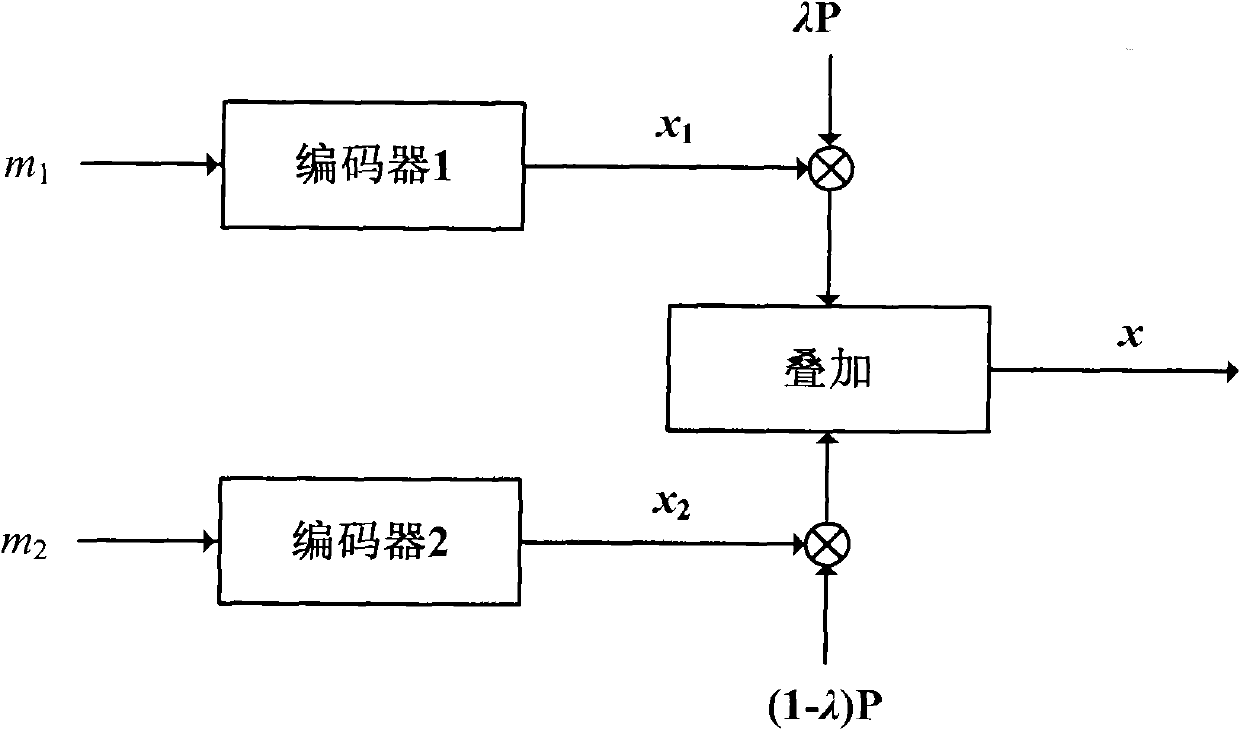

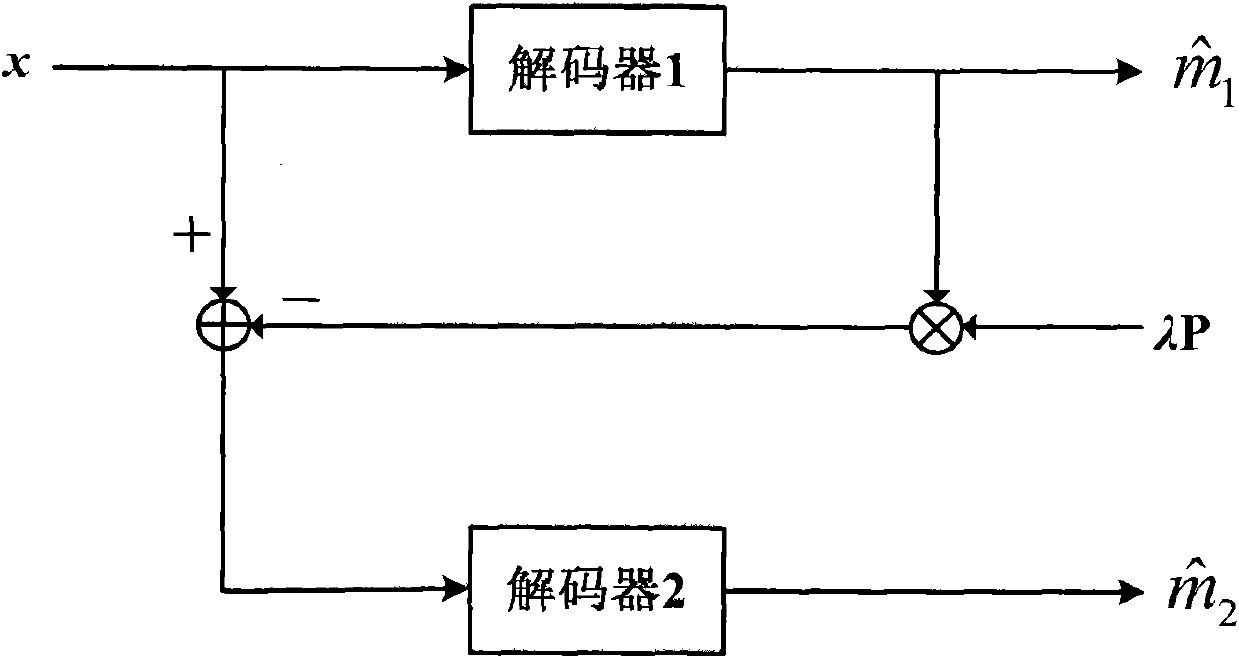

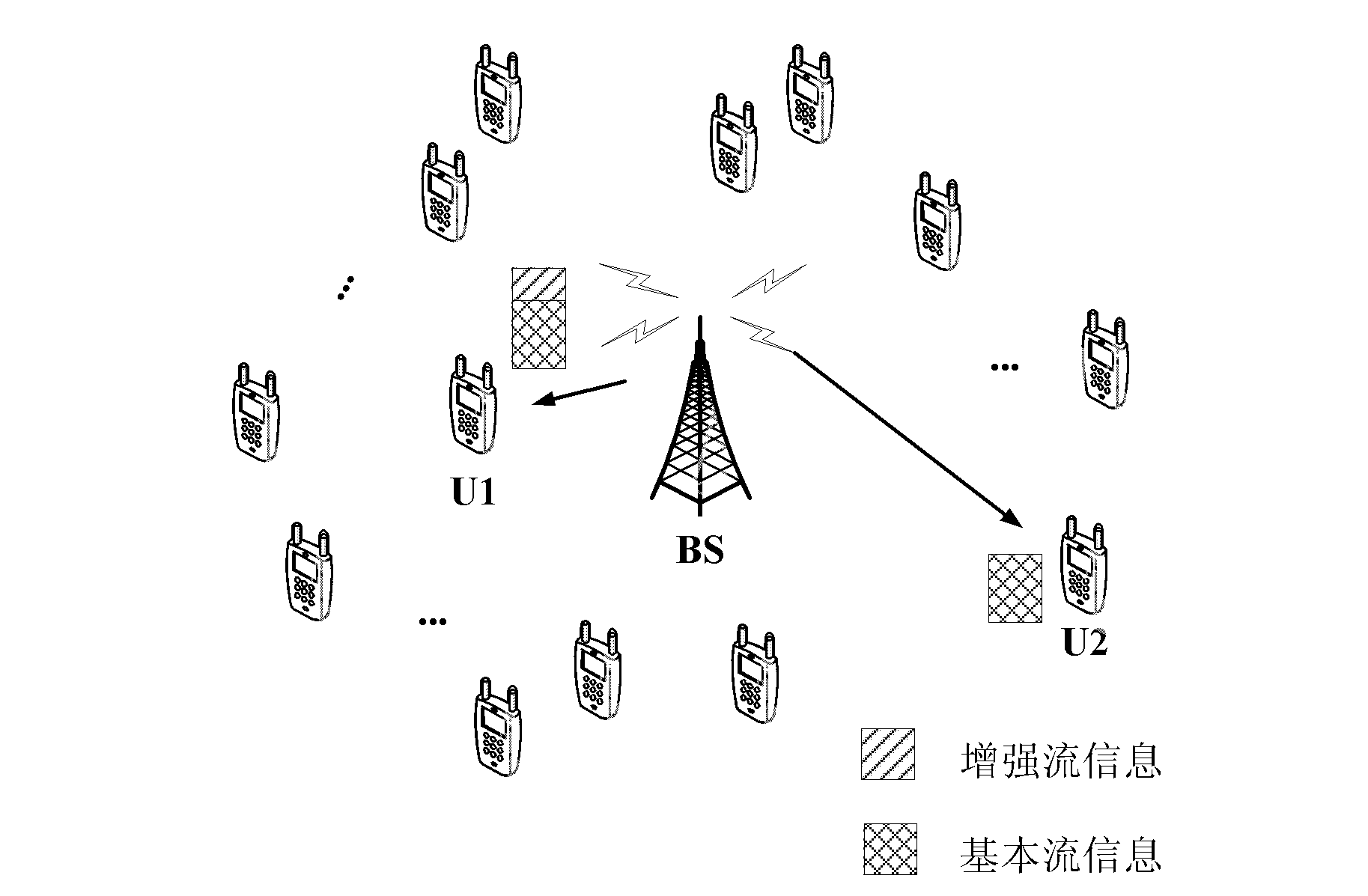

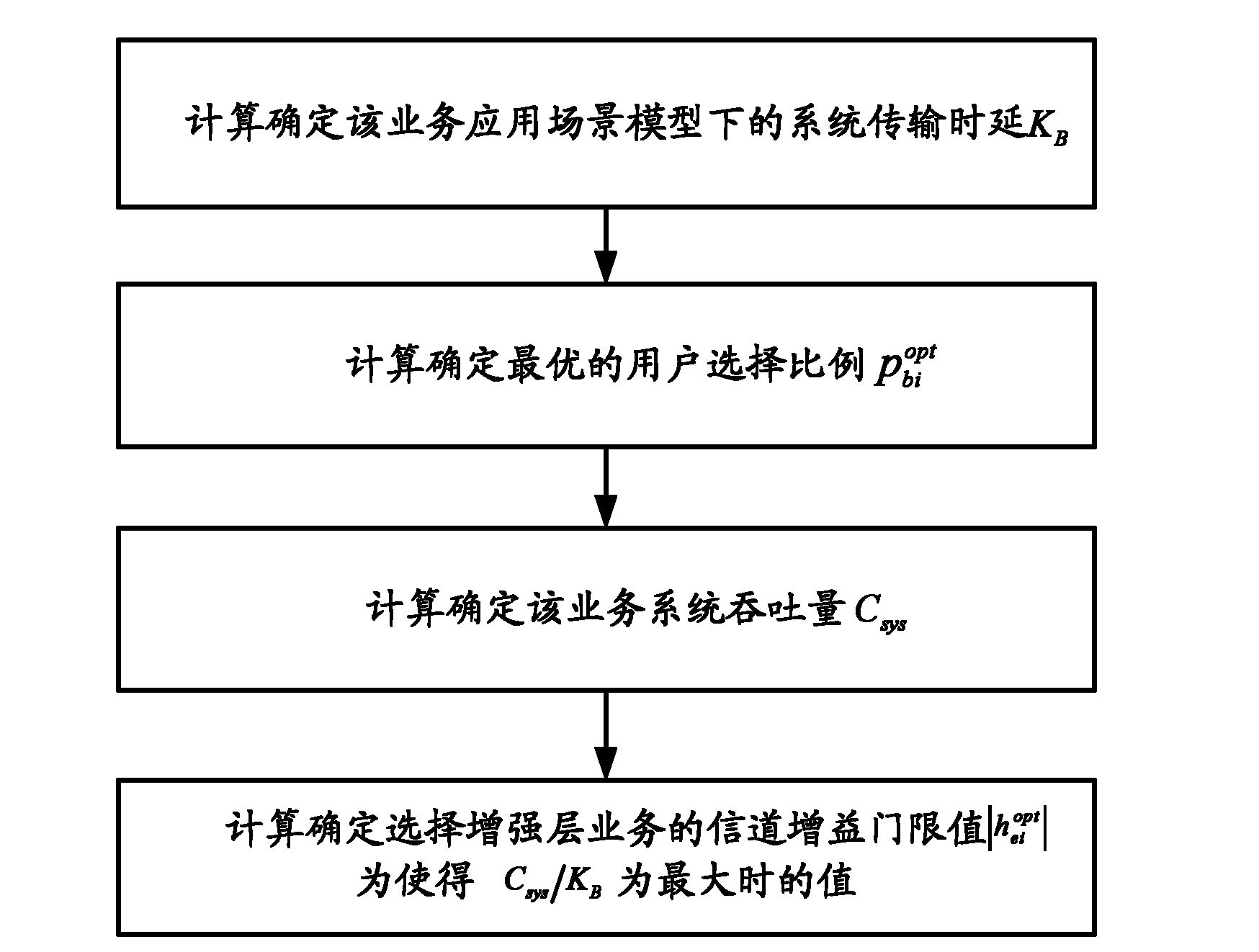

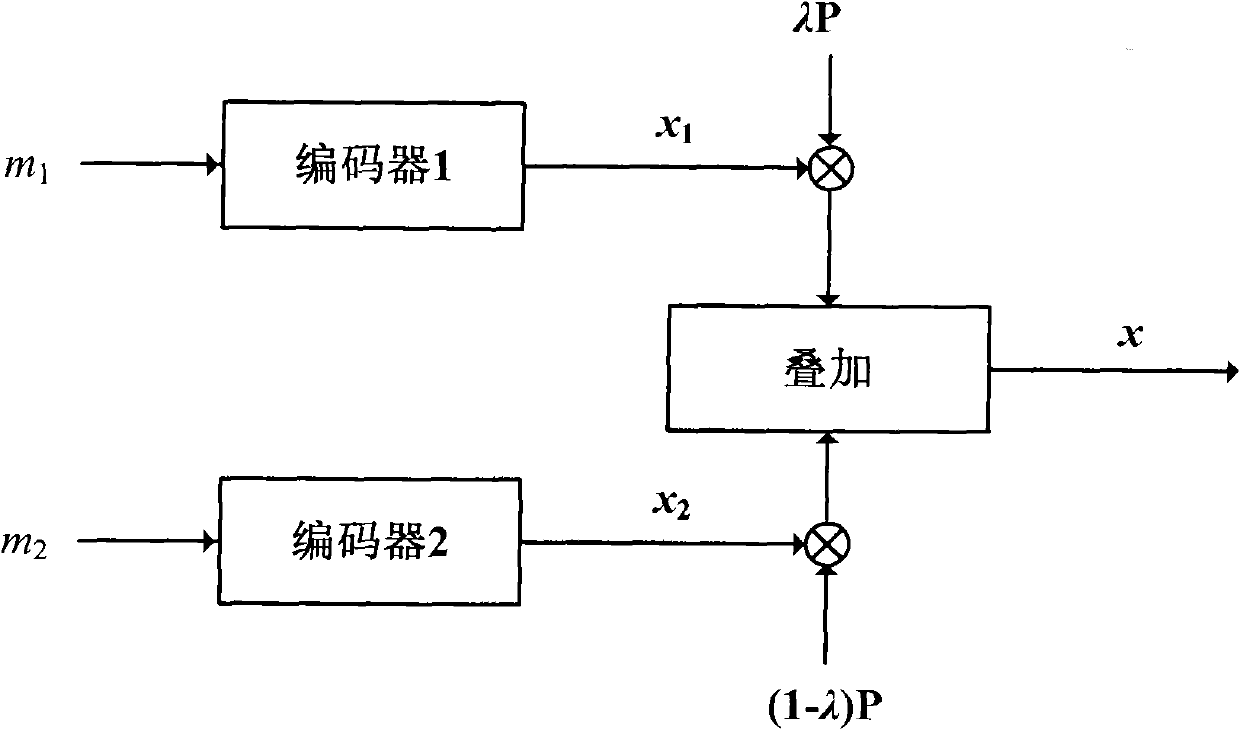

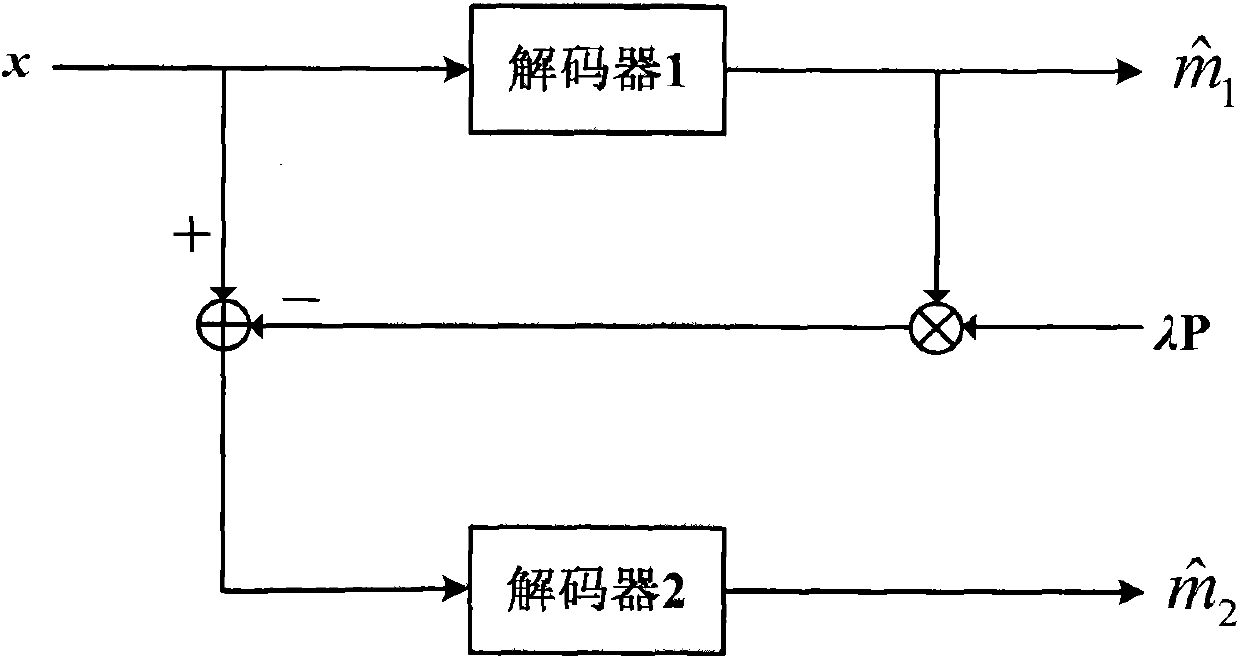

Power allocation method for wireless broadcast multicast layered modulation

InactiveCN102036184AImprove service qualityAchieve optimization goalsPower managementBroadcast service distributionWireless broadcastSystem time

The invention discloses a power allocation method for wireless broadcast multicast layered modulation. In the method, a transmitting end allocates power lambda P to an elementary stream, allocates (1-lambda)P to an enhanced stream and transmits the elementary stream at a first user selected rate pb and the enhanced stream at a second user selected rate pe every time, until the user rate of receiving the elementary stream is presumed to be more than or equal to a preset rate H, wherein the lambda is a power allocation factor and is more than 0 and less than or equal to 1, and P is total power for transmitting the elementary stream and the enhanced stream; and the value of the lambda is determined to be the maximum value of the lambda, wherein Cu is throughput of the enhanced stream at the transmission finishing moment, KB is system time delay at the transmission finishing moment, Cu and KB are expressions of the lambda, and H is more than or equal to 90 percent. The invention provides an optimal power allocation method, and the system performance optimization is realized.

Owner:BEIJING UNIV OF POSTS & TELECOMM

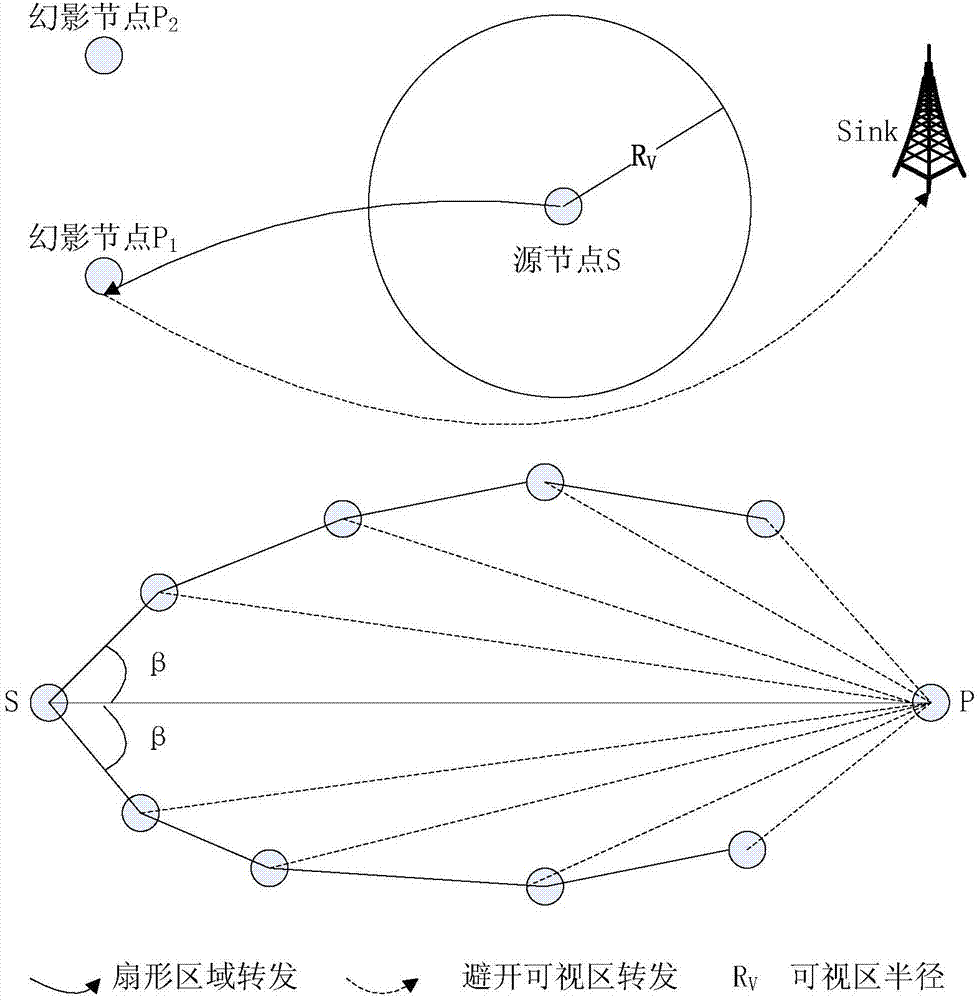

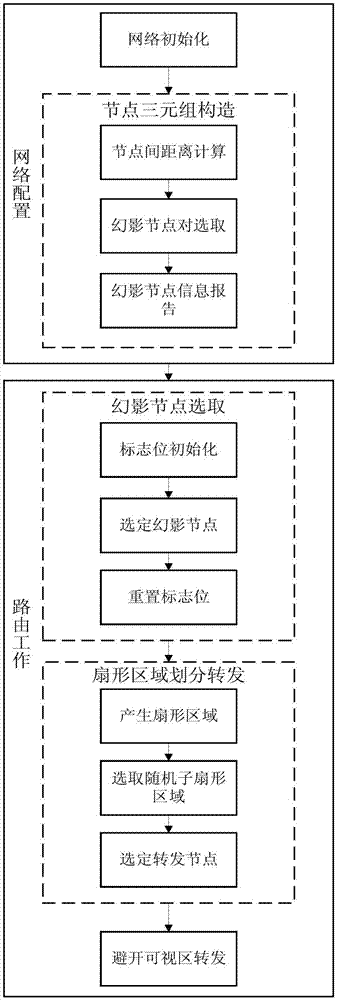

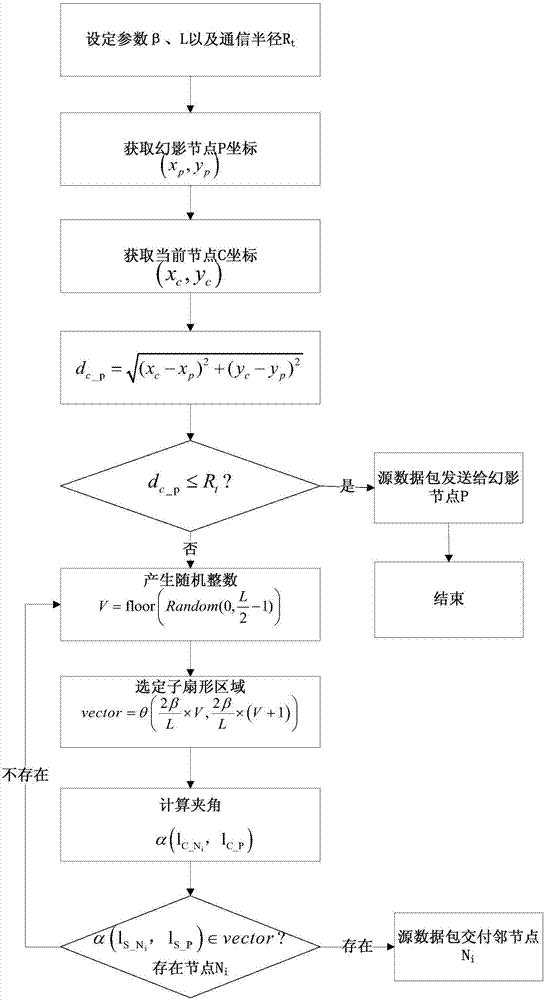

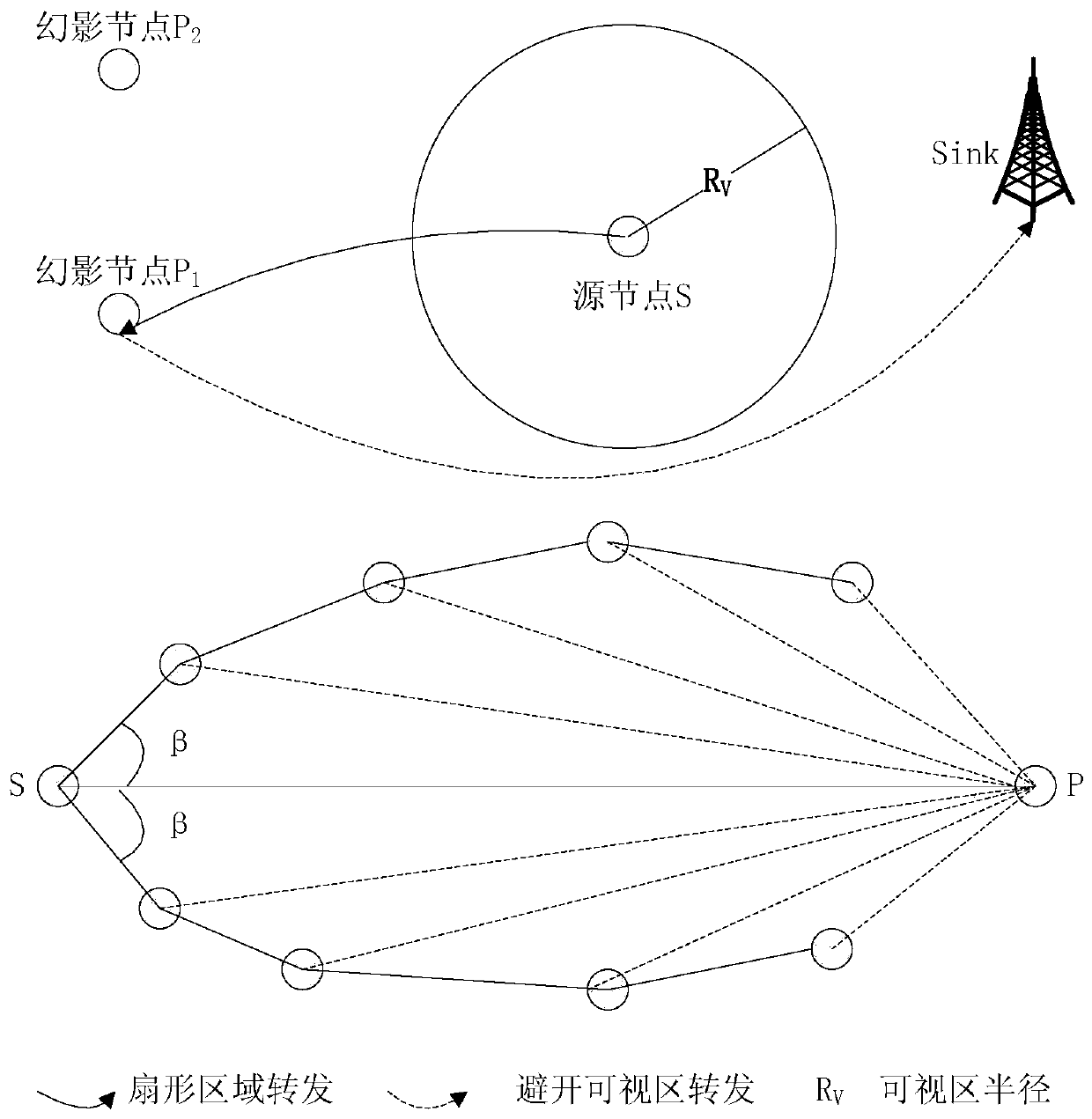

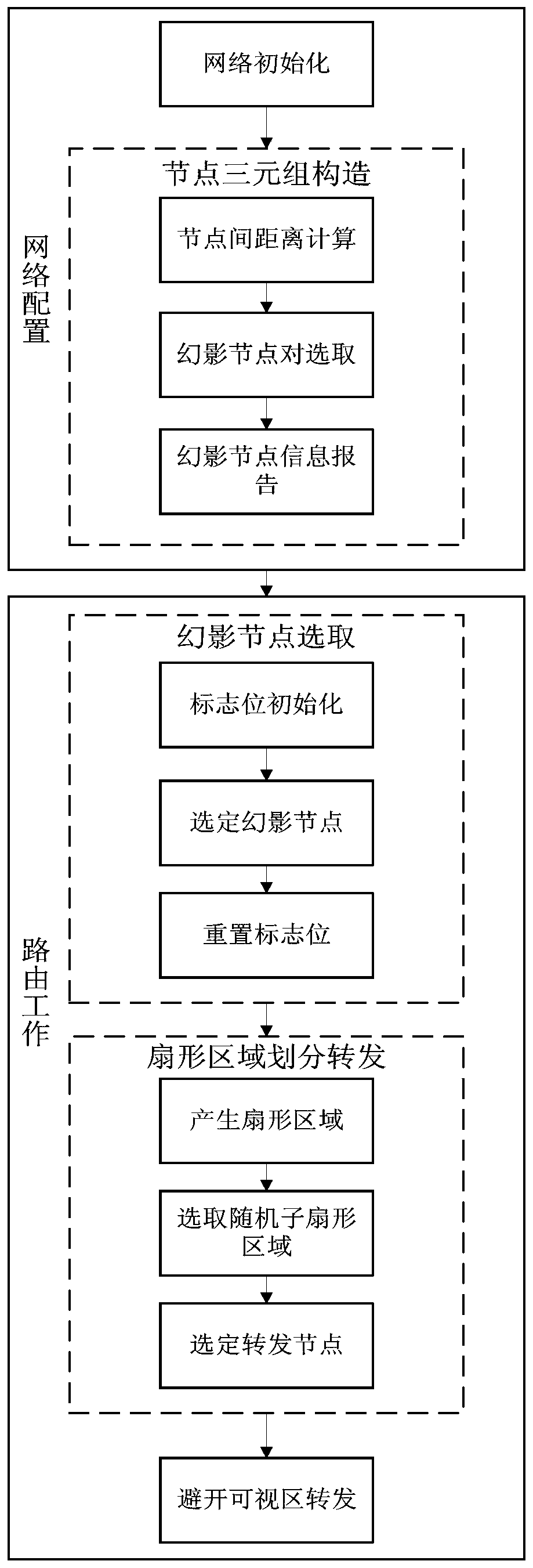

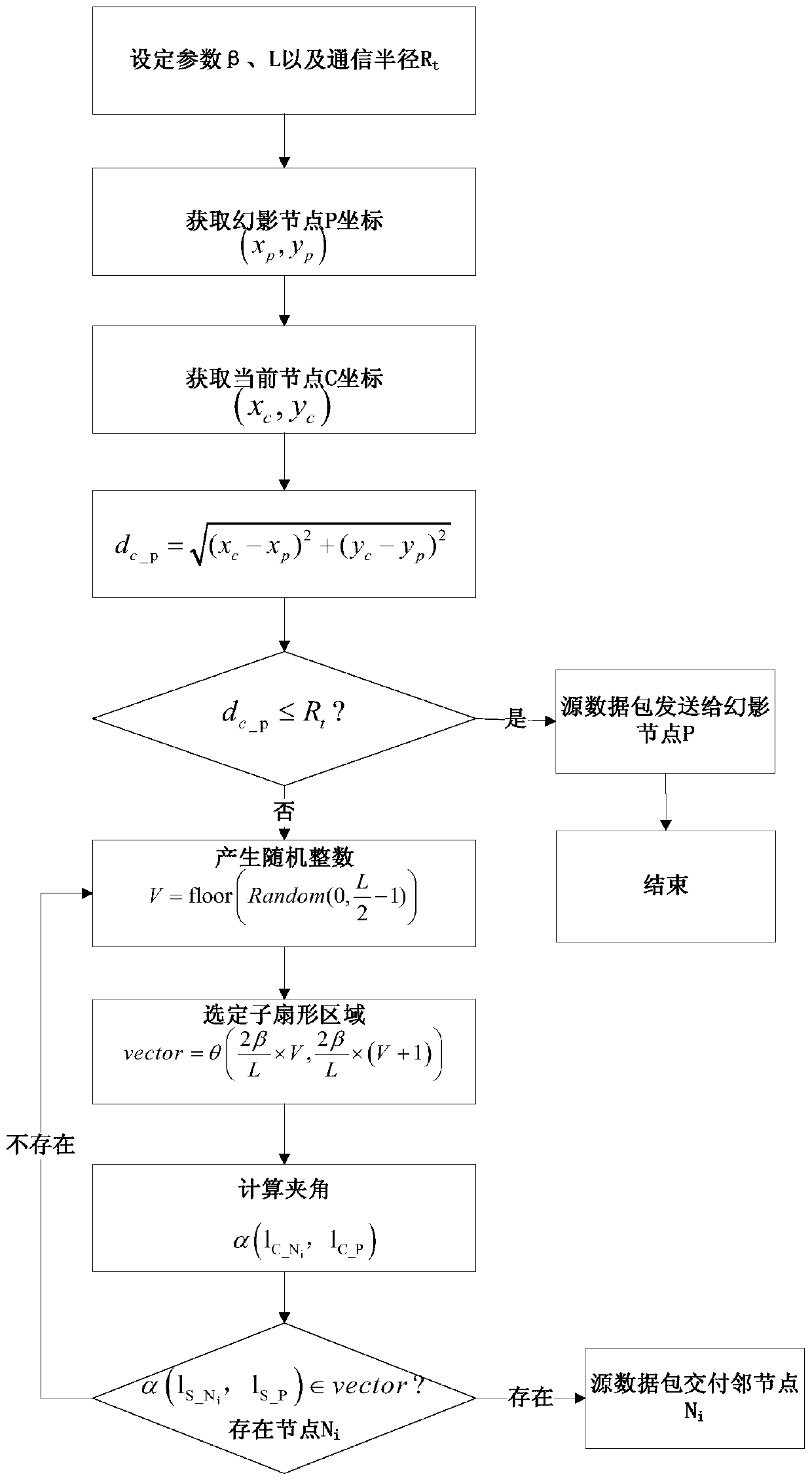

Source position privacy protection method based on multi-phantom node strategy

ActiveCN107148013AImprove practicalityImprove securityNetwork topologiesSecurity arrangementTransmission time delayPrivacy protection

A source position privacy protection method based on multi-phantom node strategy comprises the steps of: initializing a network, constructing a node triple, alternatively selecting phantom nodes, transmitting the source node-phantom node based on a sector area division, and keeping away from a visible range to transmit the phantom node-base station. By using the multi-phantom node idea, the method generates two phantom nodes at the same time to form a node triple; any two nodes of the node triple can be used as the alternative phantom node of the third node; moreover, in the working stage of the route, the source data packet is transmitted by combining the sector area division method and the visible range avoiding strategy; thus, the security of the source node is effectively increased by keeping away from the visible range of the source node; and, the transmission time delay and the energy consumption of the router are well controlled at the same time.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

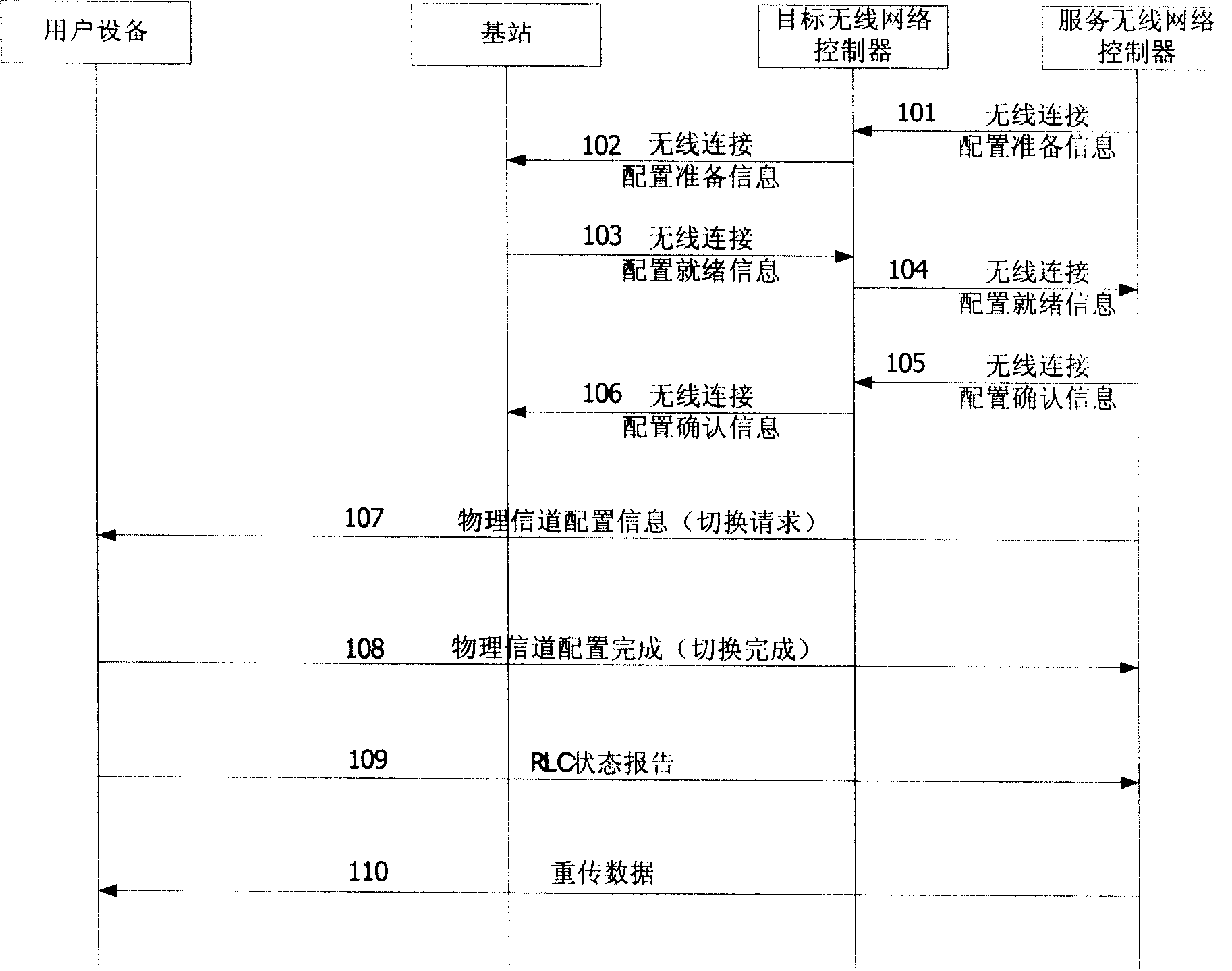

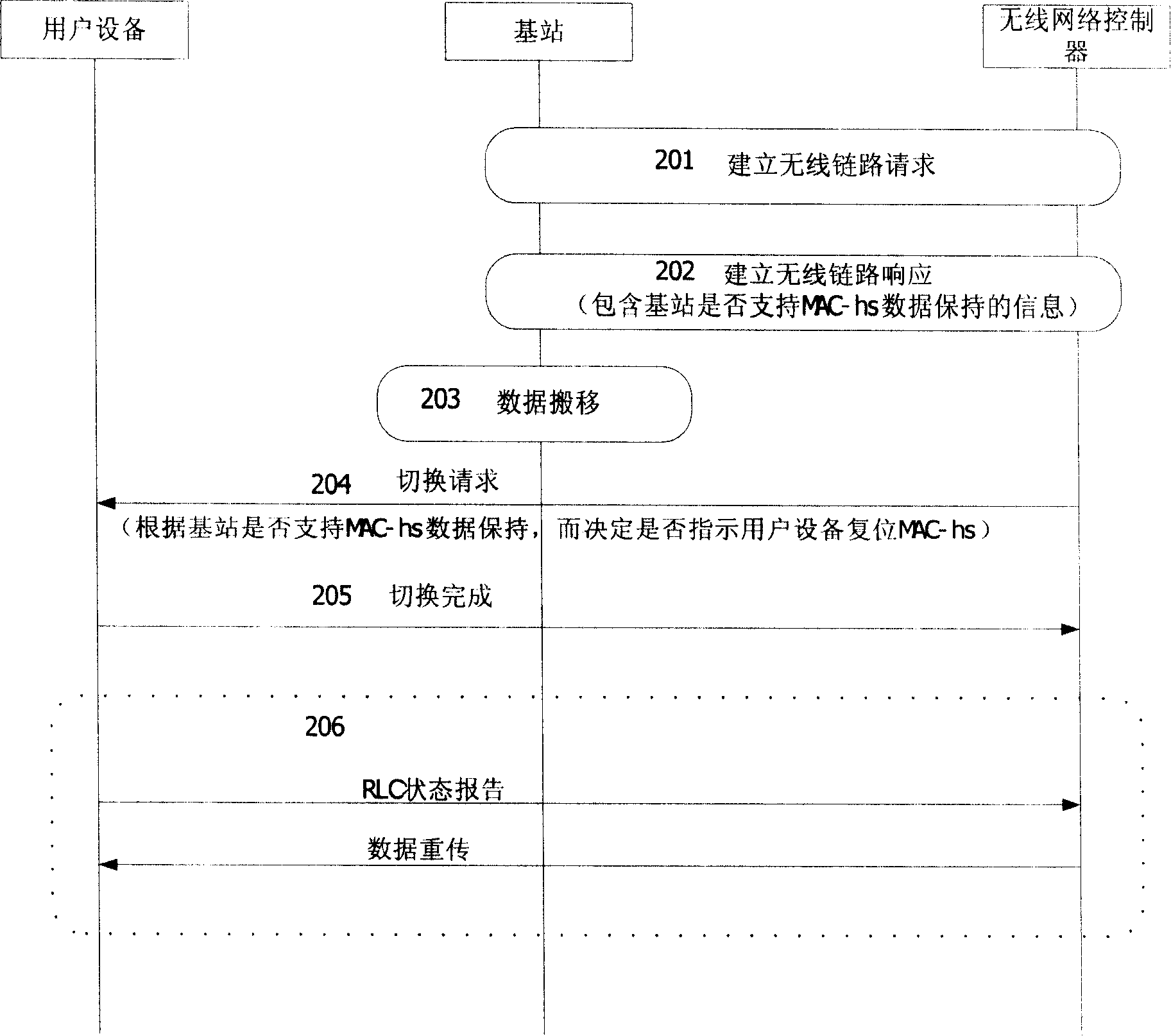

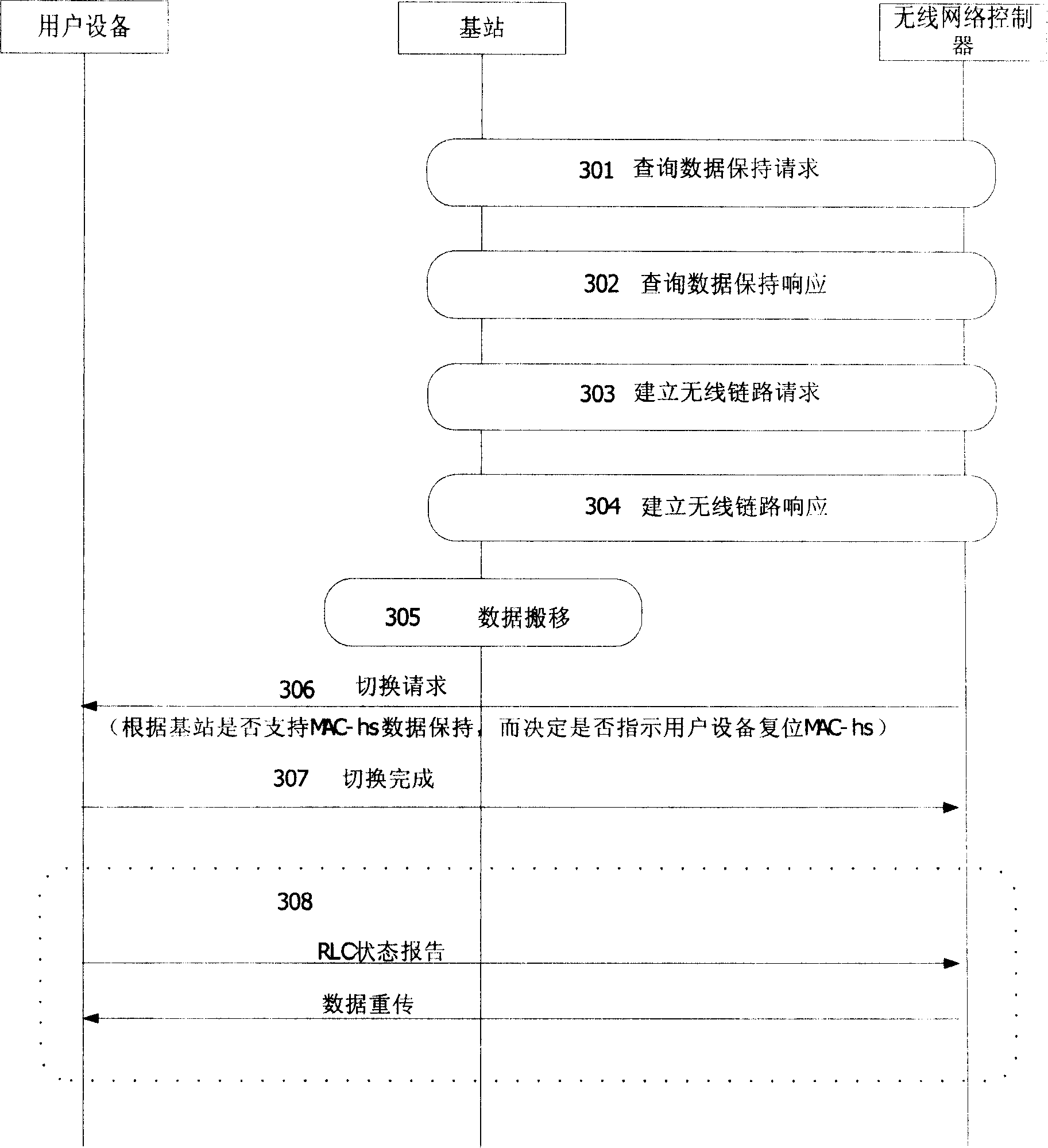

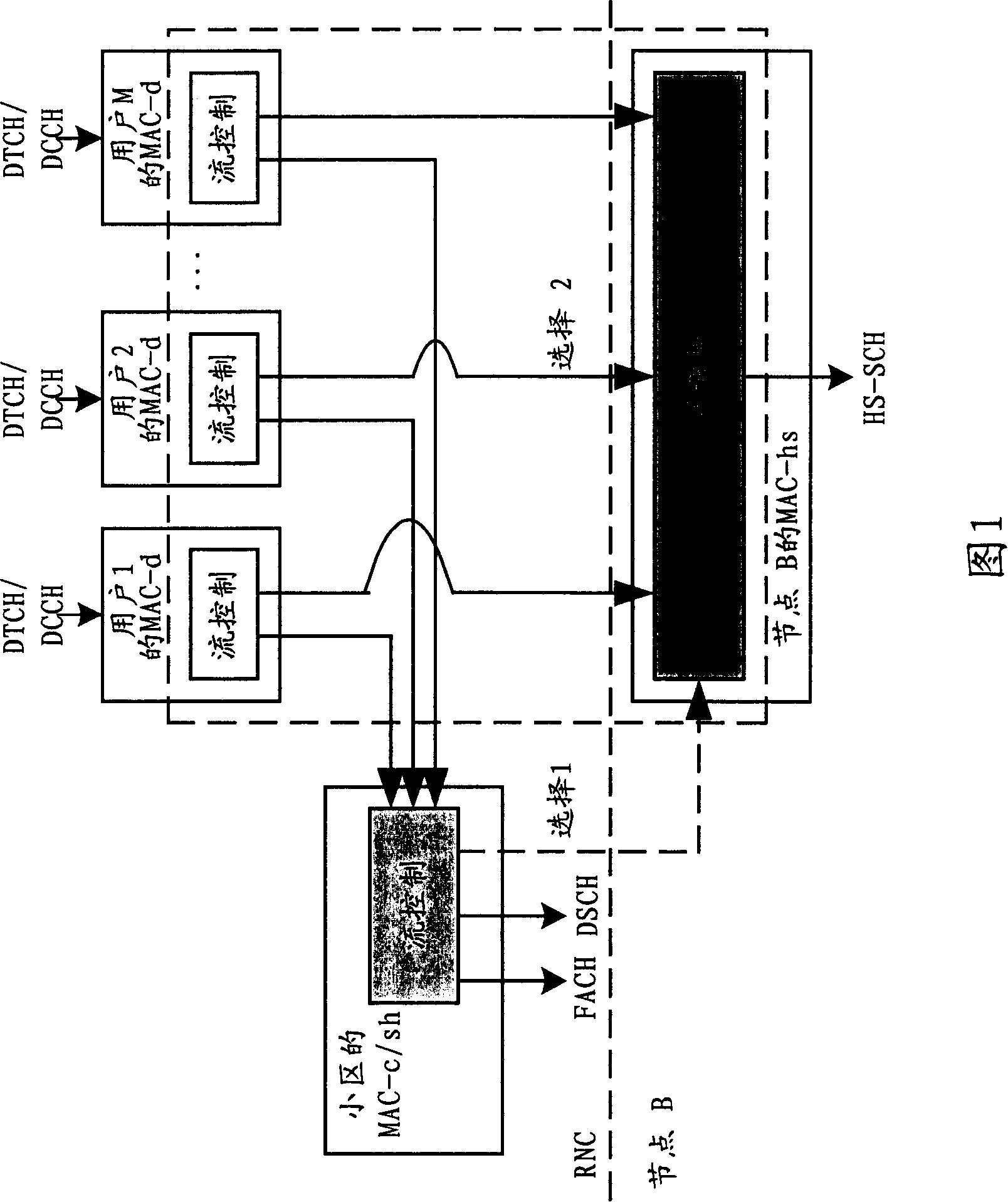

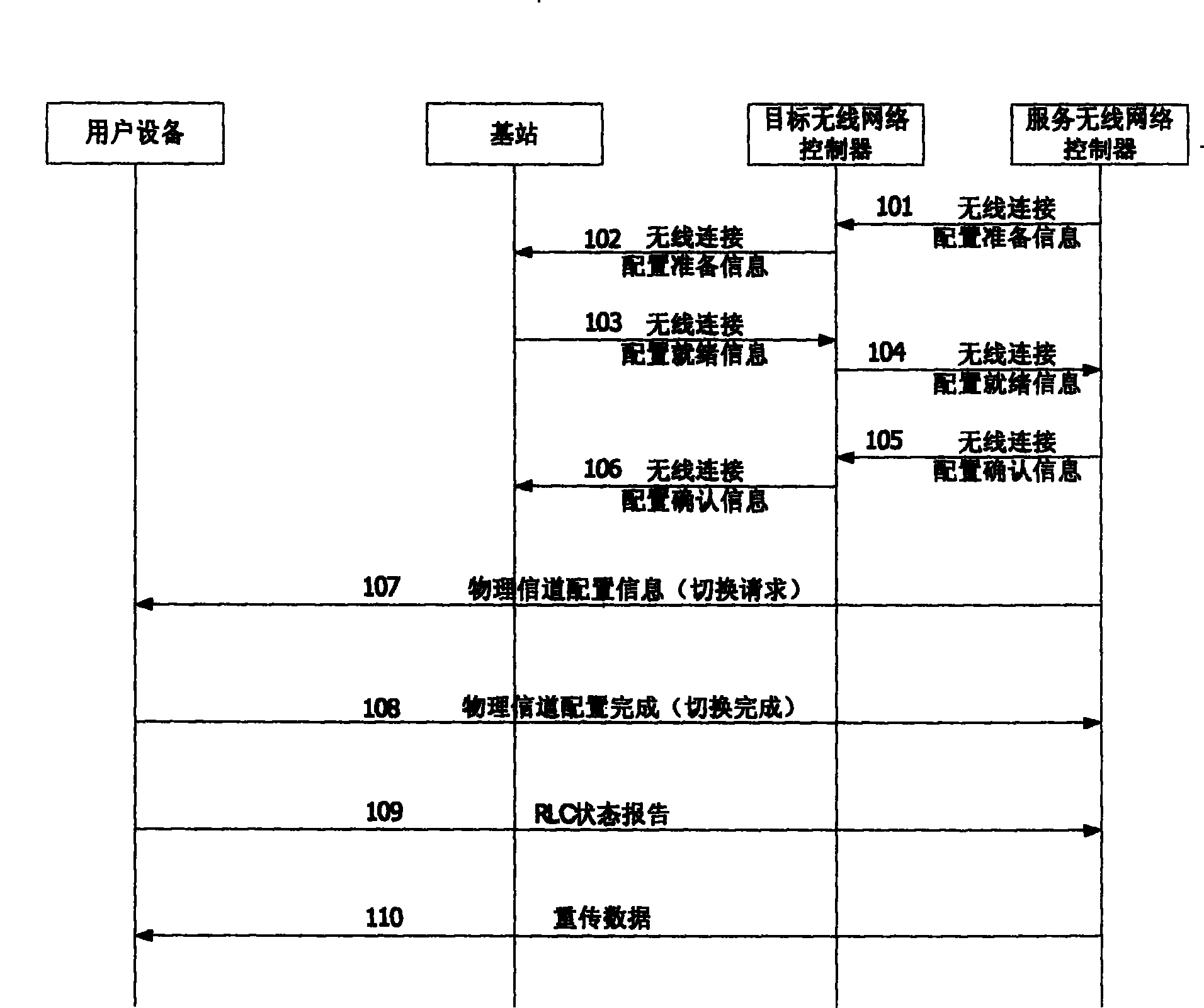

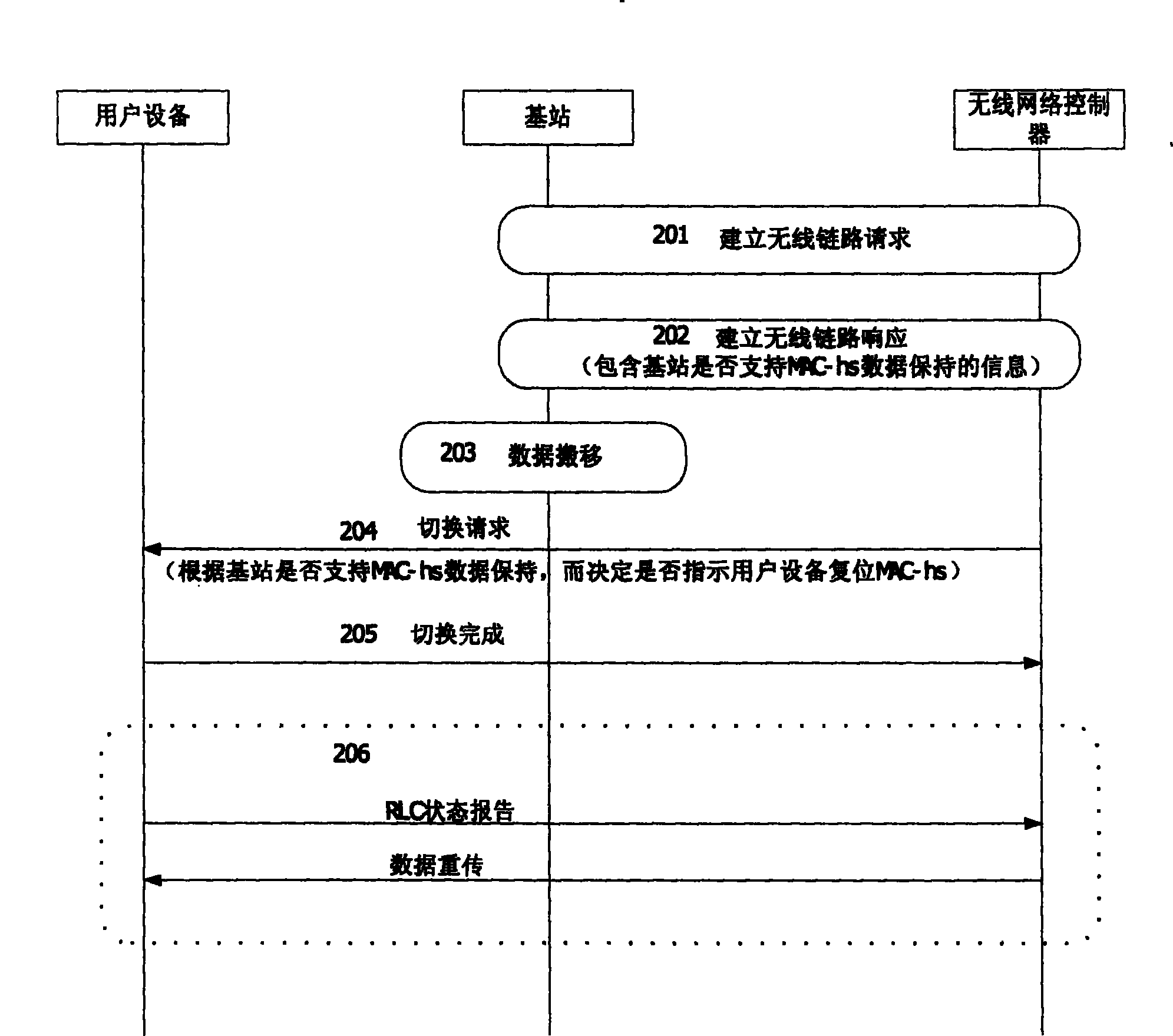

Selection method of data recovery mode and radio network controller

InactiveCN101166344AImprove performanceOptimize transmission delayError prevention/detection by using return channelRadio/inductive link selection arrangementsPreconditionRadio Network Controller

Being applicable to switching HSDPA sector, the method includes steps: RNC corresponding to base station belonging to the subzone obtains whether base station supports data retention of MAC-hs entity; RNC initiates switching request on user equipment being in switching subzones; if base station supports data retention of MAC-hs entity, then the switching request does not contain indication for resetting MAC-hs entity; otherwise, the switching request contains indication for resetting MAC-hs entity. Obtaining information whether base station supports data retention of MAC-hs entity or not, the invention makes RNC possible to select two modes for recovering data. In precondition that known base station supports data retention of MAC-hs entity, the method prefers this mode in order to improve data transmission time delay in aerial port, and raise efficiency of using aerial port. The invention also discloses a wireless network controller.

Owner:TD TECH COMM TECH LTD

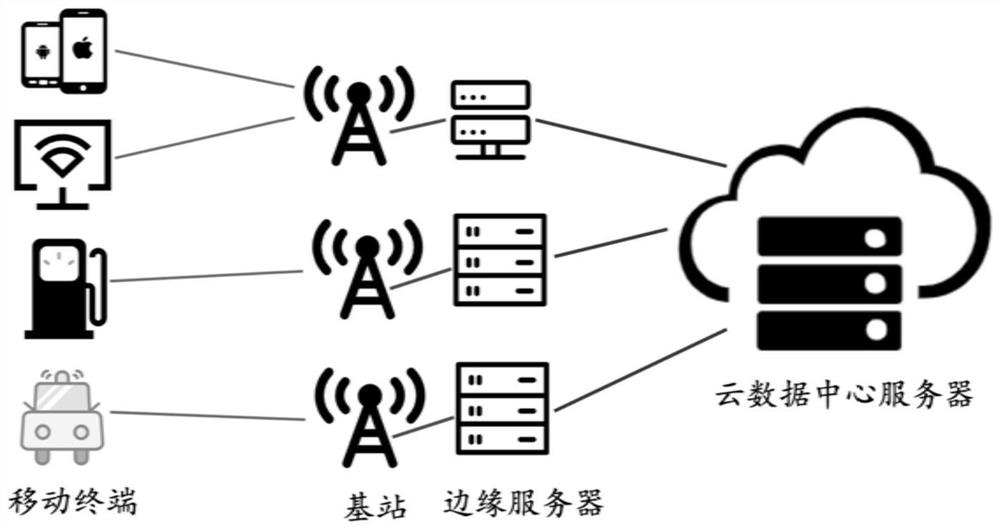

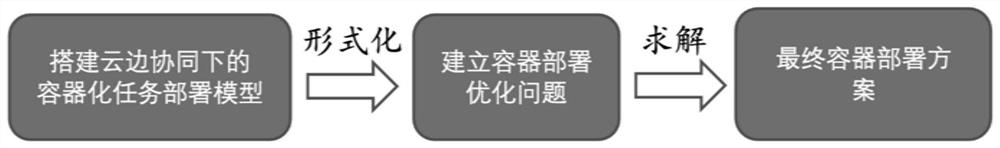

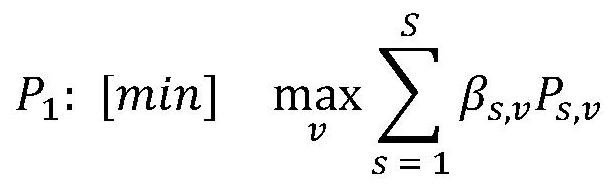

Low-delay containerized task deployment method and device based on cloud edge collaboration

ActiveCN113301151AImprove deployment efficiencyImprove execution performanceEnergy efficient computingData switching networksDeployment timeEdge node

The invention discloses a low-delay containerized task deployment method and device based on cloud edge collaboration, and the method comprises the steps: building a containerized task deployment model in a cloud edge collaboration scene, and representing the bandwidth from a mobile terminal to an edge node and a cloud data center and the deployment cost of a container mirror image layer, wherein the response time delay of the containerized task is subjected to formalized analysis which specifically comprises task transmission time delay, container mirror image deployment time delay and task execution time delay, and an optimization problem of response time delay minimization is established; and relaxing the optimization problem into a linear programming problem, and using a container deployment algorithm designed based on a random rounding technology to complete the deployment of a containerized task. According to the method, the containerized task is processed in parallel based on the cloud edge collaboration scene, so that the aim of optimizing the response time delay of the containerized task is fulfilled.

Owner:NANJING UNIV

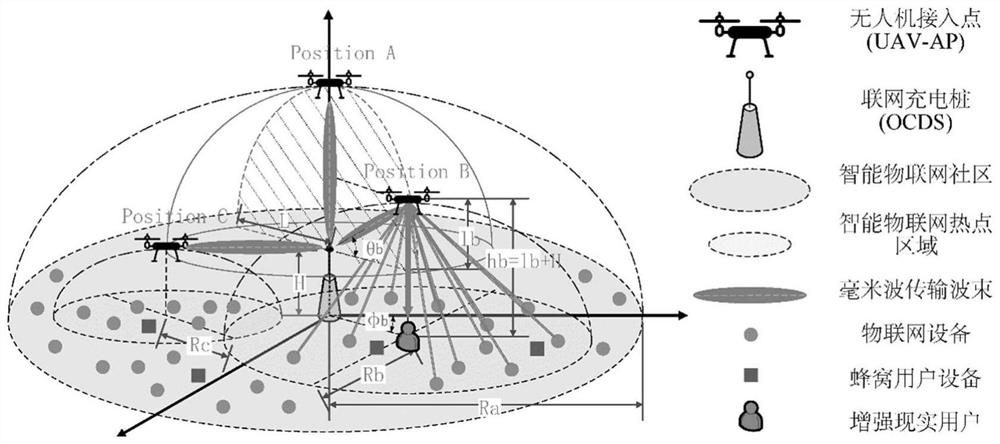

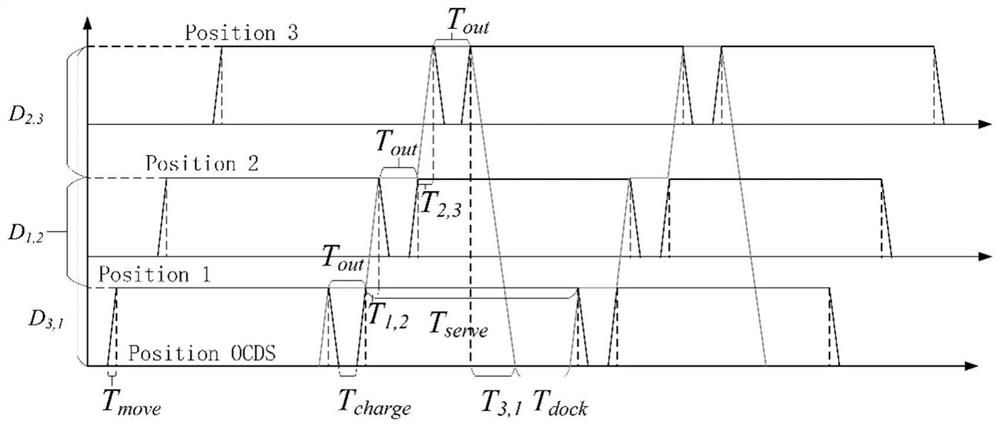

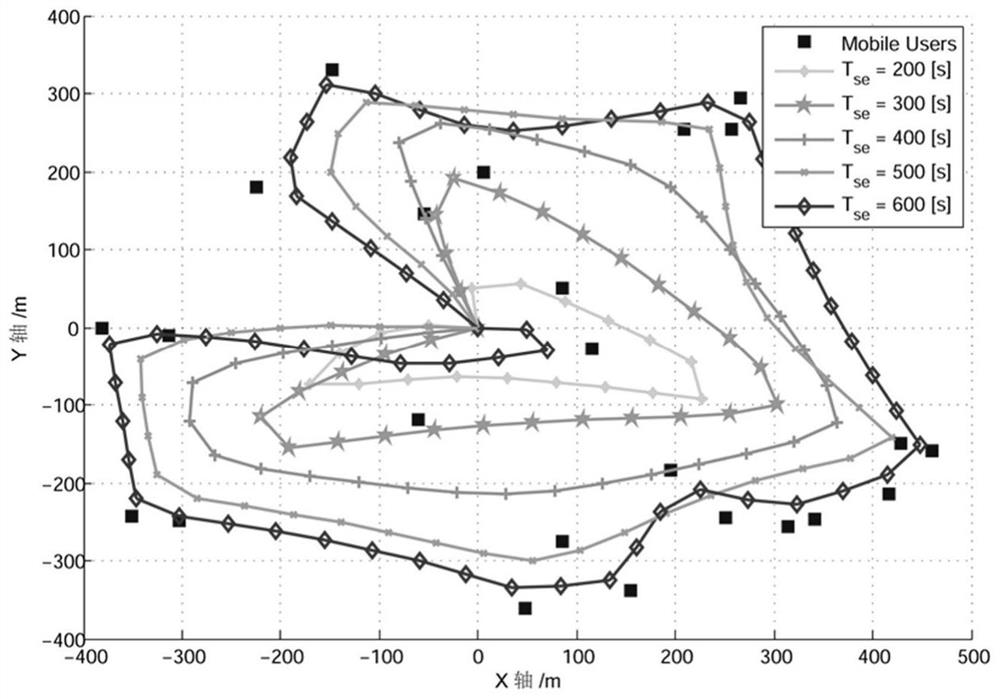

Ground-air full-coverage power control and protocol design method based on centralized array antenna

InactiveCN113259946ADelayed Broadband Media ServicesOptimize processing latencyRadio transmissionHigh level techniquesProtocol designTransmitted power

The invention discloses a ground-air full-coverage power control and protocol design method based on a centralized array antenna. According to the method, three-dimensional layouts and cruise trajectories of two unmanned aerial vehicles are optimized, the transmitting power of ground machine communication equipment is adjusted at the same time, two different convex approximation methods are combined, an original non-convex system energy efficiency optimization problem is converted into a convex problem, and optimal solution is achieved. The hovering height and the transmitting power of the unmanned aerial vehicle are reasonably set, the ground internet of things can firstly converge scene sensing data to a small access point coverage range, high-speed data uploading is achieved by fully utilizing the access bandwidth of a cellular network, and meanwhile energy consumption generated by large-range cruising of the unmanned aerial vehicle is avoided. According to the method, a space data compression process and an energy domain multi-antenna cooperative transmission process are creatively combined to realize high-energy-efficiency transmission, and an optimal parameter configuration scheme is found through experiments. The invention also provides a multi-unmanned aerial vehicle joint scheduling mechanism to guide the optimization process of the cruise trajectory of the unmanned aerial vehicle.

Owner:XI AN JIAOTONG UNIV

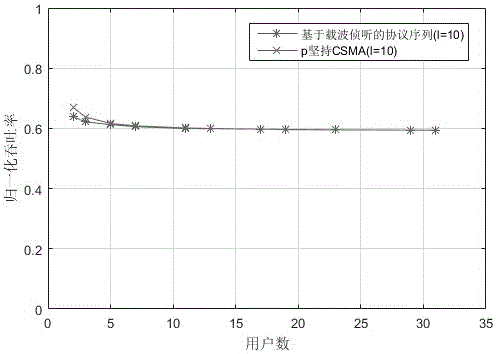

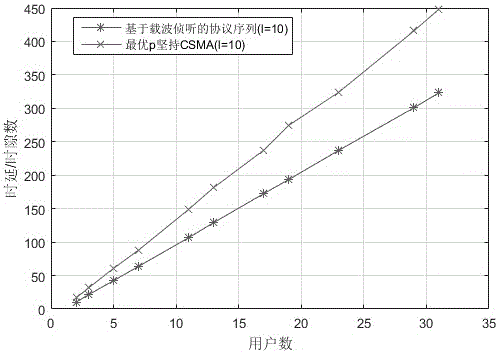

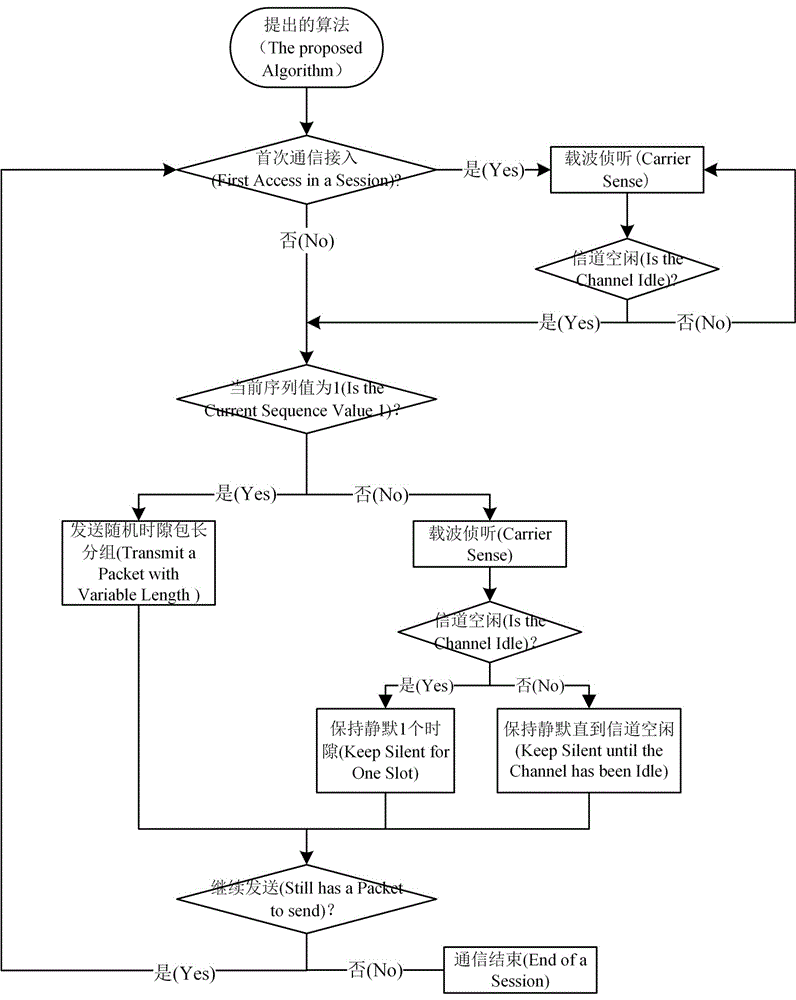

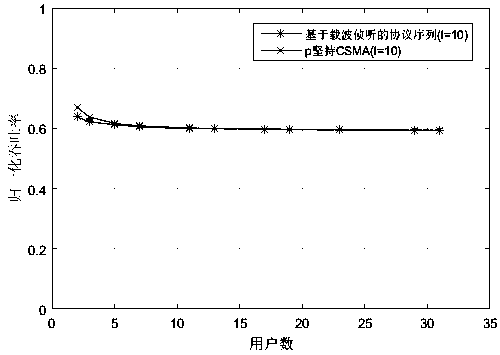

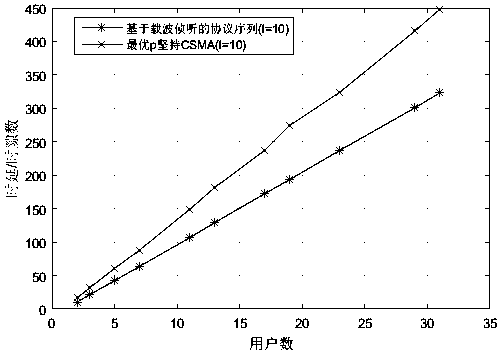

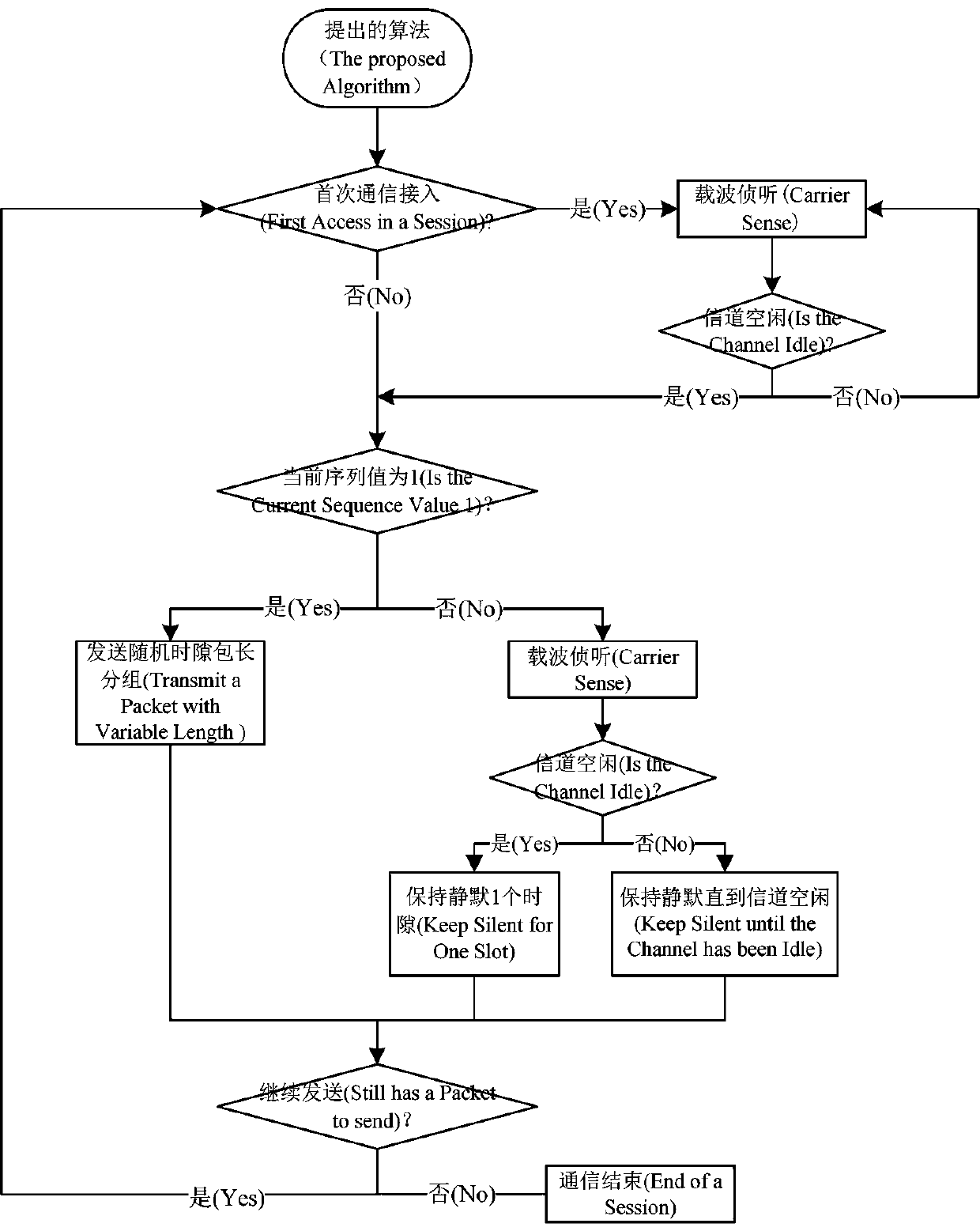

Protocol sequence channel access algorithm based on carrier interception

ActiveCN106658749AGuaranteed synchronicityImprove channel utilizationSynchronisation arrangementCarrier signalTime delays

The invention proposes a protocol sequence channel access algorithm based on carrier interception. The algorithm comprises the steps: firstly distributing a binary protocol sequence to each network node, and reading the sequence values sequentially; secondly transmitting a data group with a non-fixed length when the current sequence value is one, and determining the moment of keeping silent according to a channel interception result when the current sequence value is zero. Compared with a conventional protocol sequence channel access mechanism, the method is more suitable for a network scene comprising various types of data businesses. Moreover, the time delay performance is remarkably superior to a p-persistence CSMA channel access mechanism.

Owner:NANJING UNIV OF SCI & TECH

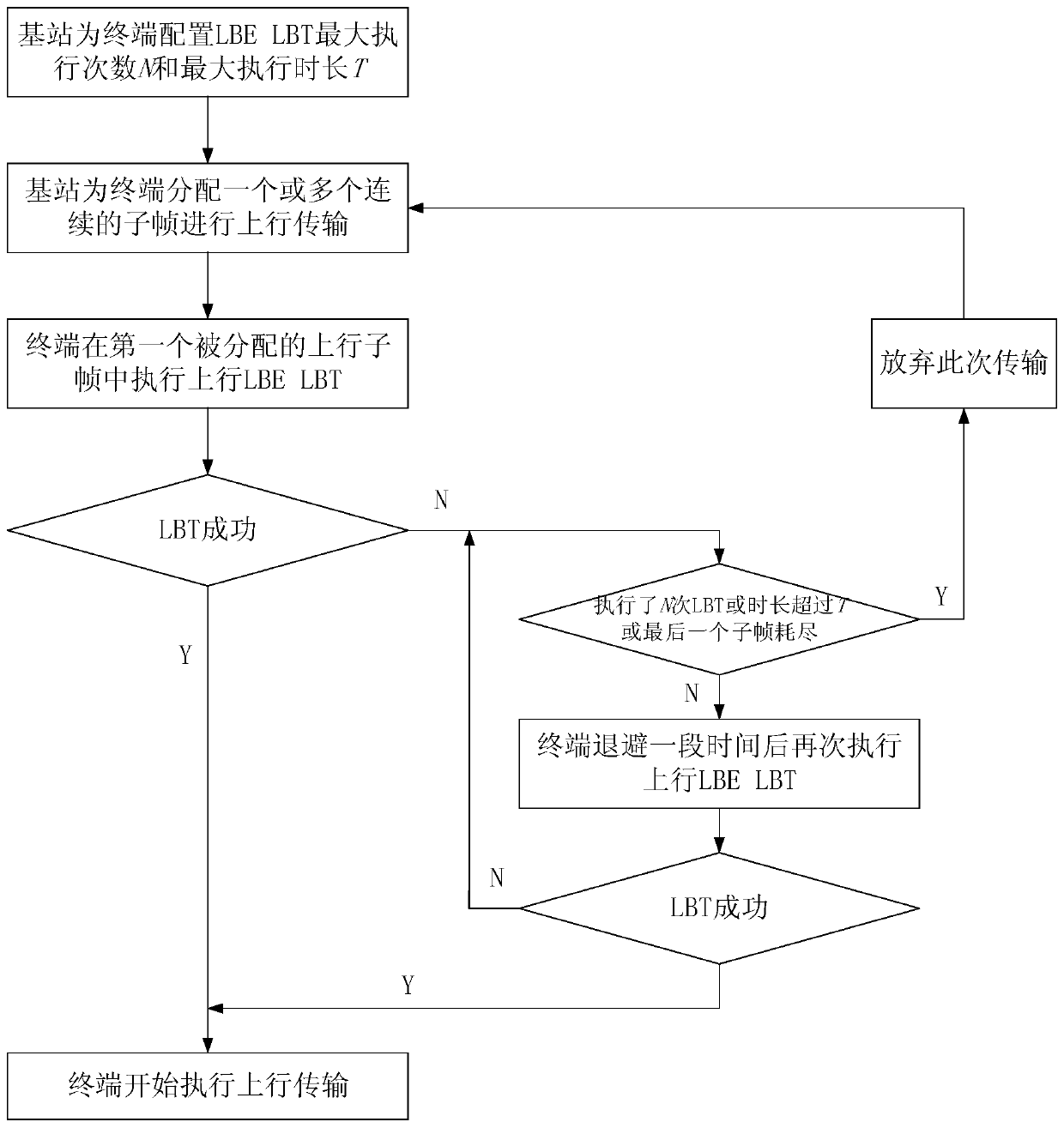

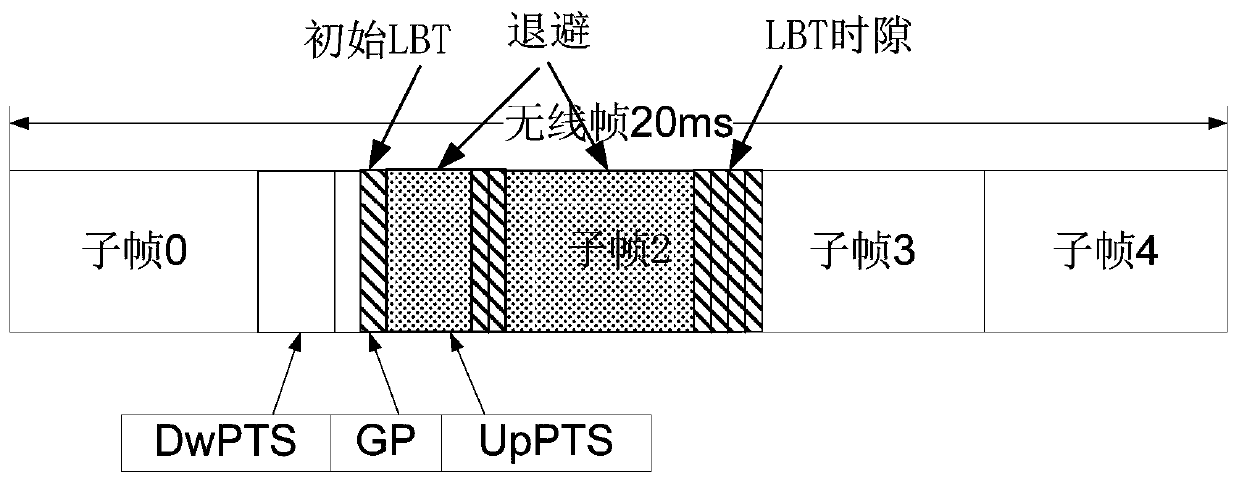

Listen-before-talk parameter configuration method for load-based equipment

InactiveCN109982432AOptimize transmission delayFrequent transmissionWireless communicationComputer terminalResource allocation

The invention relates to a listen-before-talk parameter configuration method for load-based equipment, and the method comprises the steps: enabling a base station to configure the LBE LBT maximum execution frequency N and / or the LBE LBT maximum execution duration T for a terminal; and each time when the base station executes uplink resource allocation, the frequency of executing the LBE LBT by theterminal does not exceed the maximum execution frequency N of the LBE LBT, and / or the total time length of executing the LBE LBT by the terminal does not exceed the maximum execution time length T ofthe LBE LBT. According to the invention, the LBE LBT parameters are reasonably configured for the terminal, the delay requirements of different services and the energy consumption requirements of different terminals are met, the method can adapt to a complex dynamic interference environment, and the transmission performance of the system is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

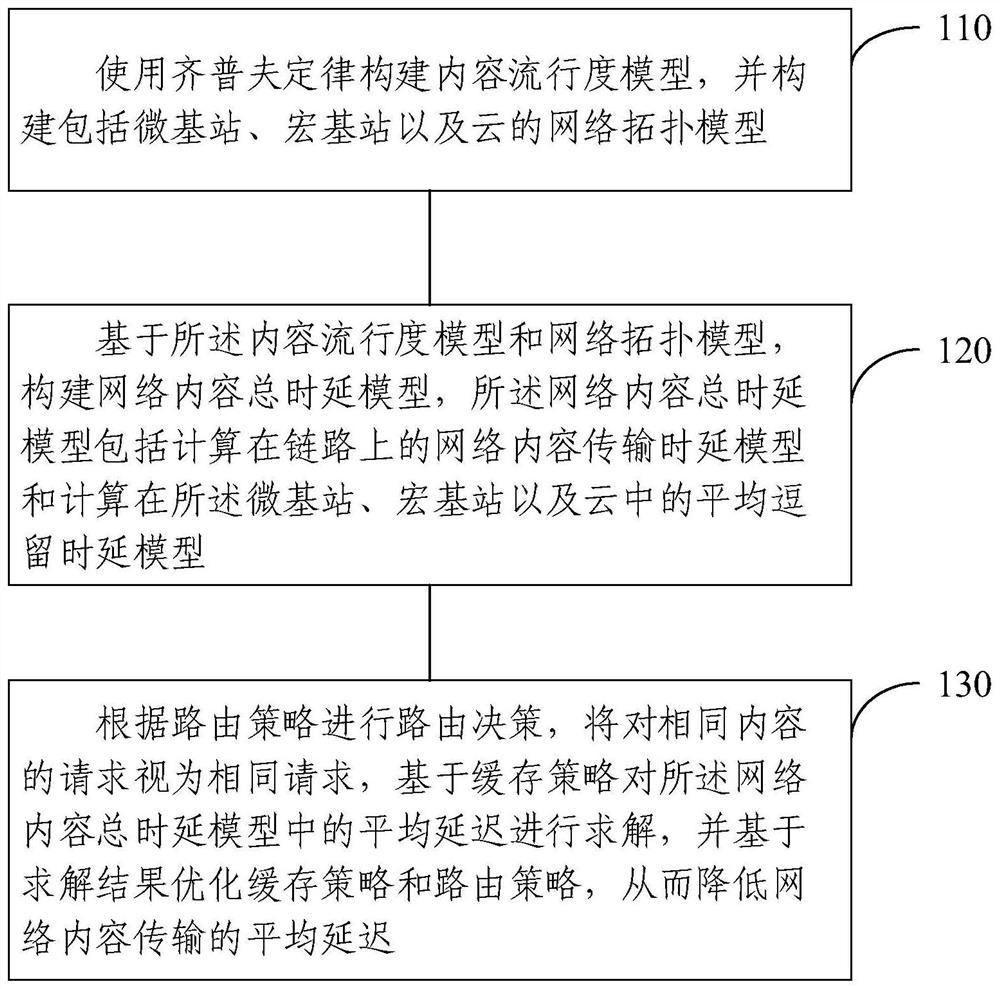

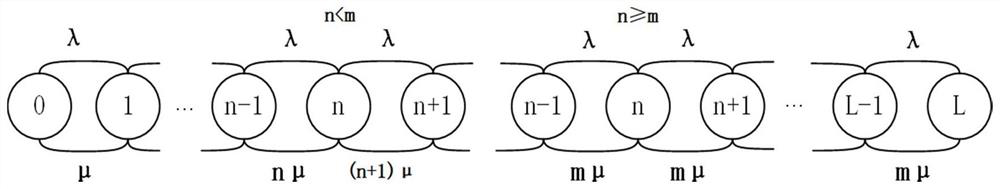

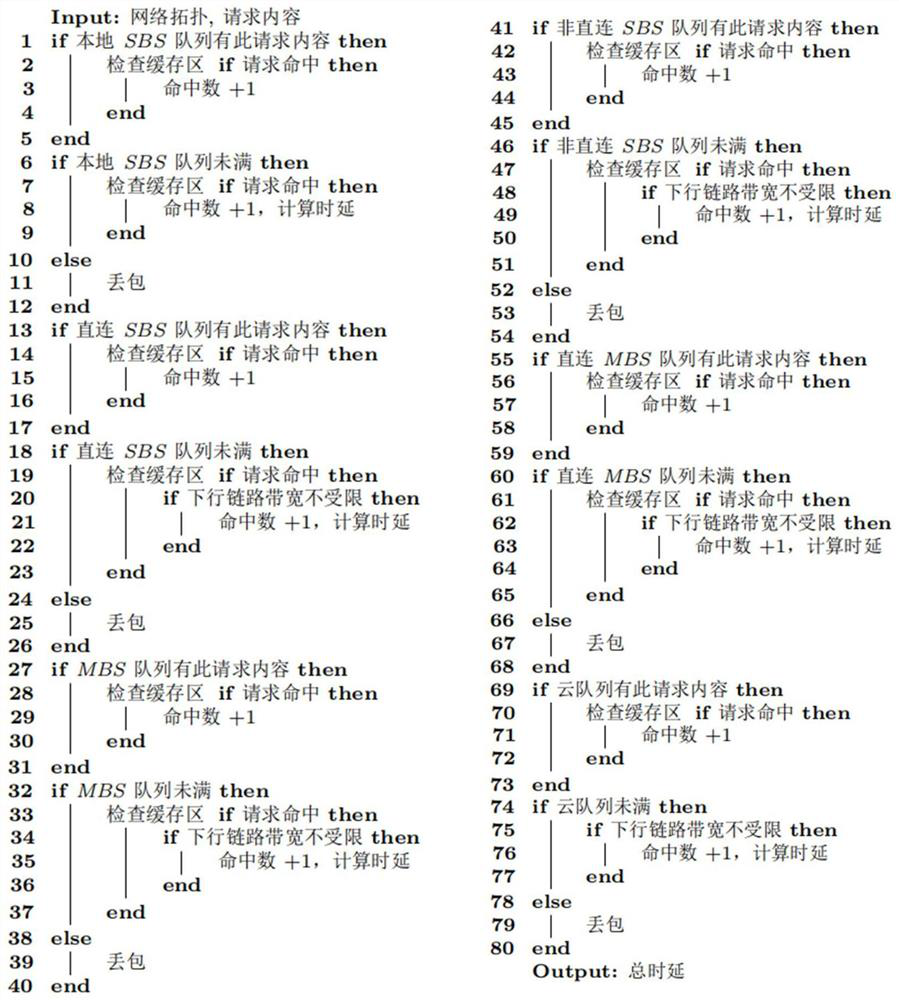

Low-delay network content transmission method and device, electronic equipment and medium

PendingCN113766540AReduce delivery pressureOptimize transmission delayWireless communicationContent distributionMacro base stations

The invention provides a low-delay network content transmission method, device and equipment and a medium, and the method comprises the steps: constructing a content popularity model through employing the Zipf's law, and constructing a network topology model comprising a micro base station, a macro base station and cloud; constructing a network content total time delay model, wherein the network content total time delay model comprises a model for calculating network content transmission time delay on a link and a model for calculating average stay time delay in the micro base station, the macro base station and the cloud; performing a routing decision according to a routing strategy, regarding requests for the same content as the same request, solving the average delay in the network content total delay model based on a caching strategy, and optimizing caching and the routing decision based on a solving result. The convergence effect of the same content is considered to reduce the utilization rate of the server, so the network content transmission delay is optimized, the network content distribution efficiency is improved, and the network transmission pressure is relieved.

Owner:BEIJING UNIV OF TECH

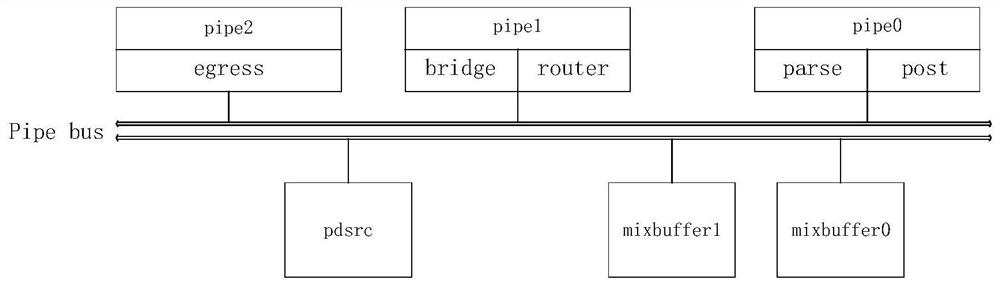

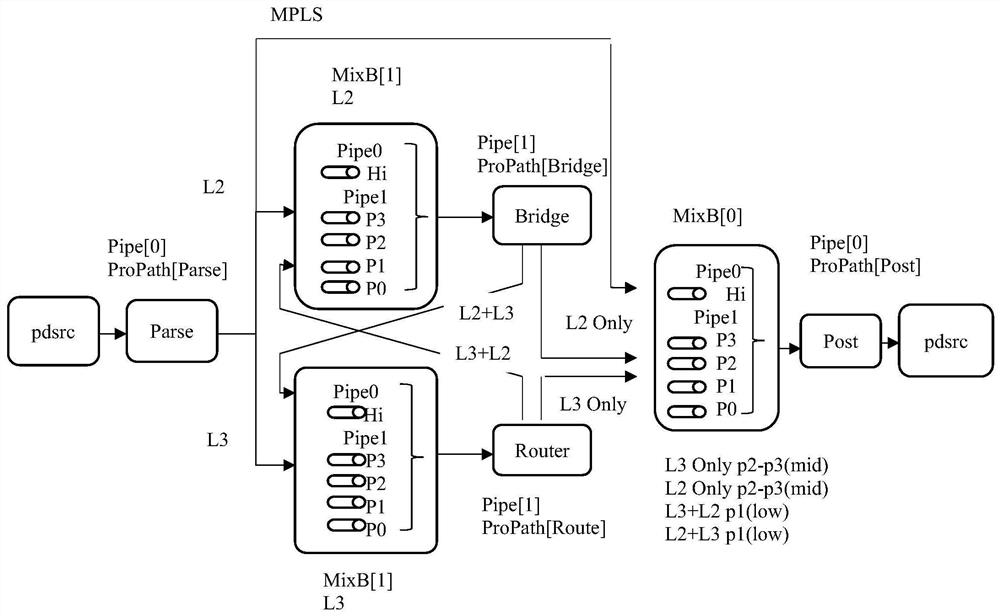

Pipeline scheduling method and device

ActiveCN111884948AReduce latencyOptimize transmission delayProgram initiation/switchingInterprogram communicationParallel computingAssembly line

The invention discloses an assembly line scheduling device, which comprises three physical assembly lines, two mix buffers and a bus pipe bus, and is characterized in that the three physical assemblylines are logically divided into five assembly lines, and the five assembly lines respectively correspond to five stages of processing messages in a chip, i.e., a parse stage, a bridge stage, a routerstage, a post stage and an egress stage; the two mix buffers are used for scheduling different services and then sending the different services to the corresponding logic assembly lines; and each pipeline unit pipe, the mix buffer and the pdsrc are hung on the bus pipe bus and are used for completing the interaction among the pipeline units. According to the invention, various services are optimized in the aspect of assembly line processing length, and different services can correspond to different processing lengths, so that unnecessary processing is reduced; the pipe bus is used for replacing the original connection relationship among the members of the assembly line, so that the members of the assembly line are connected more flexibly, the expandability is very high, and the new requirements in the future can be met. The invention further provides a corresponding assembly line scheduling method.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

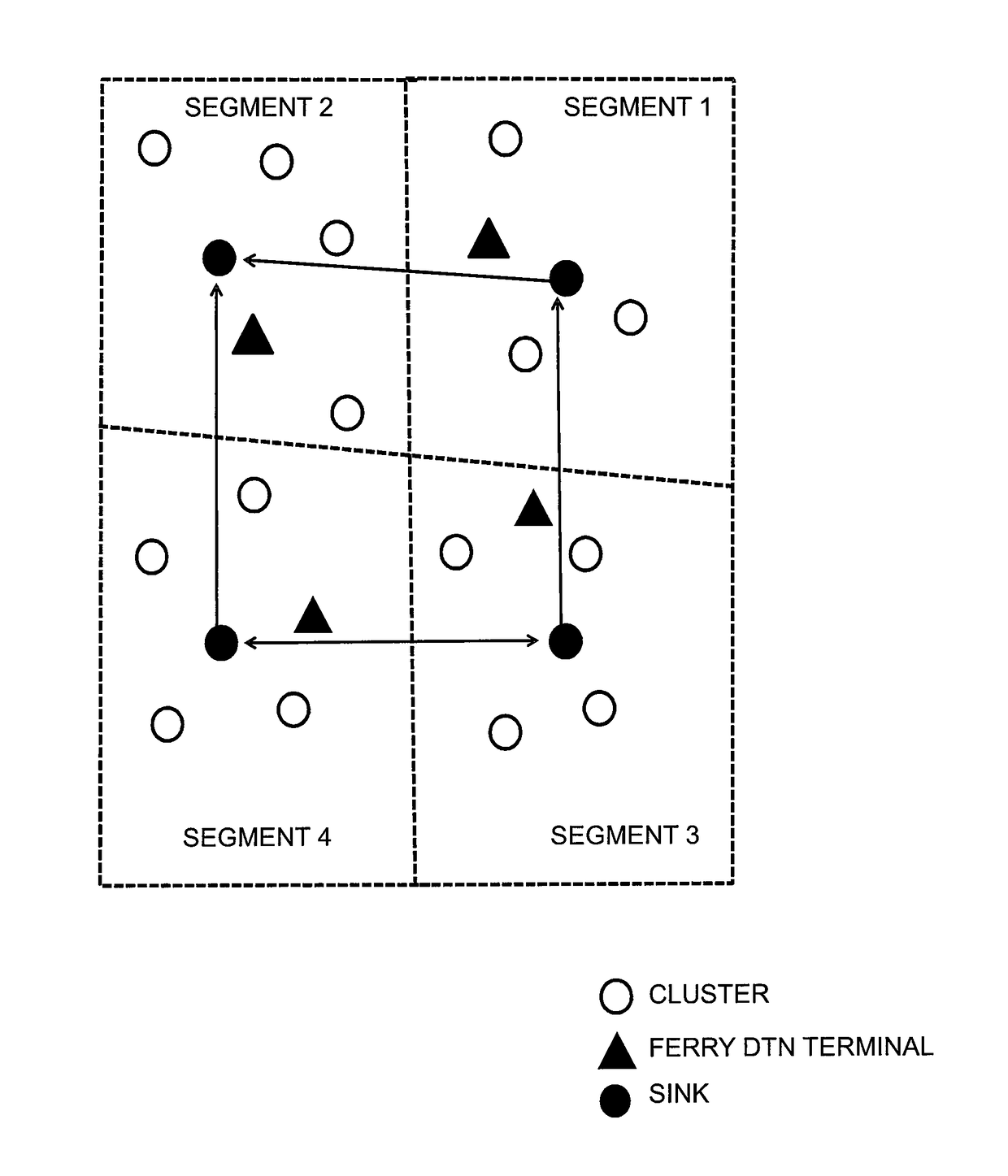

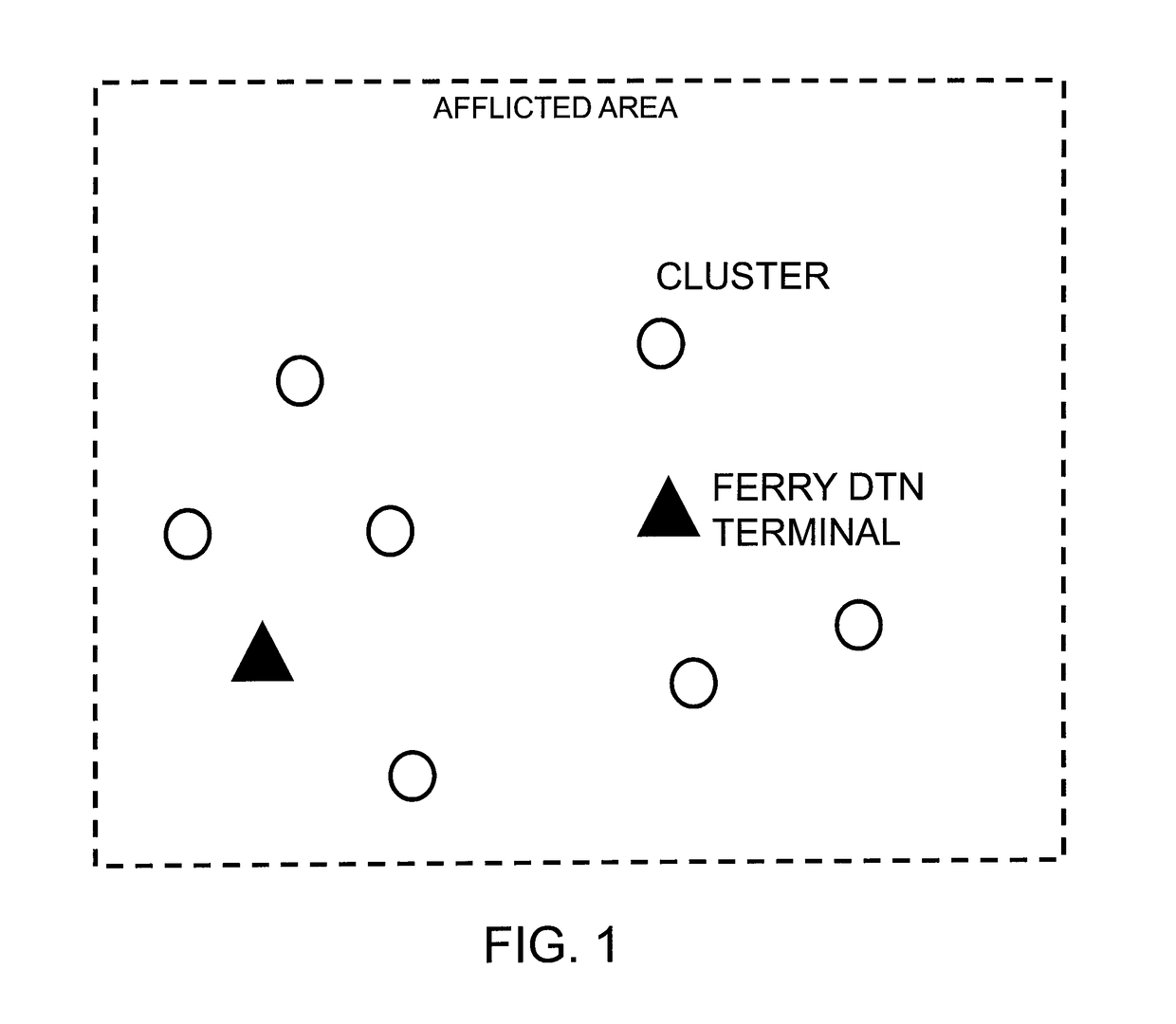

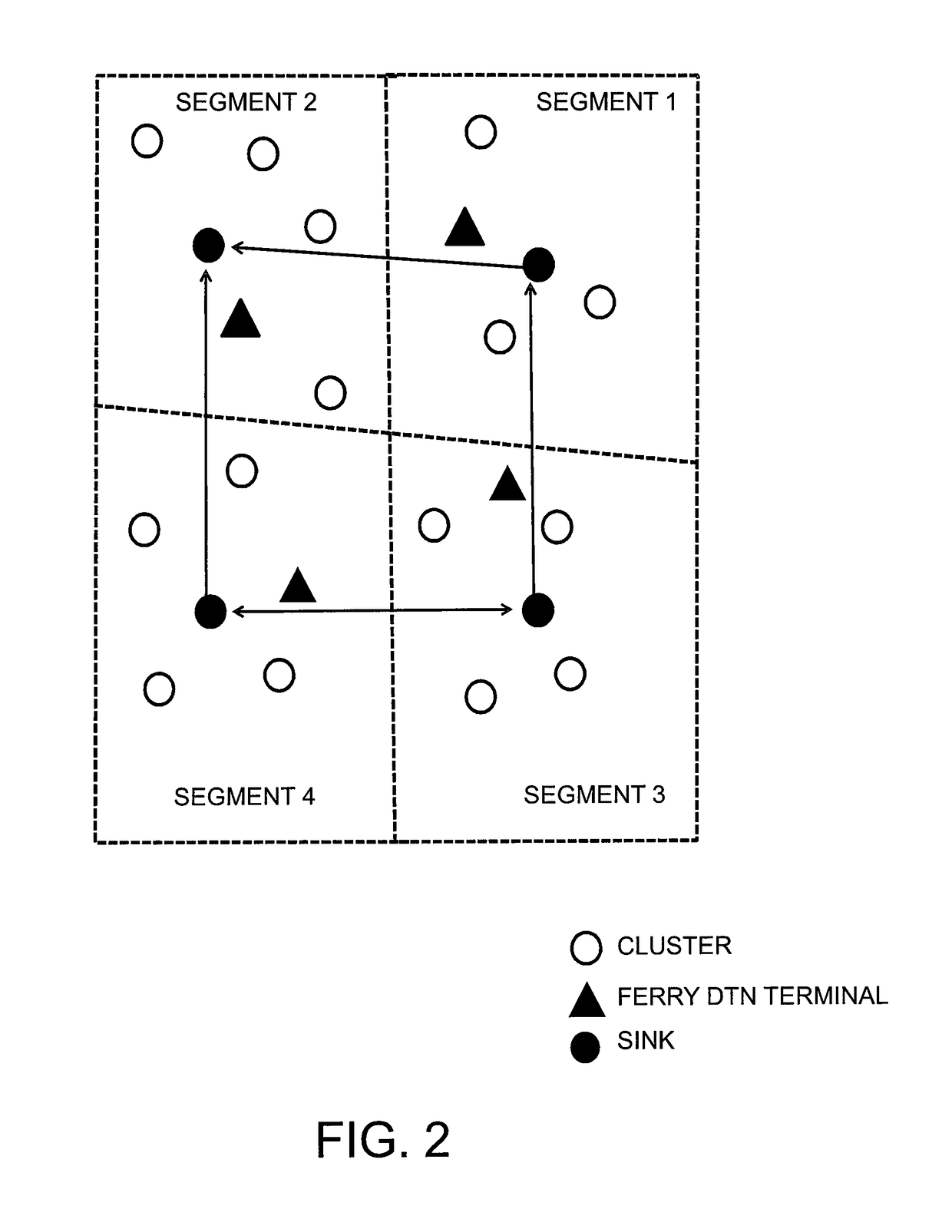

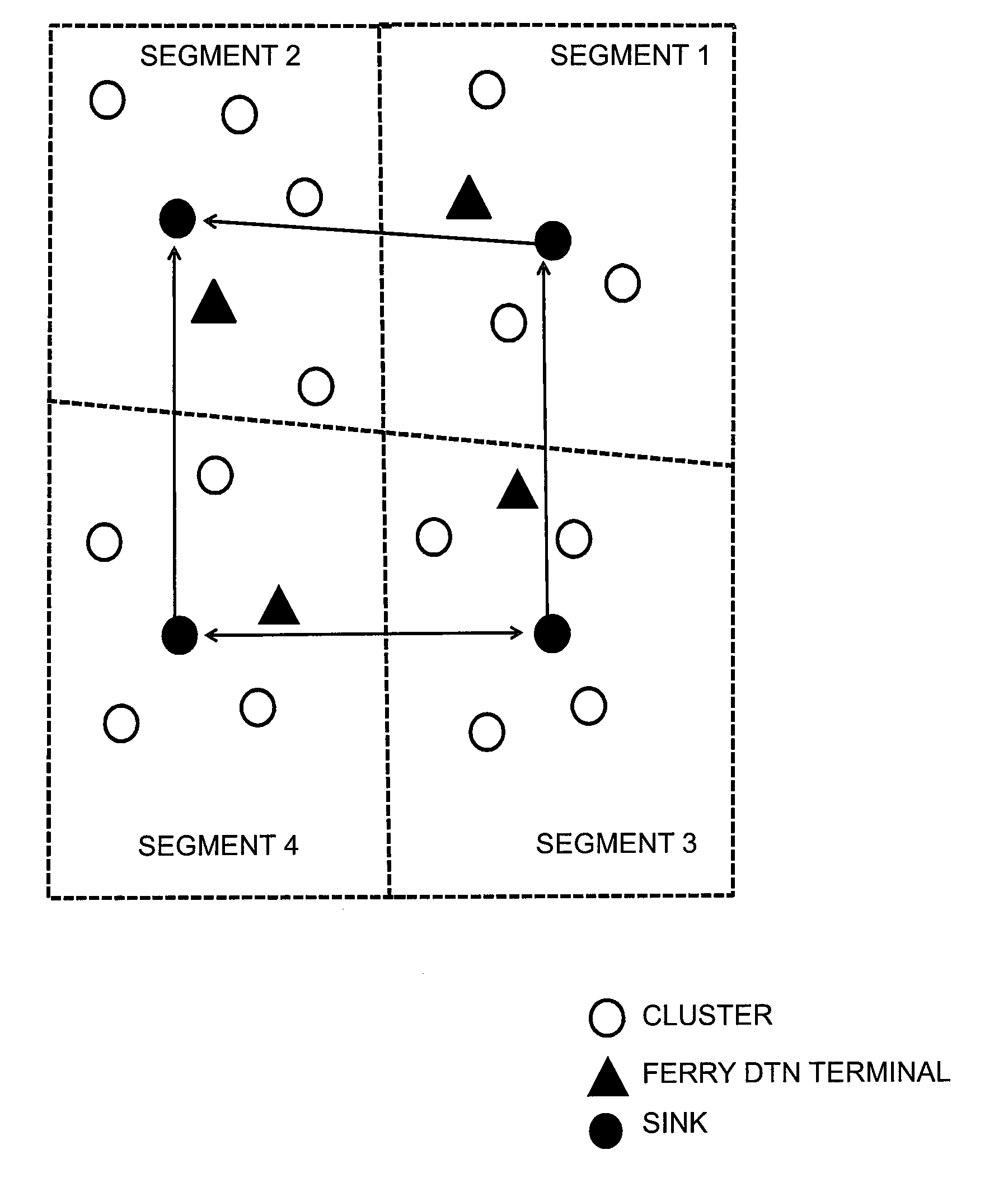

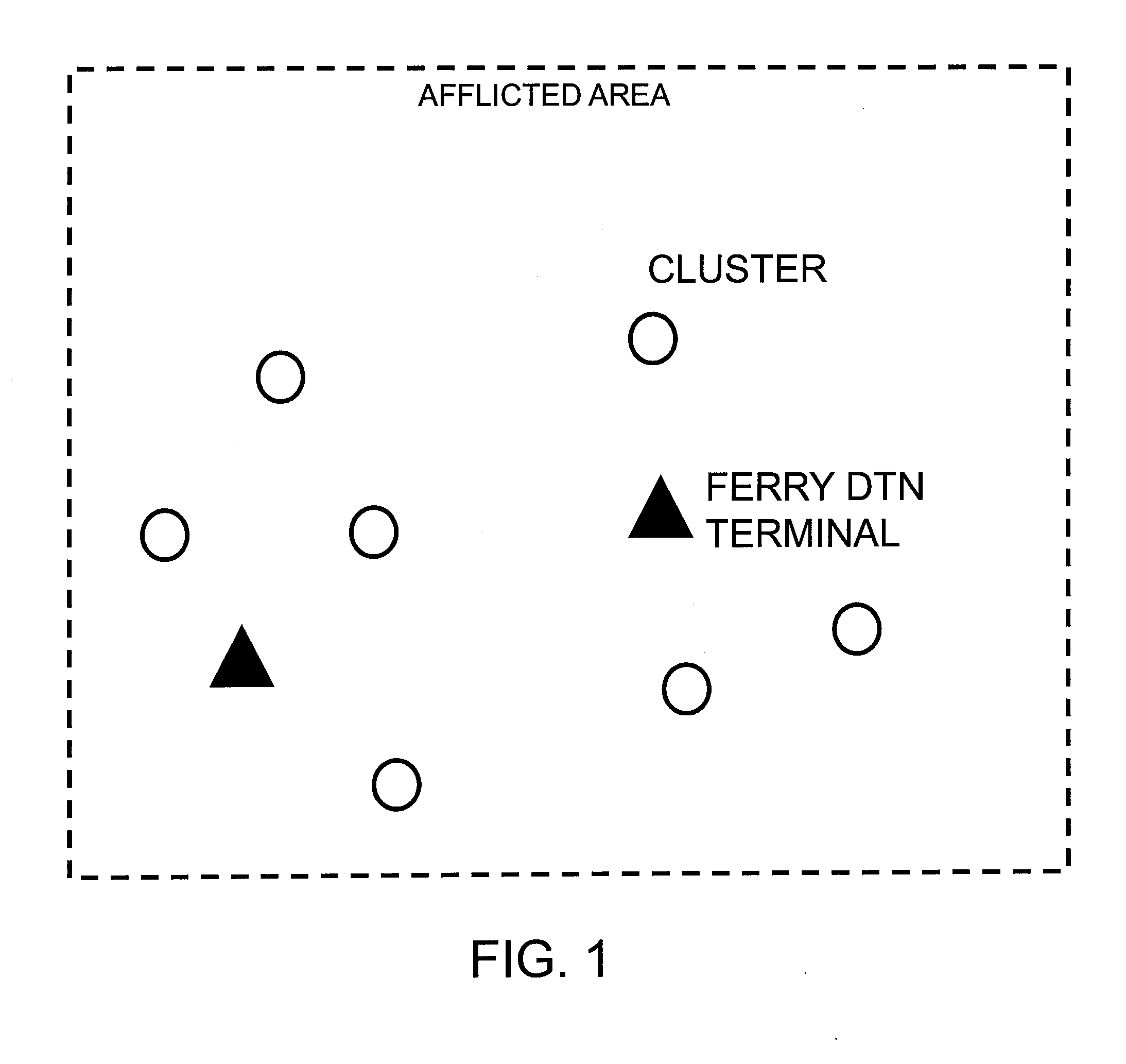

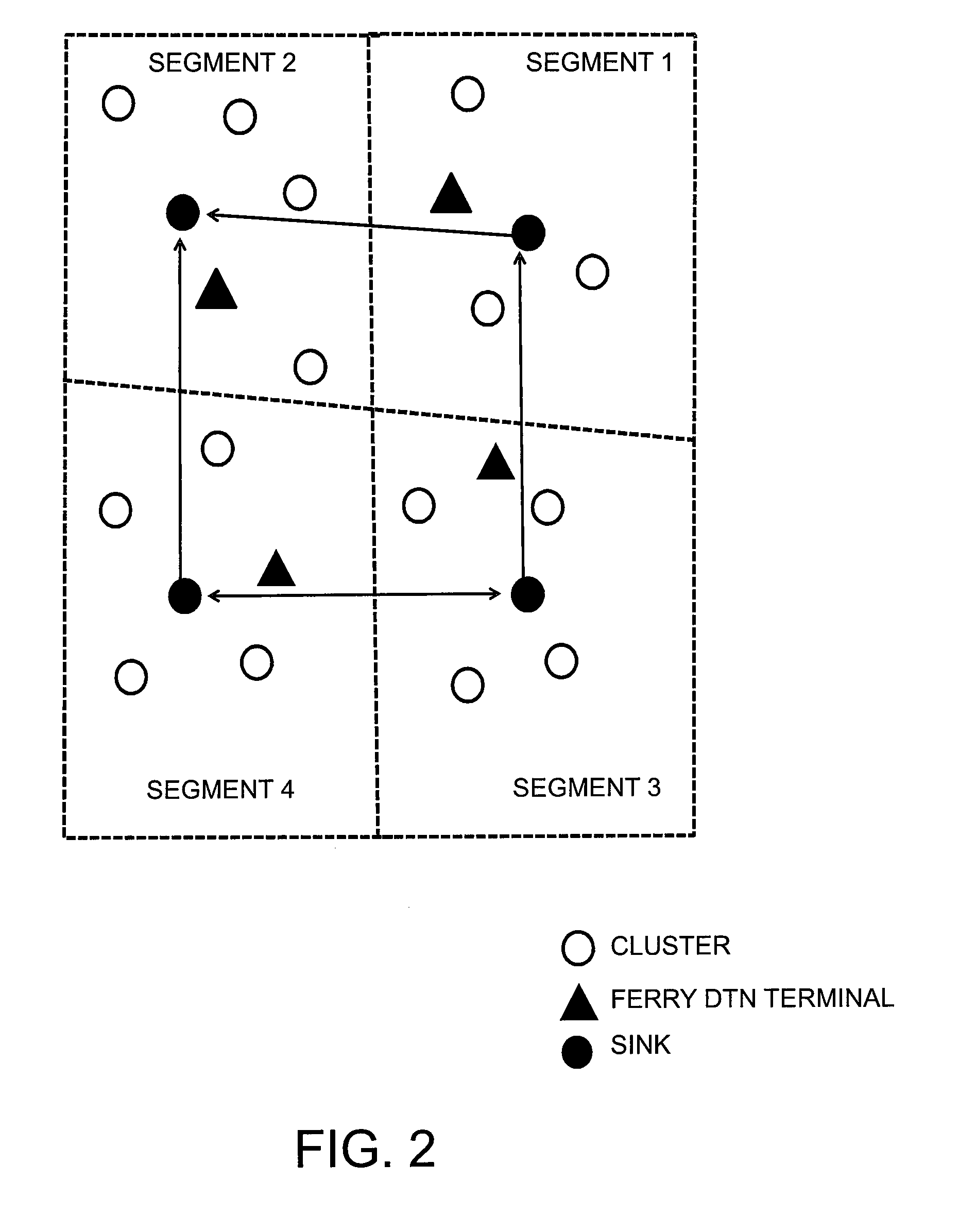

Information transfer device, delay tolerant network, information transmission method, and recording medium

ActiveUS9853887B2Optimize transmission delayReduction of informationNetwork topologiesFault locationCommunication unitInformation transmission

A delay tolerant network is built with the use of a plurality of information transfer devices each of which includes: a communication unit to communicate to and from another device within a communication range that is connected to the information transfer device; and a storing unit to store and keeps collected notification information, and each of which holds delay tolerant communication by exchanging the collected and kept notification information with another device when the exchange becomes possible. Each information transfer device includes a control unit to exchange environment information with another information transfer device, and to execute deriving processing an assigned range that is assigned autonomously to its own information transfer device, based on the environment information that is kept by its own information transfer device, through a planarization search processing in which a value is evened out between its own information transfer device and other information transfer devices.

Owner:NEC CORP +1

Information transfer device, delay tolerant network, information transmission method, and recording medium

ActiveUS20160020996A1Optimize transmission delayReduction of informationError preventionTransmission systemsCommunication unitInformation transmission

A delay tolerant network is built with the use of a plurality of information transfer devices each of which includes: a communication unit to communicate to and from another device within a communication range that is connected to the information transfer device; and a storing unit to store and keeps collected notification information, and each of which holds delay tolerant communication by exchanging the collected and kept notification information with another device when the exchange becomes possible. Each information transfer device includes a control unit to exchange environment information with another information transfer device, and to execute deriving processing an assigned range that is assigned autonomously to its own information transfer device, based on the environment information that is kept by its own information transfer device, through a planarization search processing in which a value is evened out between its own information transfer device and other information transfer devices.

Owner:NEC CORP +1

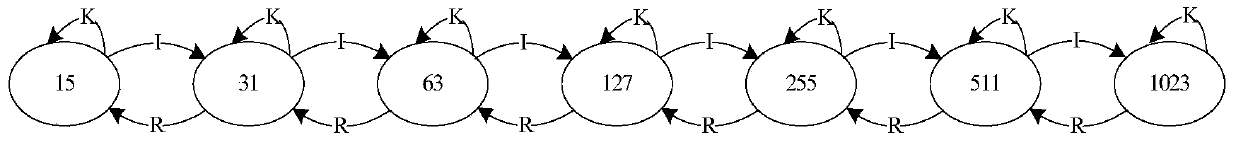

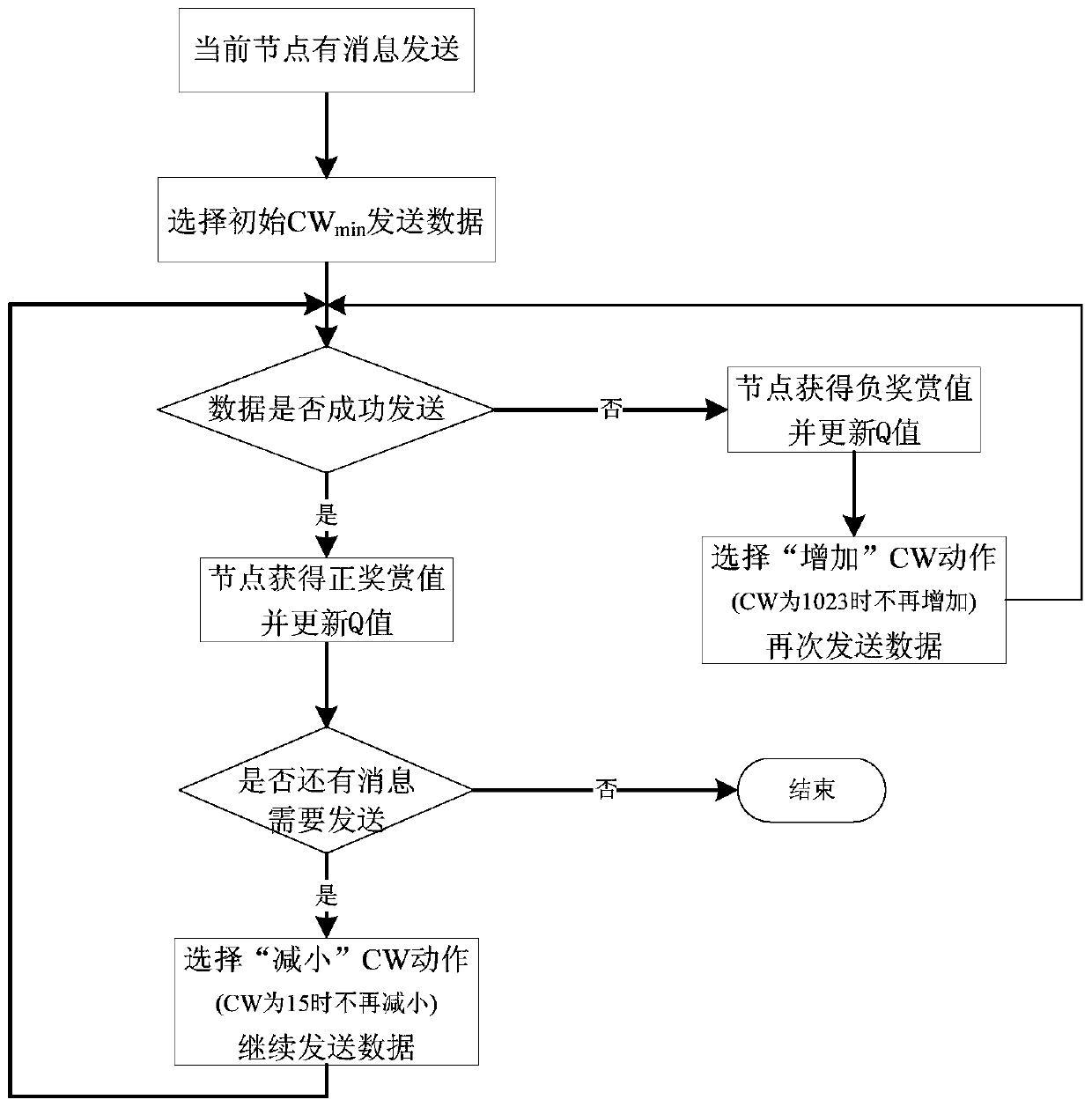

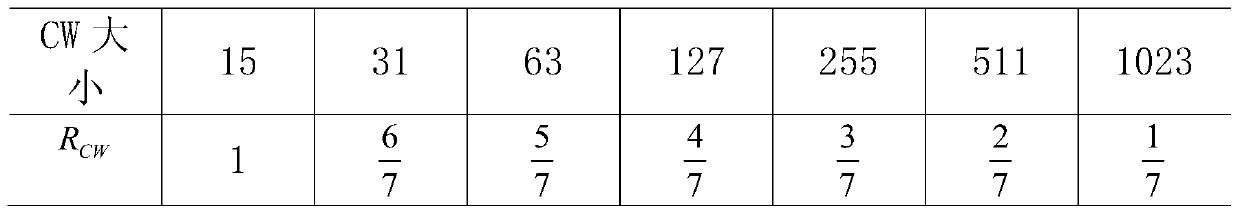

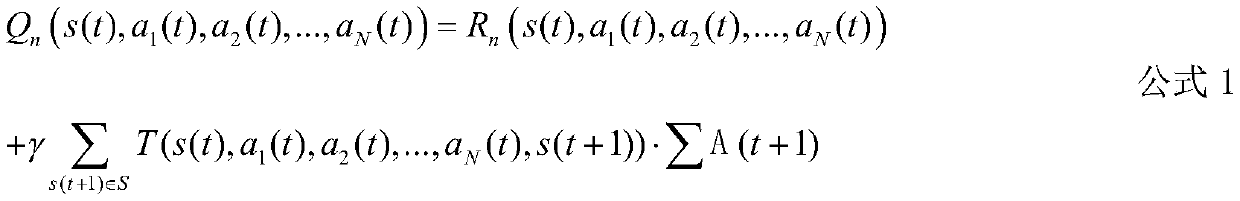

A realization method of mac protocol in vehicle network based on q-learning

ActiveCN105306176BIncrease the probability of successful deliveryReduce the number of dodgesError prevention/detection by using return channelNetwork traffic/resource managementIn vehicleEngineering

Owner:NANJING NANYOU INST OF INFORMATION TECHNOVATION CO LTD

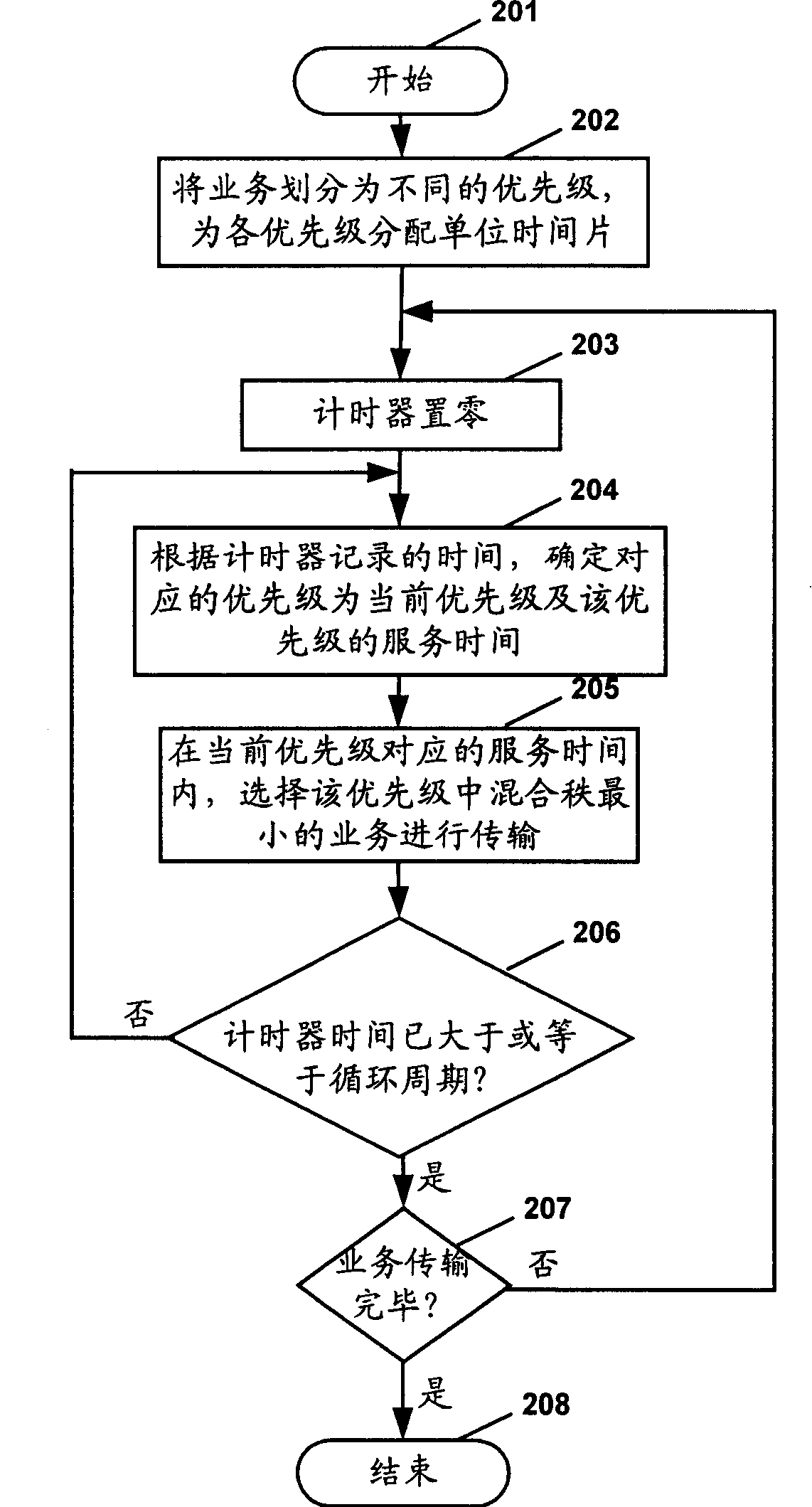

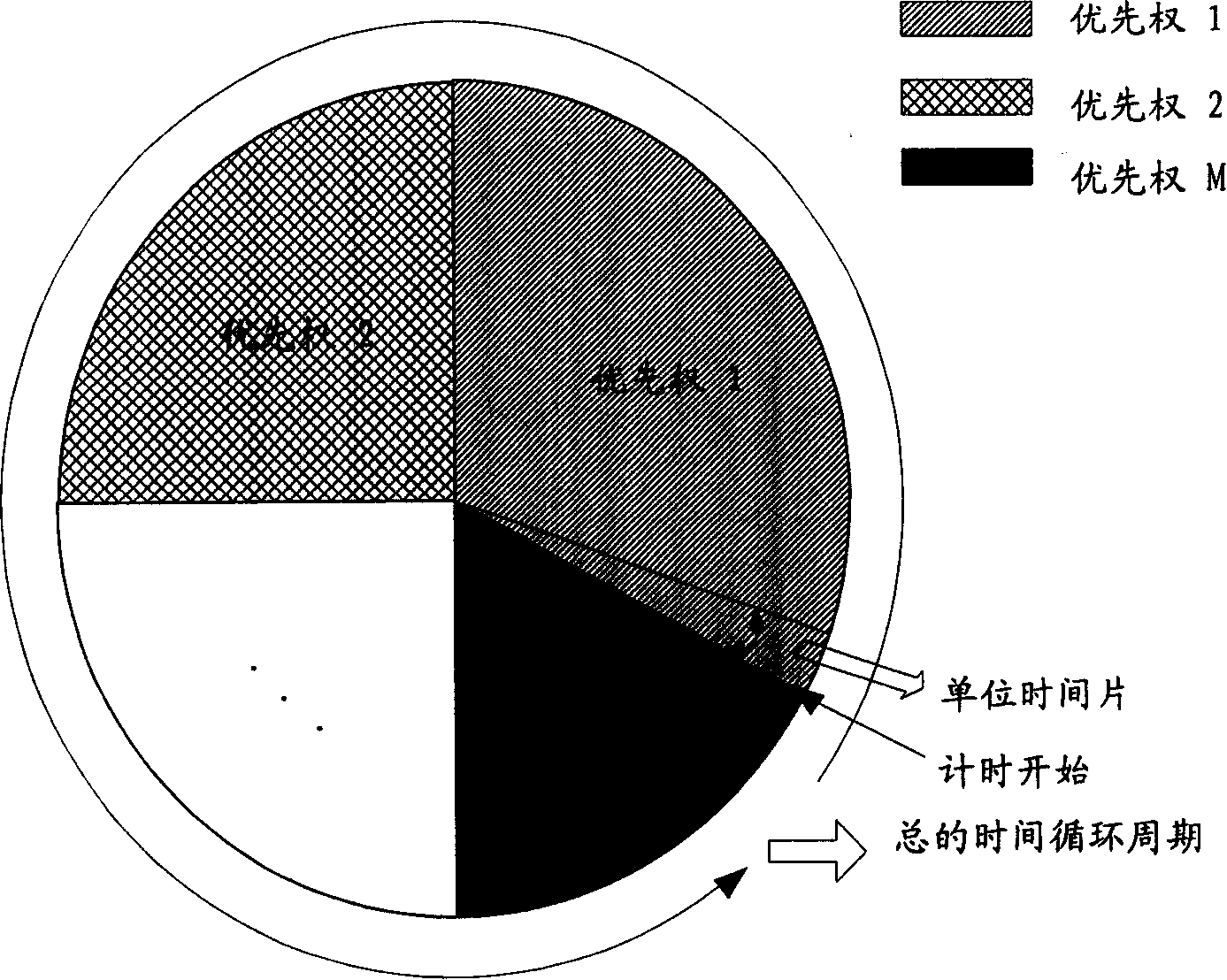

Packet dispatch and flux control method for share transmission channel

ActiveCN1731727BOptimize transmission delayImprove resource utilizationData switching networksTraffic capacityResource utilization

The invention discloses a method for flow controlling and sectionalization dispatching of sharing transmission channel in wireless switch-in network which comprises the steps of: obtaining just ranks and capacity ranks for every business need to be transmitted; obtaining mixing ranks according to the just ranks and capacity ranks; selecting the minimum mixing rank to transmit. Wherein the just ranks reflect the just property of each business; the capacity ranks reflect the capacity property of each business. The inventive method has the advantages of taking regard of the fairness and capacitybetween each business, of improving resource usage of system and transmission rate and delay.

Owner:ALCATEL LUCENT SHANGHAI BELL CO LTD

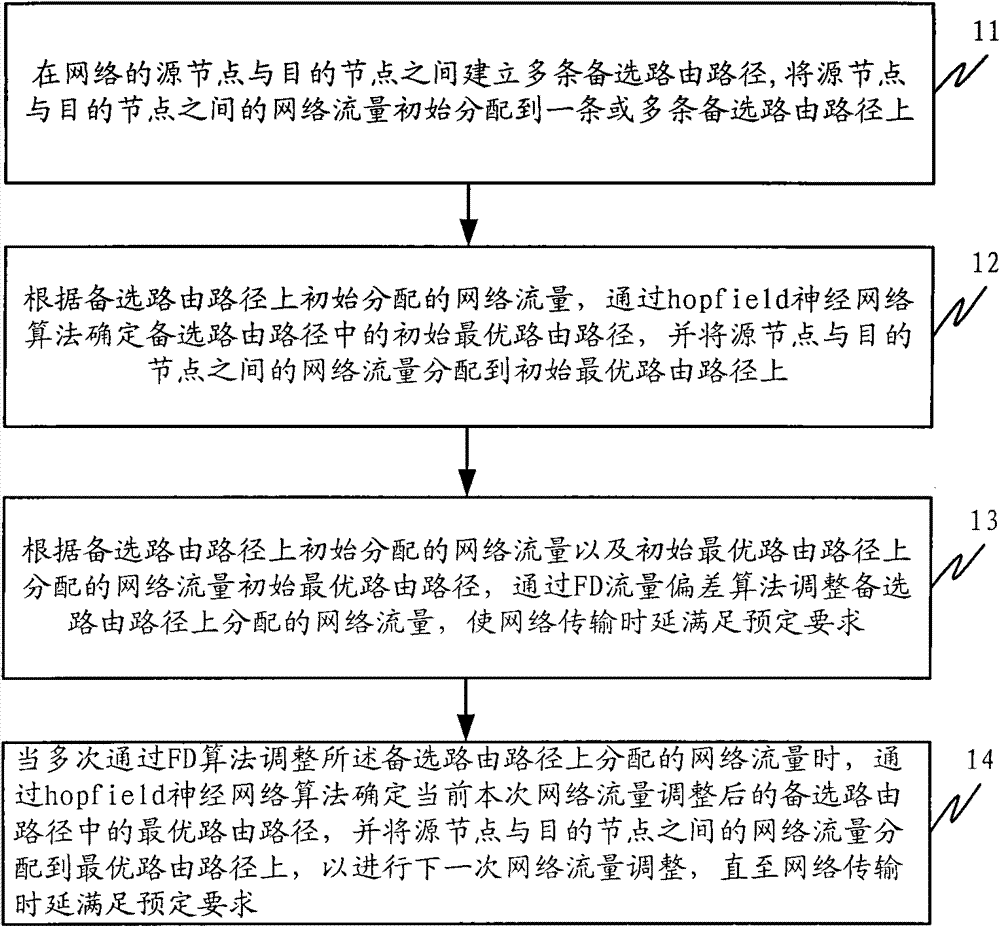

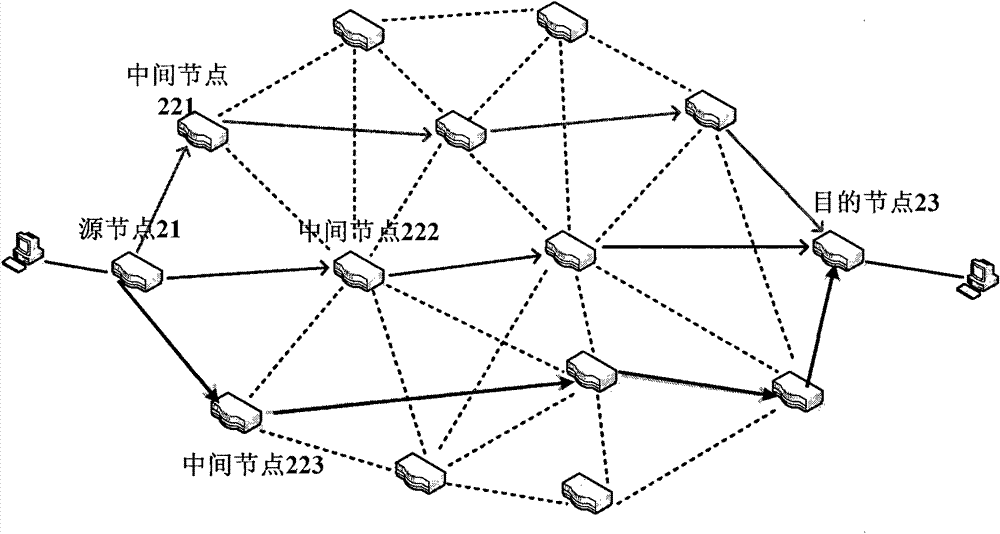

Distribution method of network flow

InactiveCN102025628BOptimize transmission delayData switching networksHopfield networkTransmission time delay

Owner:BEIJING UNIV OF POSTS & TELECOMM

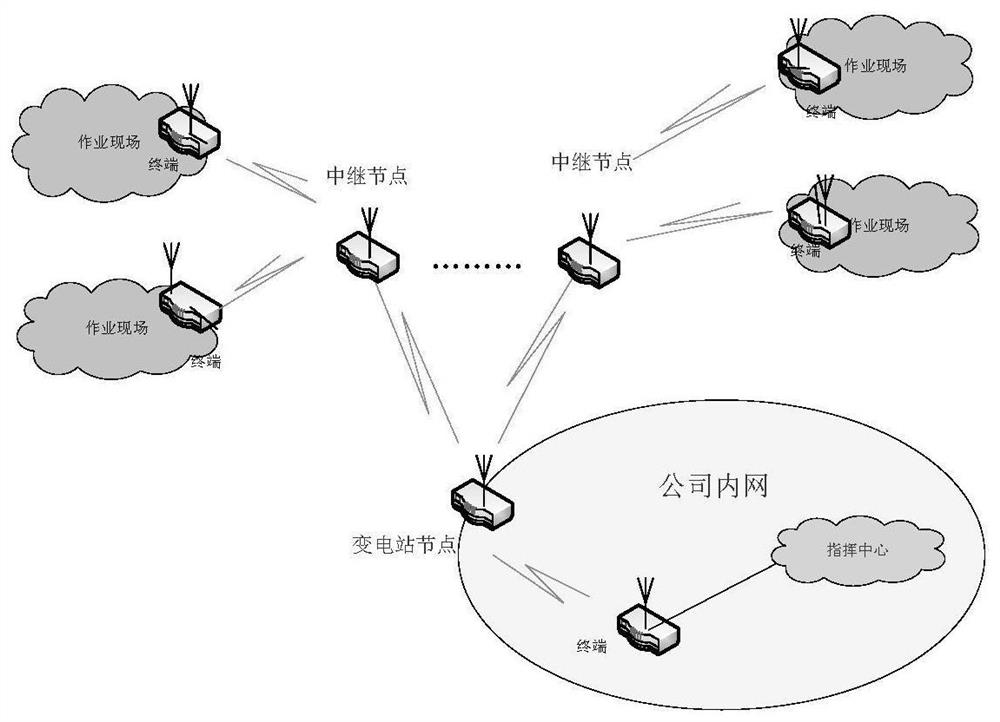

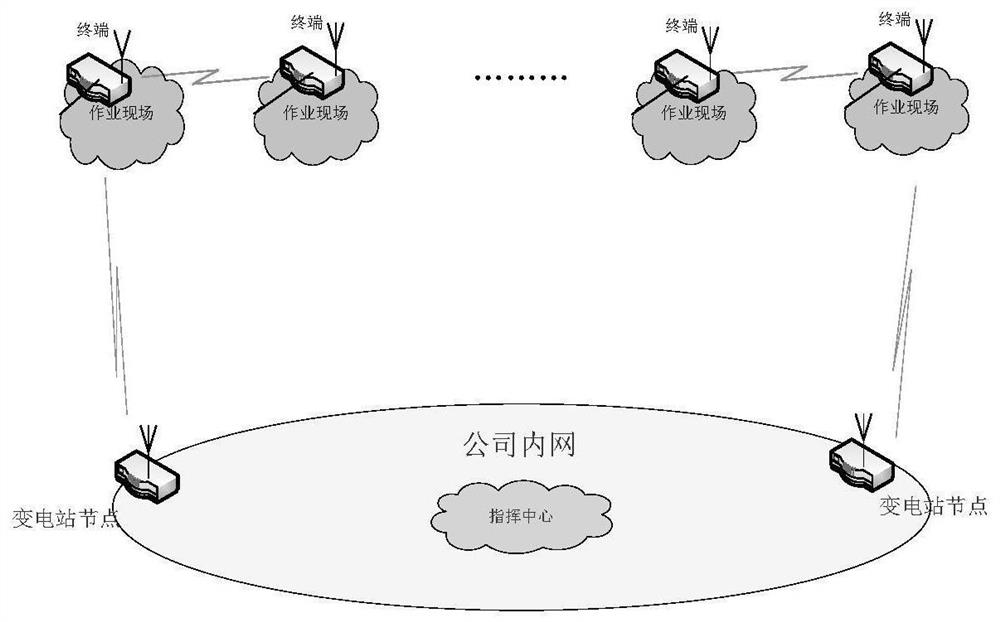

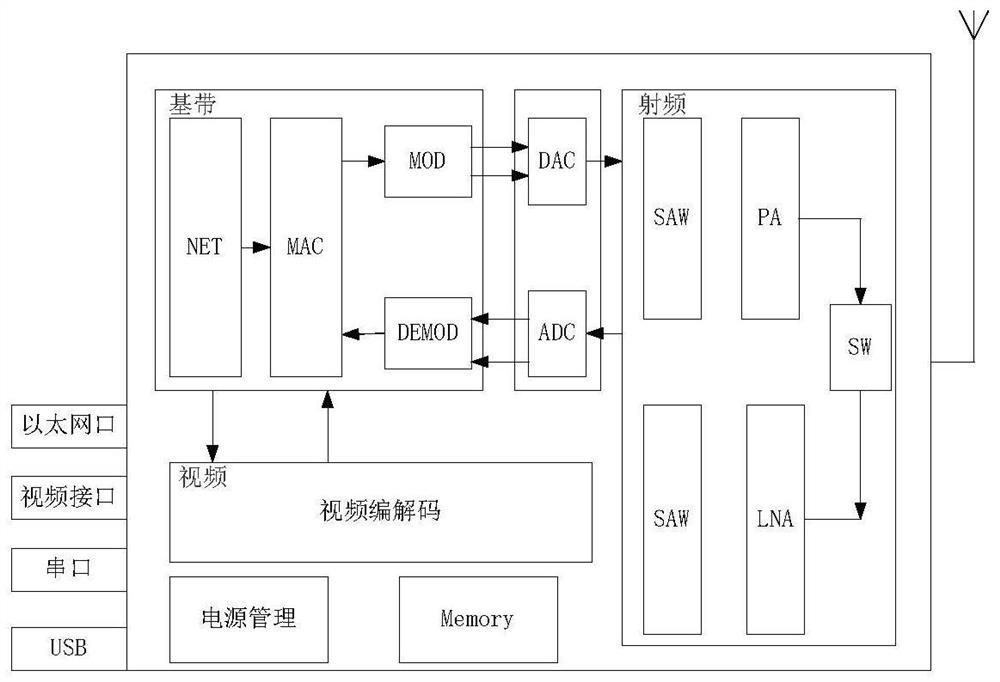

A high-definition audio and video ad hoc network data interaction system based on 230mhz wireless private network

ActiveCN109905341BImprove utilization efficiencyAnti-jamming hasDigital video signal modificationMulti-frequency code systemsInterference (communication)Private network

The invention discloses a high-definition audio and video ad hoc network data interaction system based on a 230MHz wireless private network. The control plane is used to complete node control, including admission / authentication / topology maintenance / user plane parameter negotiation; the user plane is used for Complete the transmission of user data on the air port / network port; the management plane is used to complete the configuration management of the device itself and the air port / network port parameters / performance index reporting / log maintenance channel establishment; use TDMA technology to customize the MAC layer protocol, and use DFT ‑S‑OFDM technology designs the physical layer, builds the network topology structure connected to the terminal through the ad hoc network based on the link layer, realizes time division, single frequency point two-way switching, realizes the ad hoc network and two-way transmission; based on multi-carrier technology and Combined with the H.265 video codec scheme to simultaneously transmit audio, video and IP streaming data. The present invention greatly improves the utilization efficiency of 230MHZ low-frequency band resources. A low-frequency and high-bandwidth internal communication network with advanced reliability, security and encryption, and anti-interference can be quickly built on the job site.

Owner:STATE GRID CORP OF CHINA +1

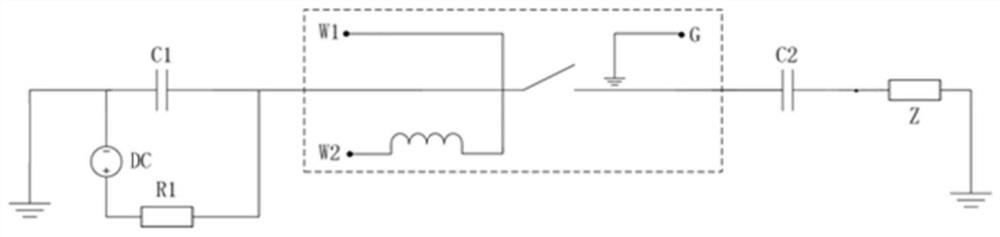

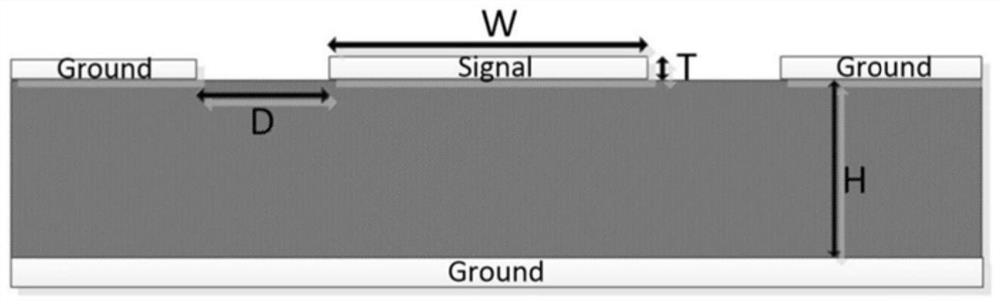

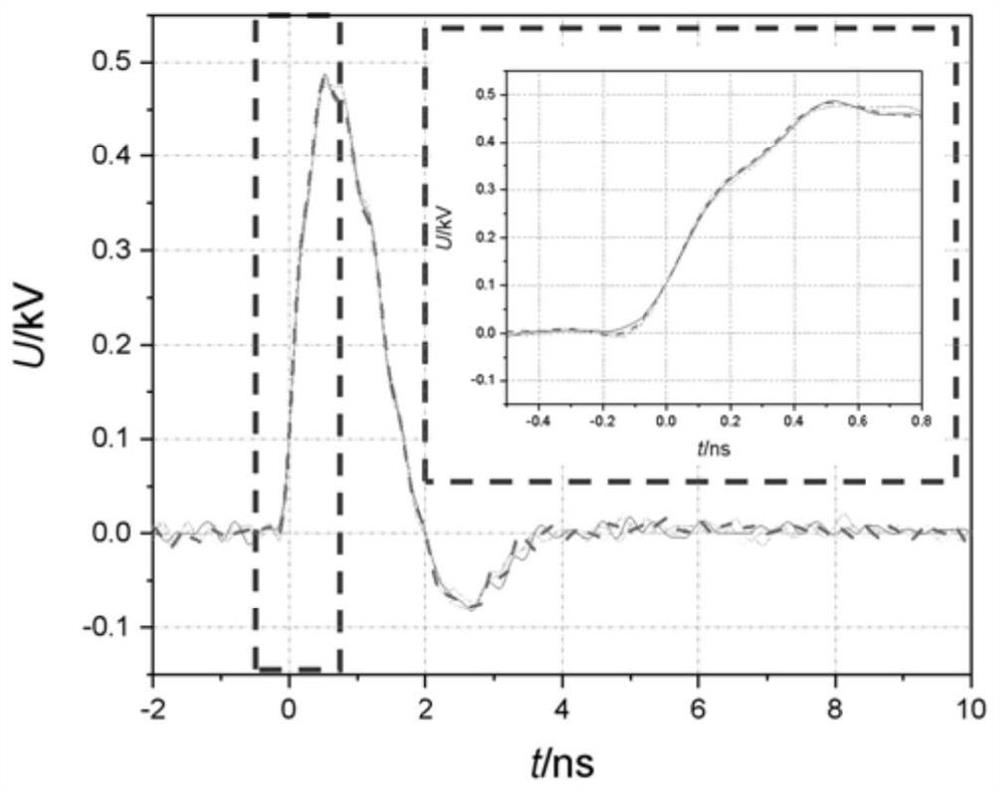

A portable fast pulse generating device and its manufacturing method

ActiveCN109212447BShorten rise timeIncrease ascent speedElectrical measurement instrument detailsElectrical testingCapacitanceHigh-voltage direct current

The invention discloses a portable fast pulse generating device and a manufacturing method thereof, comprising: a high-frequency PCB circuit board, a main loop structure, a secondary loop structure, a power supply and a load; both the primary loop structure and the secondary loop structure are built on a high-frequency PCB circuit board; the main circuit structure includes the main capacitor C 1 , mercury switch and filter module; all components of the main circuit structure are in a straight line; the secondary circuit structure includes a high-voltage DC voltage source and a charging resistor R 1 ; High voltage DC voltage source and charging resistor R 1 Used to form the main capacitor C 1 The charging circuit; the power supply is used for the power supply of the high-voltage DC voltage source; the power supply is also used for the triggering of the mercury switch; the load is connected to the high-frequency PCB circuit board through the SMA plug and the SMA socket. The invention miniaturizes the signal source used to generate the electromagnetic wave for calibration, and can meet the calibration requirement of the ultra-high frequency sensor for partial discharge measurement under actual working conditions on site.

Owner:STATE GRID SHAANXI ELECTRIC POWER RES INST +2

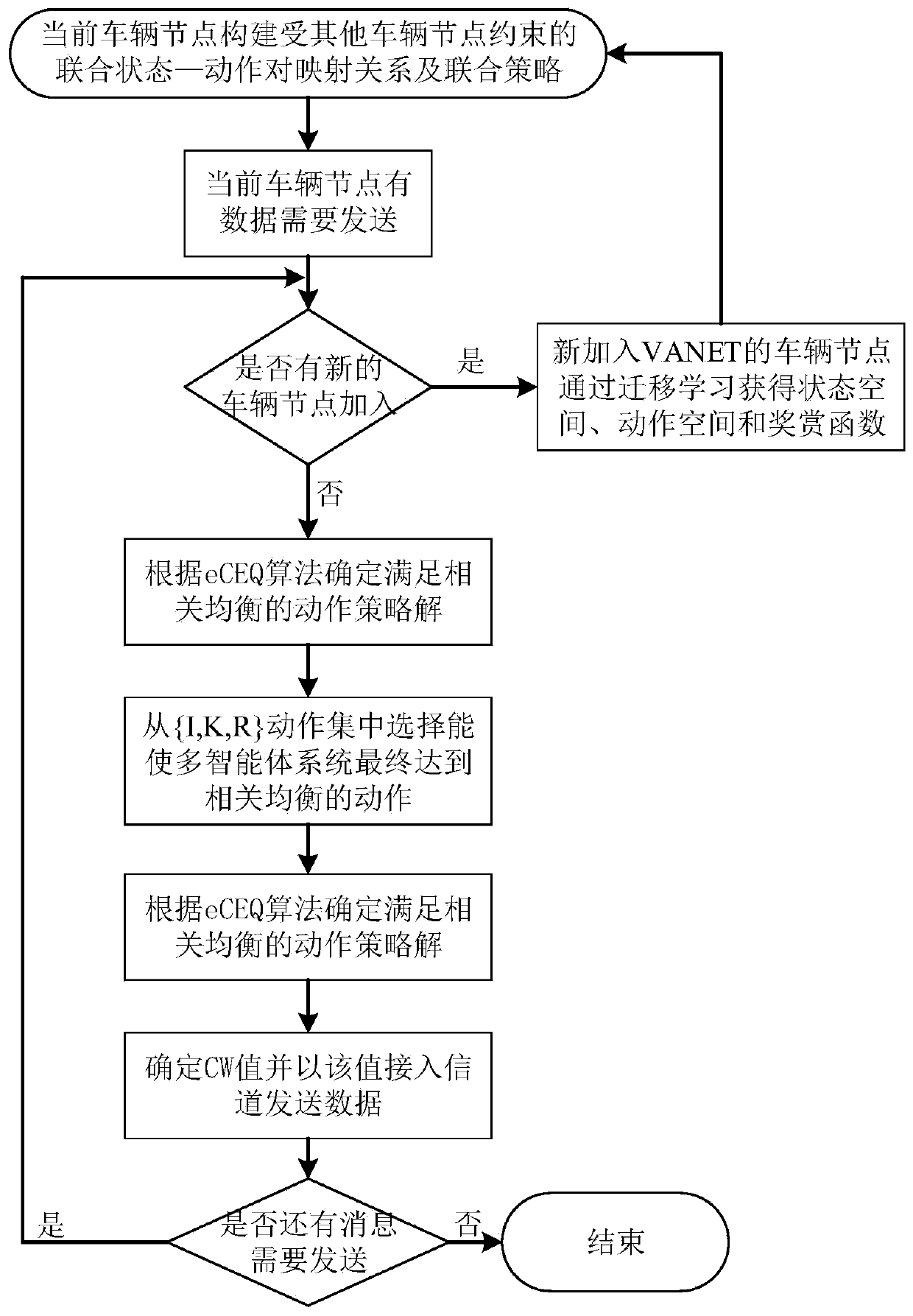

A multi-agent q-learning based channel access method for MAC layer in vehicle communication

ActiveCN107094321BIncrease the probability of successful deliveryReduce the number of dodgesTransmissionWireless communicationData packIn vehicle

The invention discloses an MAC-layer channel access method based on multi-agent Q learning in vehicular communication. The method comprises the steps that: in a VANETs environment, each vehicular node constructs the joint state-action pair mapping relationship and the combined strategy itself; then, whether a new vehicular node is added into a VANET network or not is judged; if the new vehicular node is added into the VANET network, the new added vehicular node rapidly obtains the action space, the state space and the reward function through transfer learning; hereafter, each vehicular node updates the joint state-action pair relationship and the combined strategy itself; if the new vehicular node is not added into the VANET network, whether a current vehicular node has data needing to be sent or not is judged; if the current vehicular node has the data needing to be sent, the action strategy solution satisfying correlated equilibrium can be determined according to a eCEQ algorithm; an action enabling a multi-agent system to achieve correlated equilibrium finally is selected from an action set; a CW value is determined; and, the vehicular node is accessed to a wireless channel to send data according to the CW value. By means of the MAC-layer channel access method based on multi-agent Q learning in vehicular communication disclosed by the invention, the data sending success probability is increased; the withdrawal time is reduced; and the data packet receiving rate, the end-to-end transmission delay problem and the like can be effectively improved.

Owner:NANJING UNIV OF POSTS & TELECOMM

Transmission optimization method, system and equipment of AP network

ActiveCN101742690BOptimize the transmission pathEliminate Bandwidth BottlenecksConnection managementService Access PointComputer science

The embodiment of the invention discloses a transmission optimization method of an AP network, a first access point receives a call message sent to a second user by a first user; the first access point acquires the communication address of a second access point belonging to the second user; and the first access point establishes a direct-connecting transmission tunnel between the first access point and the second access point to enable the first user to communicate with the second user by the direct-connecting tunnel. In the embodiment of the invention, the transmission path of the AP networkcan be optimized, the transmission delay is improved, the bandwidth bottleneck of a core network is eliminated and meanwhile, the cost of the core network is lowered.

Owner:HUAWEI TECH CO LTD

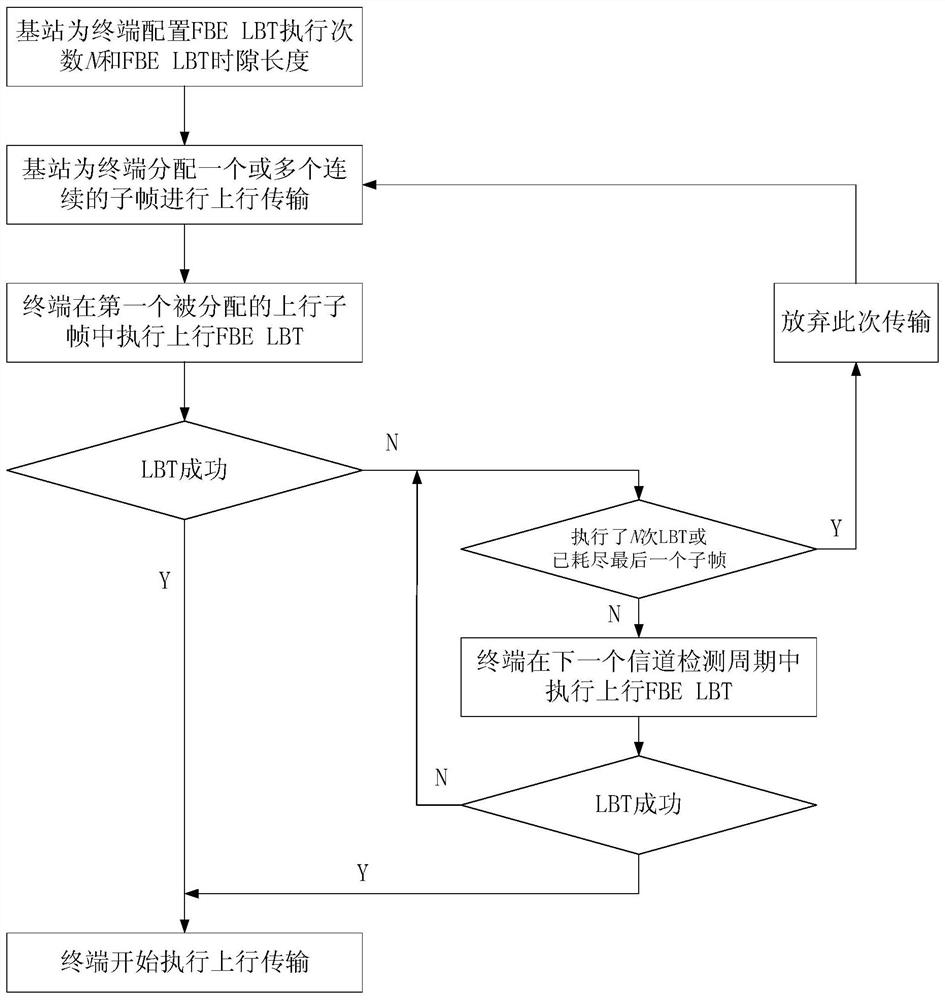

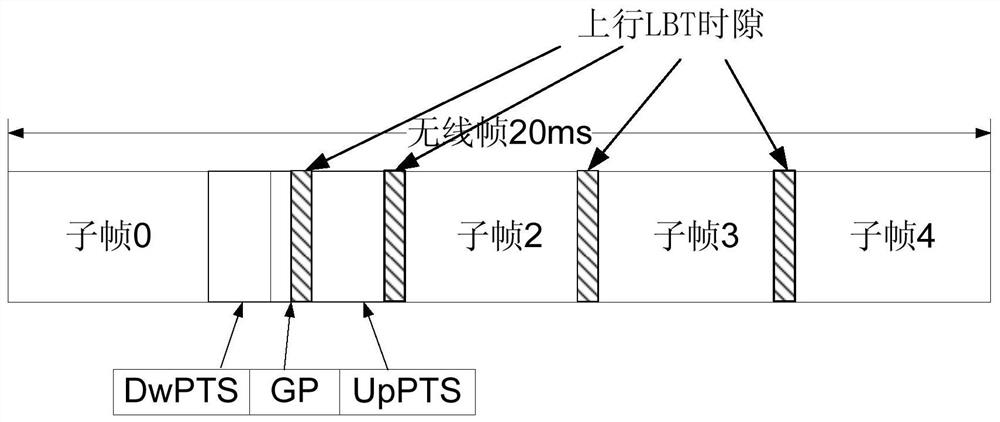

A listening-before-speaking parameter configuration method for frame-based devices

ActiveCN109688626BSatisfy latency requirementsMeet energy consumption requirementsWireless communicationResource assignmentTime delays

The present invention relates to a method for configuring parameters of a listen-before-talk frame-based device, wherein the base station configures the number of FBE LBT executions N for the terminal, or configures the number of FBE LBT executions N and the length of the FBE LBT time slot for the terminal; When performing uplink resource allocation for the first time, the number of times the terminal executes FBE LBT does not exceed the number of times N of FBE LBT executions; the terminal configures FBE LBT time slots based on the length of the FBE LBT time slot, and performs Perform FBE LBT channel detection in . The invention satisfies the time delay requirements of different services and the energy consumption requirements of different terminals by rationally configuring FBE LBT parameters for the terminals, and can adapt to complex and dynamic interference environments, thereby improving the transmission performance of the system.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

A source location privacy protection method based on multi-phantom node strategy

ActiveCN107148013BImprove practicalityImprove securityNetwork topologiesSecurity arrangementTransmission time delaySimulation

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

A Carrier Sense-Based Protocol Sequence Channel Access Algorithm

ActiveCN106658749BGuaranteed synchronicityIncrease profitSynchronisation arrangementAlgorithmTime delays

The invention proposes a protocol sequence channel access algorithm based on carrier interception. The algorithm comprises the steps: firstly distributing a binary protocol sequence to each network node, and reading the sequence values sequentially; secondly transmitting a data group with a non-fixed length when the current sequence value is one, and determining the moment of keeping silent according to a channel interception result when the current sequence value is zero. Compared with a conventional protocol sequence channel access mechanism, the method is more suitable for a network scene comprising various types of data businesses. Moreover, the time delay performance is remarkably superior to a p-persistence CSMA channel access mechanism.

Owner:NANJING UNIV OF SCI & TECH

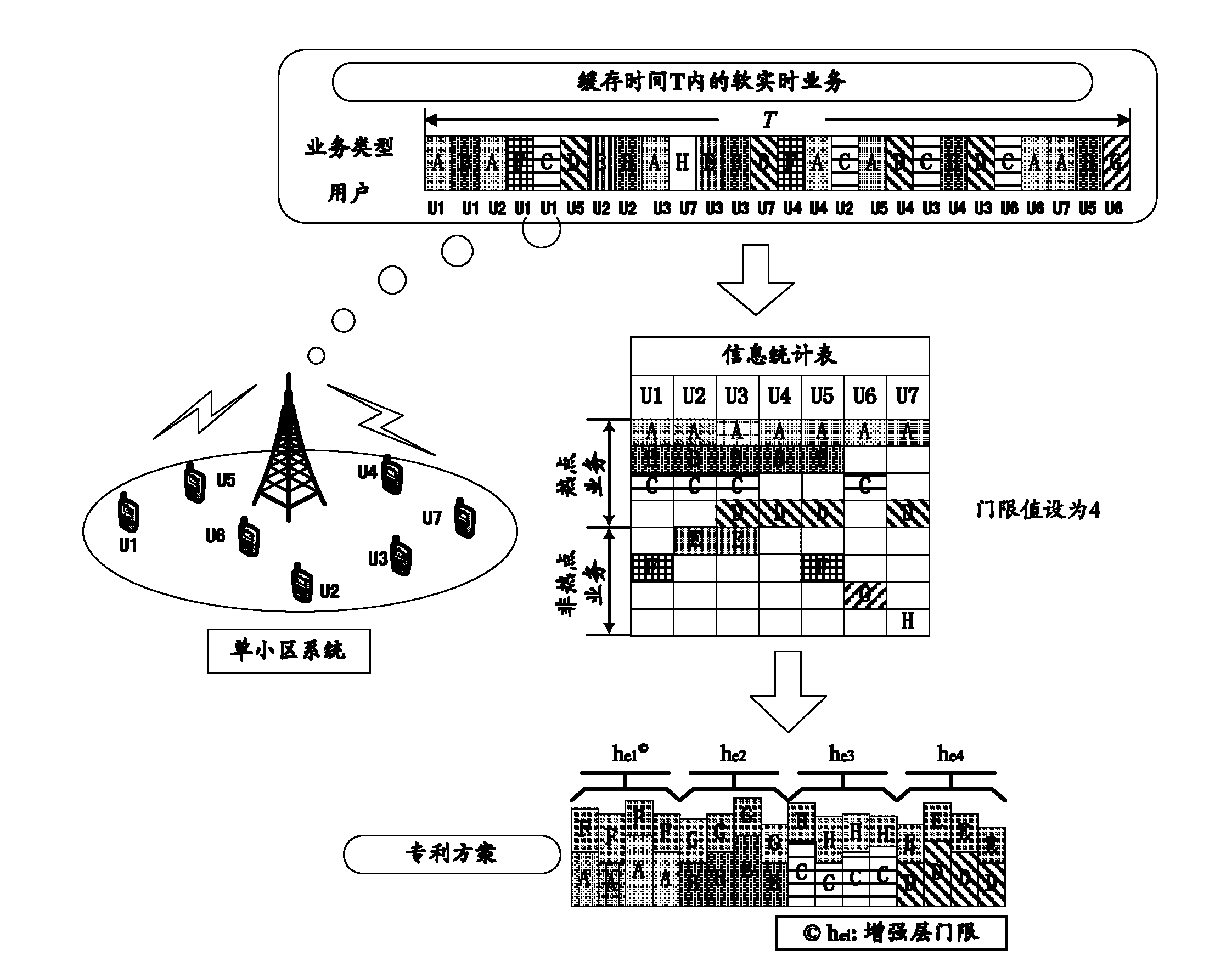

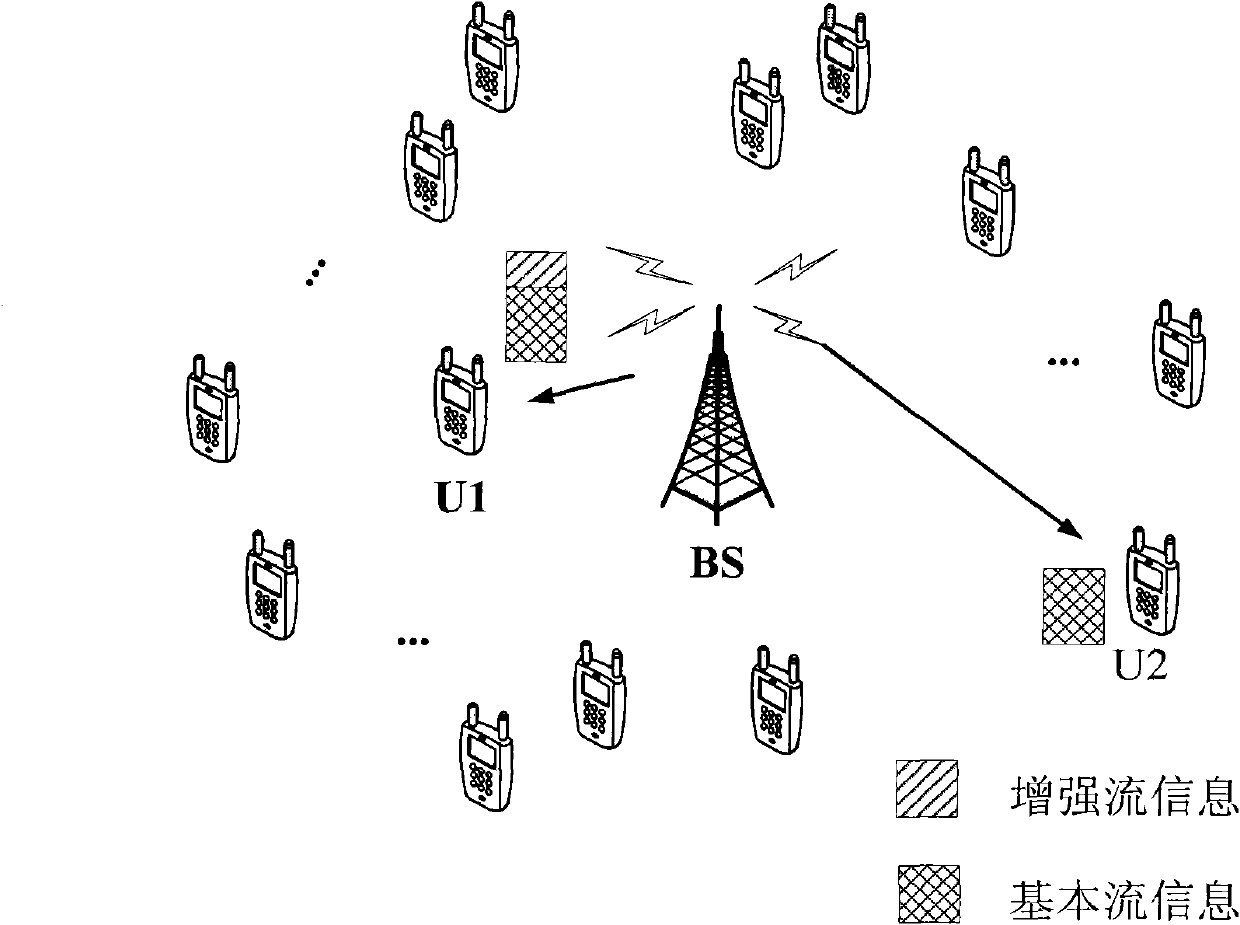

Opportunity multicast method for high-energy efficiency unicast and multicast mixed services based on superposed codes

InactiveCN102611997BNo restrictionsGuaranteed service qualityEnergy efficient ICTBroadcast service distributionHigh energyUnicast

The invention discloses an opportunity multicast method for high-energy efficiency unicast and multicast mixed services based on superposed codes. The method comprises the following steps of: introducing a transmission scene model of soft real-time services of mixed unicast and multicast, superposing service data of unicast and multicast by employing a coding mode of the superposed codes so as to improve the resource utilization rate of the power and the frequency spectrum; transmitting the superposed data in an opportunity multicast mode so as to meet the quality of service (QoS) requirement of the two services; and caching the soft real-time services required by a user in a short time, providing a service transmission method for the user required for the same service in the caching time through broadcast so as to improve the resource utilization rate of the system; and meanwhile, calculating to acquire an optimized selection scheme of enhancement layer service in the superposed codes so as to optimize the energy efficiency of the multicast transmission method. The QoS of various services can be effectively guaranteed, the transmission efficiency and the throughput of the system are obviously improved, and the method is suitable for multiple wireless communication networks and has good popularization and application prospects.

Owner:BEIJING UNIV OF POSTS & TELECOMM

Power allocation method for wireless broadcast multicast layered modulation

InactiveCN102036184BImprove service qualityAchieve optimization goalsPower managementBroadcast service distributionWireless broadcastSystem time

The invention discloses a power allocation method for wireless broadcast multicast layered modulation. In the method, a transmitting end allocates power lambda P to an elementary stream, allocates (1-lambda)P to an enhanced stream and transmits the elementary stream at a first user selected rate pb and the enhanced stream at a second user selected rate pe every time, until the user rate of receiving the elementary stream is presumed to be more than or equal to a preset rate H, wherein the lambda is a power allocation factor and is more than 0 and less than or equal to 1, and P is total power for transmitting the elementary stream and the enhanced stream; and the value of the lambda is determined to be the maximum value of the lambda, wherein Cu is throughput of the enhanced stream at the transmission finishing moment, KB is system time delay at the transmission finishing moment, Cu and KB are expressions of the lambda, and H is more than or equal to 90 percent. The invention provides an optimal power allocation method, and the system performance optimization is realized.

Owner:BEIJING UNIV OF POSTS & TELECOMM

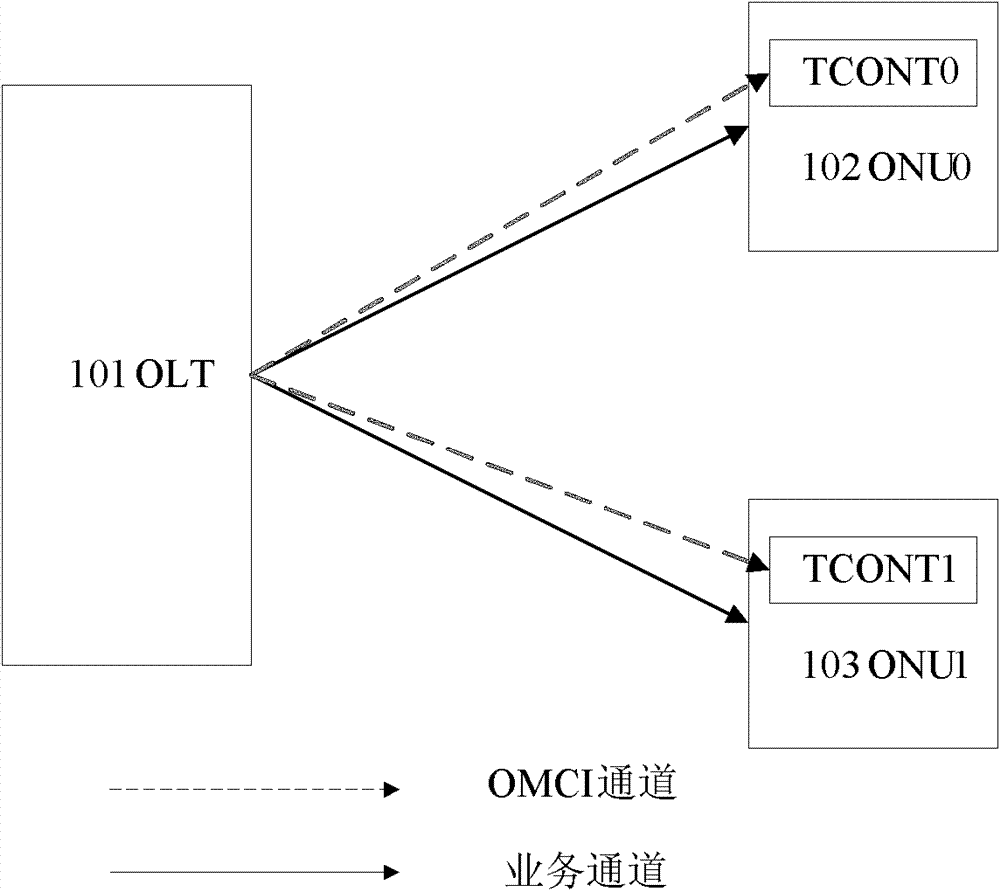

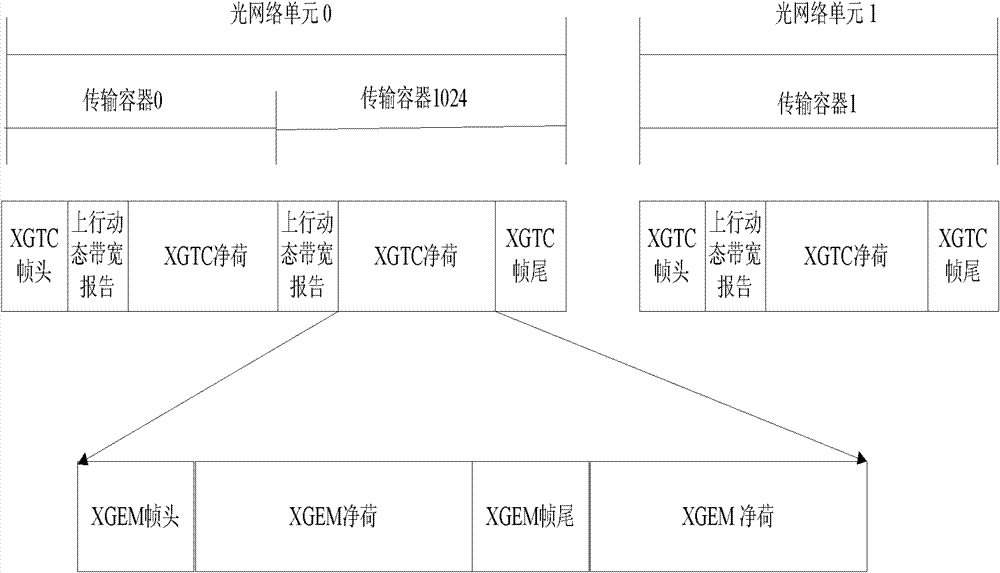

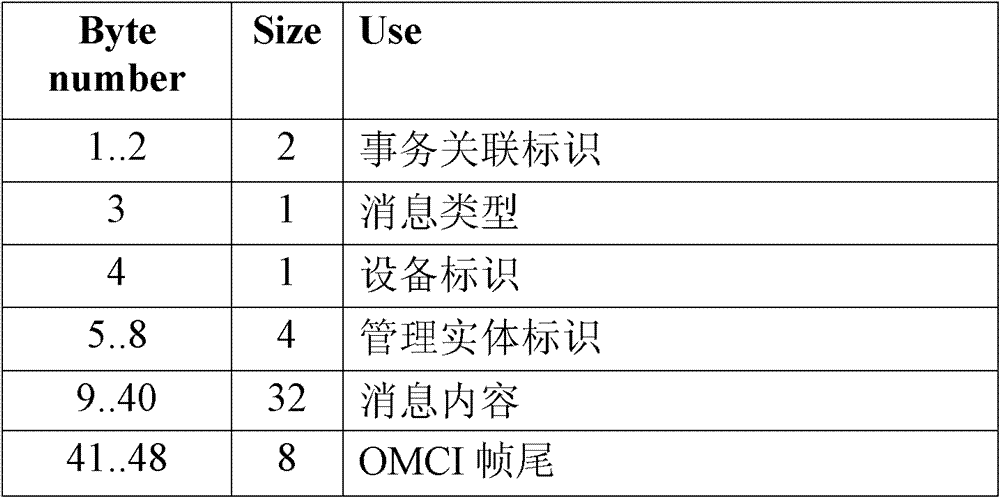

Device and method for dynamically allocating bandwidth of operation management control interface

ActiveCN102685610BTimely recyclingAddresses a significant reduction in available bandwidthMultiplex system selection arrangementsData switching networksInformation transmissionComputer science

Owner:SANECHIPS TECH CO LTD

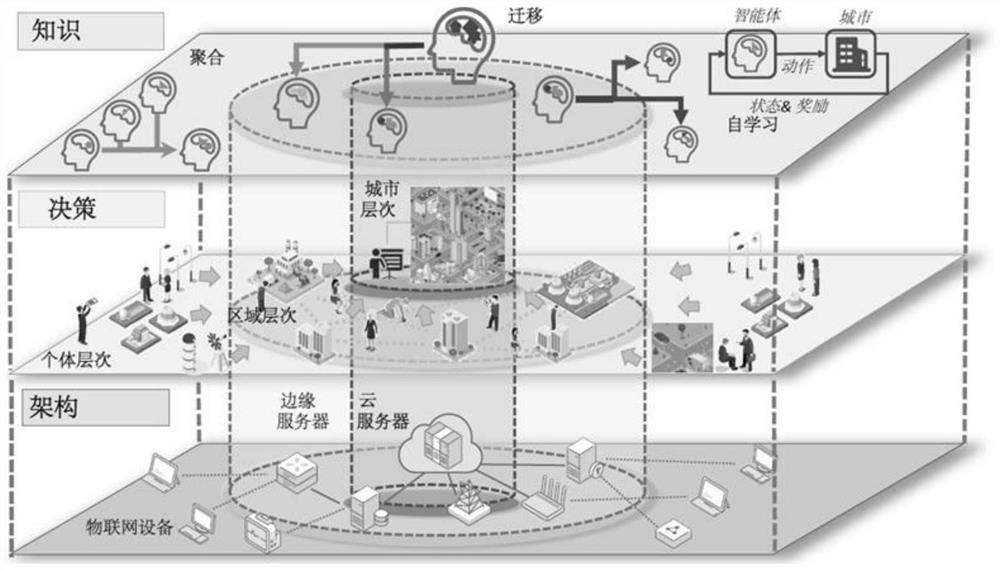

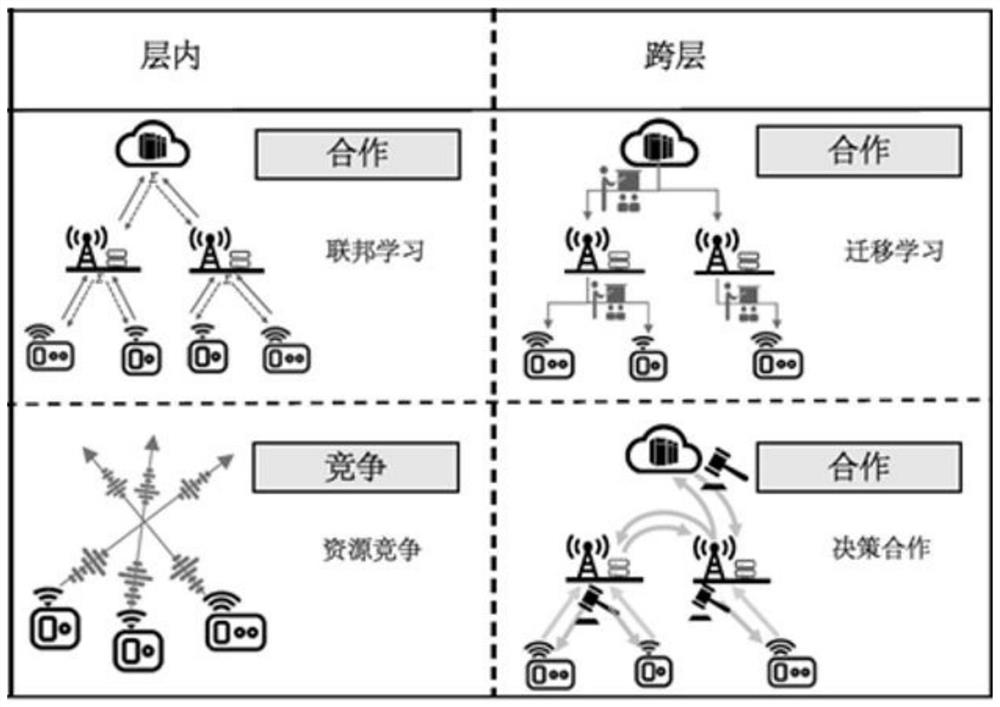

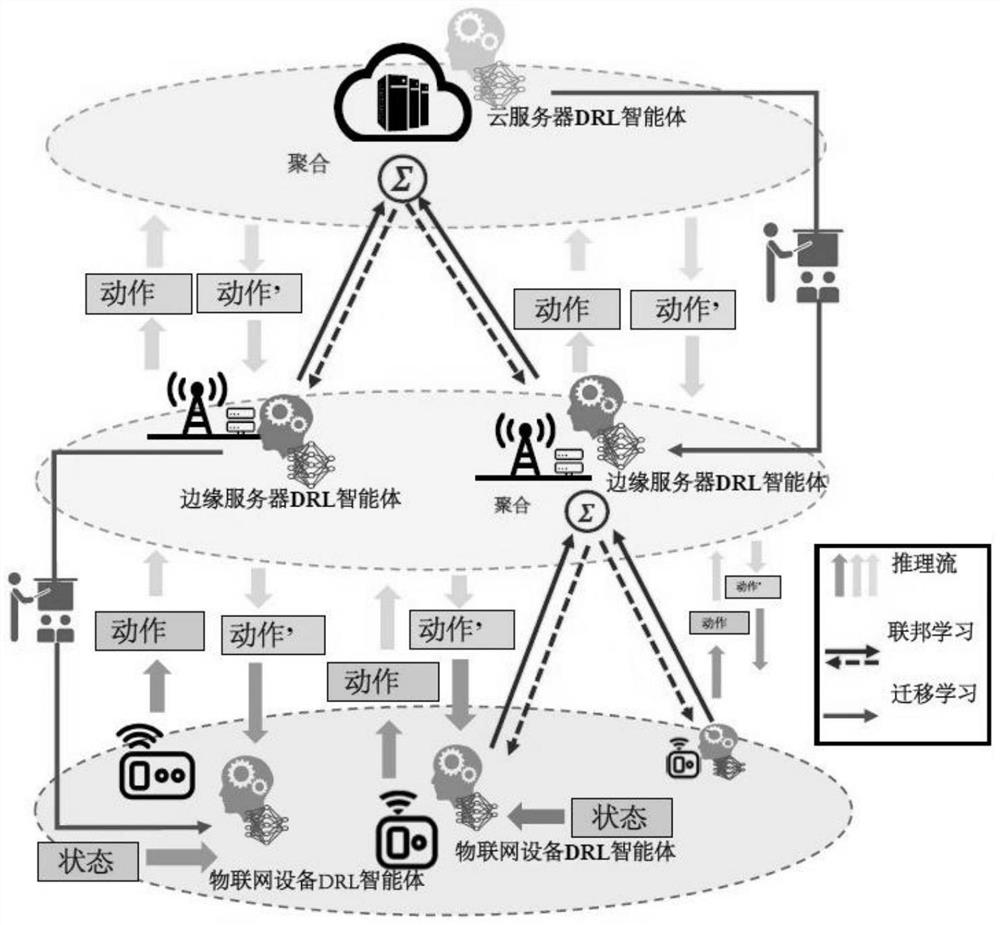

Social learning method for smart city

ActiveCN114143212AImprove performanceOptimize transmission delayData processing applicationsResource allocationSocial learningInternet of Things

The invention discloses a socialized learning method for a smart city. The method comprises the following steps: constructing a layered socialized learning system; establishing a task evaluation model based on deep reinforcement learning, and optimizing the task evaluation model by using task states and channel states of all the Internet of Things devices to obtain a basic decision; the edge server utilizes federal learning edge aggregation to receive the task evaluation model, and optimizes the task evaluation model on the edge server according to the basic decision to obtain a high-level decision; the edge server uses transfer learning to guide a model in the Internet of Things equipment; and the cloud server aggregates the received task evaluation model by using federal learning cloud, formulates a municipal decision according to a high-level decision and the task evaluation model on the cloud server, and guides the task evaluation model on the edge server by using transfer learning. According to the method, federal learning is utilized to improve cooperation among intelligent agents in the layers, transfer learning is utilized between the layers to realize guidance from the upper layer to the lower layer, and the performance of the model is improved.

Owner:TIANJIN UNIV

Audio mixing method in multiple-MCU video conference system

InactiveCN100512422COptimize transmission delayAvoid unavailableTelevision conference systemsTwo-way working systemsNetwork conditionsClient-side

Mixing method in the multi-MCU video conferencing system: (1) all MCUs are registered on the gatekeeper (GateKeeper, hereinafter referred to as GK), each MCU and other MCUs are set up between two connections, and each The MCU maintains a connection list with other MCUs and a local client list that needs to be mixed; (2) The MCU linearly superimposes the audio data sent by the local client according to the local mixing client list, and After encoding, it is sent to each peer MCU; (3) the MCU subtracts the audio data of the client to be sent to the mixed result in step (2) and mixes each decoded audio data sent from the peer MCU, Finally encode and send the result to the target client. The invention can reduce the number of audio data transmission hops and avoid single-point failure of the main MCU under the same network conditions, and has higher reliability.

Owner:BEIHANG UNIV

Selection method of data recovery mode and radio network controller

InactiveCN101166344BOptimize transmission delayImprove performanceError prevention/detection by using return channelNetwork data managementData transmission timeNetwork control

Being applicable to switching HSDPA sector, the method includes steps: RNC corresponding to base station belonging to the subzone obtains whether base station supports data retention of MAC-hs entity; RNC initiates switching request on user equipment being in switching subzones; if base station supports data retention of MAC-hs entity, then the switching request does not contain indication for resetting MAC-hs entity; otherwise, the switching request contains indication for resetting MAC-hs entity. Obtaining information whether base station supports data retention of MAC-hs entity or not, theinvention makes RNC possible to select two modes for recovering data. In precondition that known base station supports data retention of MAC-hs entity, the method prefers this mode in order to improve data transmission time delay in aerial port, and raise efficiency of using aerial port. The invention also discloses a wireless network controller.

Owner:TD TECH COMM TECH LTD