Novel millimeter wave sub-sampling DDS frequency mixing fractional frequency division phase-locked loop structure

A fractional frequency division, phase-locked loop technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of high DDS output frequency, phase error, high power consumption, etc., to achieve good filtering effect, reduce power consumption, good The effect of linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

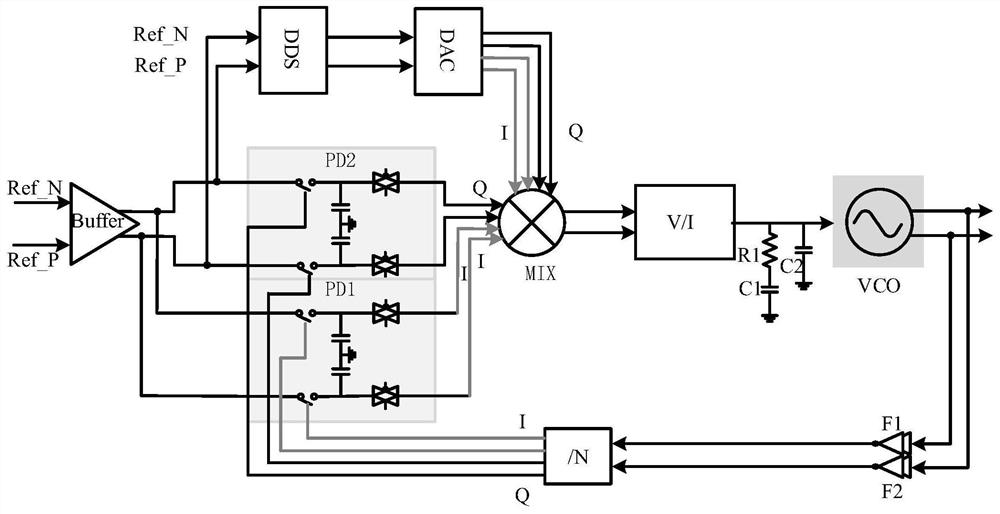

[0041] See figure 2 , figure 2 It is a schematic circuit structure diagram of a novel millimeter-wave sub-sampling DDS mixing fractional frequency division phase-locked loop structure provided by an embodiment of the present invention. This embodiment provides a novel millimeter-wave sub-sampling DDS fractional frequency-division phase-locked loop structure. The phase-locked loop structure includes: Phase PD2, DDS (direct digital frequency synthesizer), DAC (digital-to-analog converter), multiplier (ie MIX), voltage-current conversion circuit (ie V / I), low-pass filter, first inverter chain F1, second inverter chain F2, frequency divider (ie / N) and voltage controlled oscillator (ie VCO), where,

[0042] The first output end and the second output end of the buffer are respectively connected to the first input end and the second input end of the DDS, and the first output end and the second output end of the buffer are respectively connected to the first sub-sampling phase de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More