Passive wireless communication chip verification platform, construction method and chip verification method

A communication chip, passive wireless technology, applied in functional testing, instruments, electrical digital data processing, etc., can solve problems such as increasing the complexity of the environment, and achieve the effects of improving verification quality and verification efficiency, high writing efficiency, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0080] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

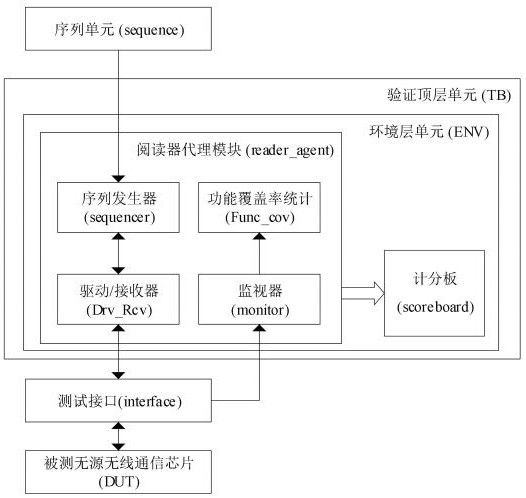

[0081] figure 1 It is a structural block diagram of a UVM-based passive wireless communication chip verification platform provided by an embodiment of the present invention. Such as figure 1 As shown, the verification platform includes:

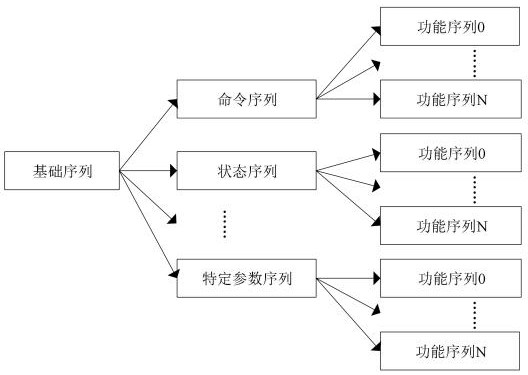

[0082] A sequence unit (sequence), used to provide a three-layer verification sequence for passive wireless communication chip verification;

[0083] Verify the top-level unit, which is used to establish the signal connection between the test interface (interface) and the passive wireless communication chip (DUT) under test, and call the run_test function to start the simulation verification;

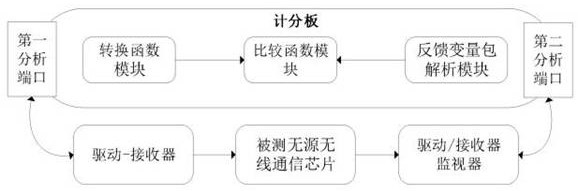

[0084] The environment layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More