DDR3 function testing platform based on digital signal integrated circuit testing system EVA100

A technology of EVA100 and functional testing, applied in the direction of digital circuit testing, electronic circuit testing, electrical measurement, etc., can solve the problems of no DDR3 direct test conditions, no DDR3 test scheme, and high operating frequency of DDR3, so as to facilitate screening tests, The effect of improving test efficiency and reducing test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

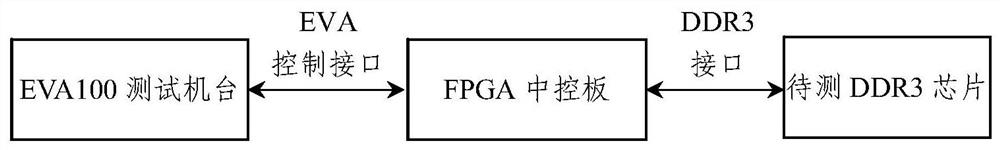

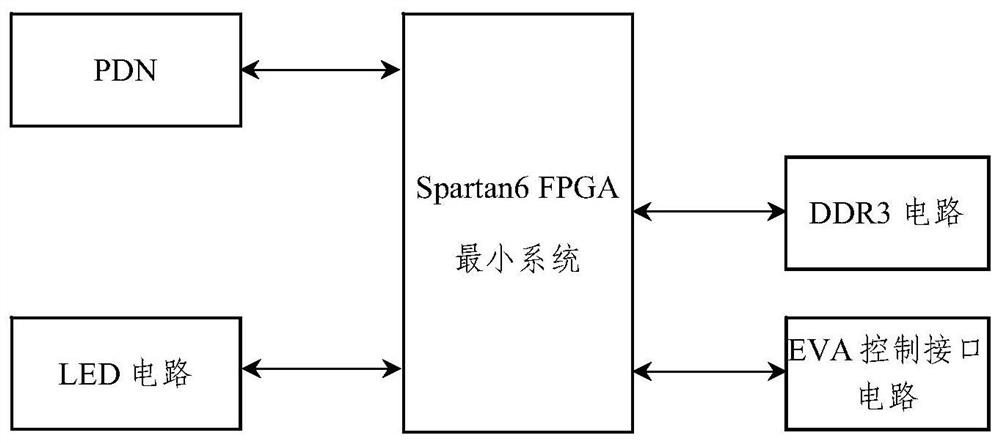

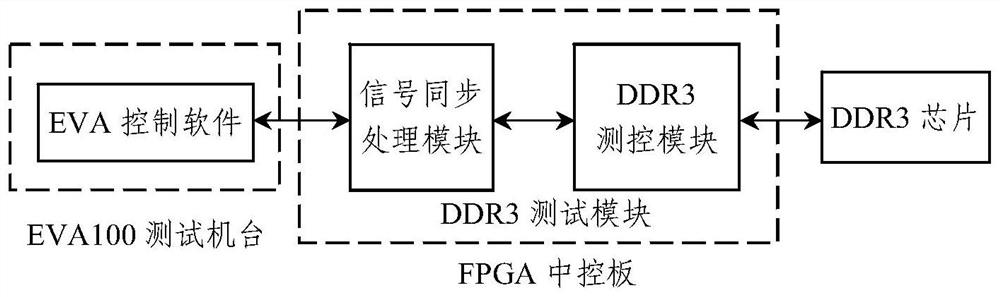

[0034] The overall structural block diagram of the DDR3 function test platform based on the digital signal integrated circuit test system EVA100 provided by the present invention is as follows figure 1 As shown, the test platform mainly includes Advantest EVA100 test machine, FPGA central control board and DDR3 chip to be tested. In view of the fact that the system does not have high requirements for trigger control signals, the EVA100 test machine communicates with the FPGA central control board in a direct connection mode. FPGA central control board adopts Xilinx Spartan6 FPGA chip XC6SLX75 to build DDR3 test platform hardware, including Spartan6FPGA minimum system, power distribution network (Power Distributed Network, referred to as PDN), LED circuit, DDR3 circuit, EVA control interface circuit. A DDR3 automatic test software is designed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com