Method for generating code pattern for signal integrity analysis

A technology of signal integrity and generation method, which is applied in the electronic field, can solve the problems of low efficiency of transistor-level models and low precision of IBIS models, and achieve the effect of enhanced feasibility and improved design efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

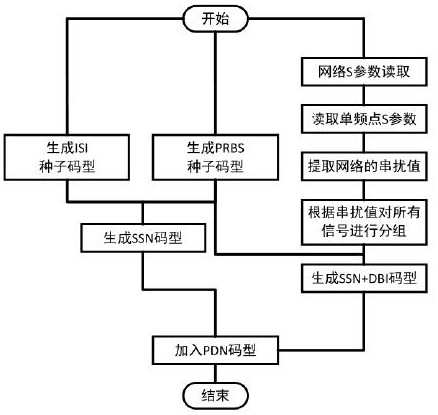

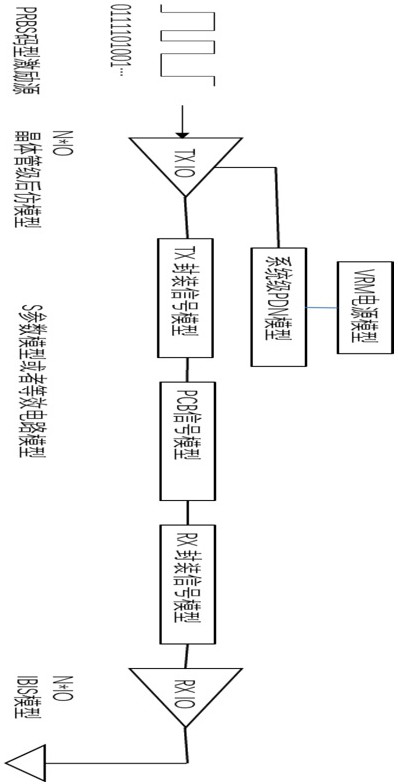

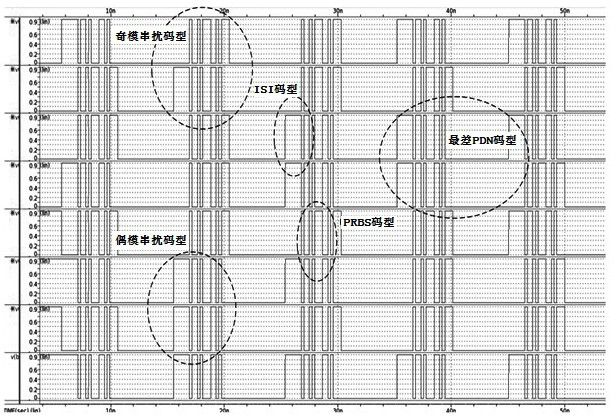

[0021] refer to figure 1 With Fig. 2, the detailed implementation steps of the present invention are as follows:

[0022] Step 1, for each attacked signal, obtain the crosstalk ranking of its attacking signals.

[0023] First read the S-parameter model of the high-speed interface link, and for each signal, read the crosstalk of other signals to it and sort it according to the magnitude. The amplitude here can be selected from a single frequency point (usually the Nyquist frequency of the high-speed interface), or the root mean square of the crosstalk amplitude at multiple frequency points near the Nyquist frequency. The resonance problem of the single frequency point method will cause errors.

[0024] The S-parameter here must be the S-parameter of the whole link, which can be obtained by cascading the S-parameters of each module such as the package...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More