Memory structure and forming method thereof

A memory and storage gate technology, applied in the direction of electric solid state devices, semiconductor devices, electrical components, etc., can solve the problem of NAND memory structure performance needs to be improved, and achieve the effect of increasing the surface area, avoiding accumulation, and reducing material accumulation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

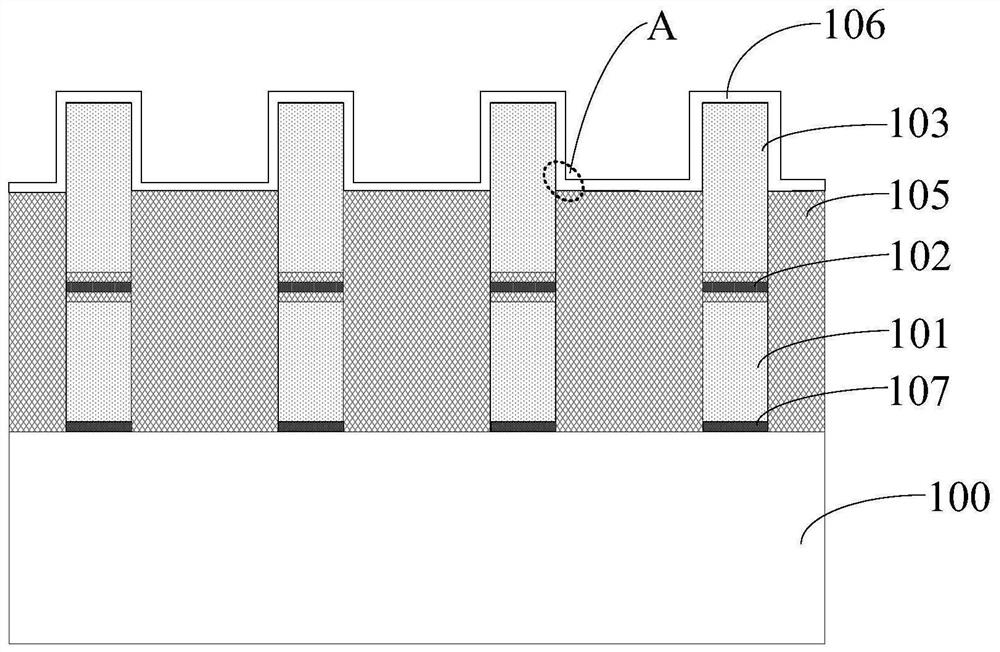

[0036] As mentioned in the background, the performance of the memory structure formed in the prior art still needs to be improved. The following will describe in detail in conjunction with the accompanying drawings.

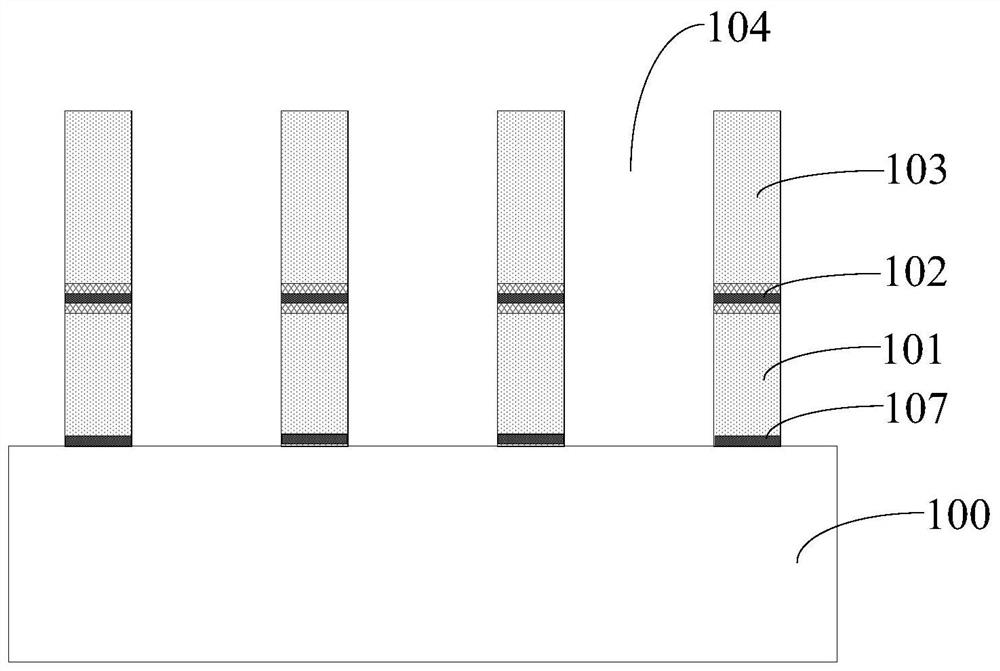

[0037] Please refer to figure 1 , providing a substrate 100, on which a plurality of separate storage gate structures are formed, with isolation grooves 104 between adjacent storage gate structures, and the storage structure includes a first gate dielectric layer 107, The floating gate layer 101 on the first gate dielectric layer 107 , the second gate dielectric layer 102 on the floating gate layer 101 , and the control gate layer 103 on the second gate dielectric layer 102 .

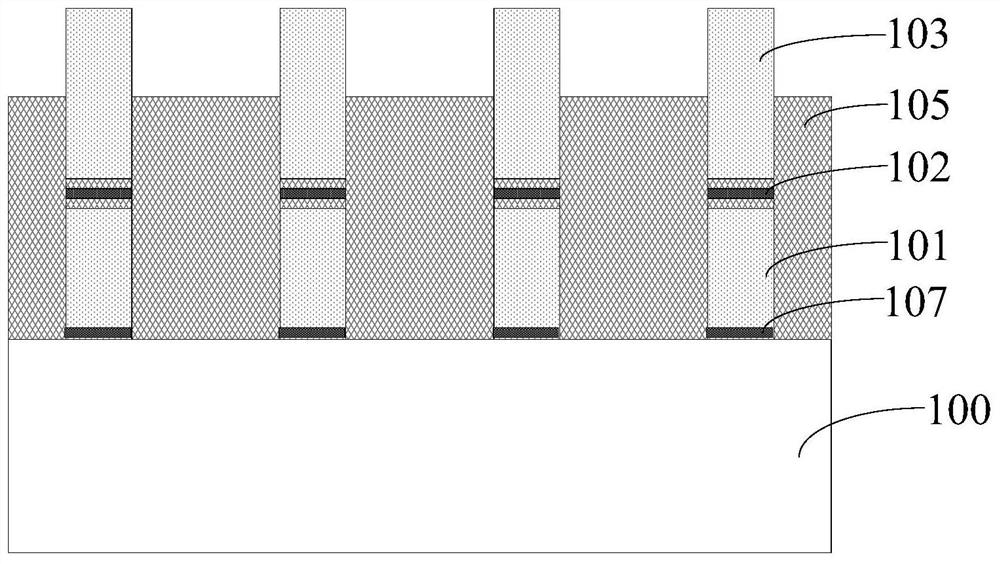

[0038] Please refer to figure 2 , forming an isolation layer 105 in the isolation groove 101, the top surface of the isolation layer 105 is lower than the top surface of the control gate layer 103, and the top surface of the isolation layer 105 is higher than that of the control gate l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More