A FPGA Implementation Method of Multiple Types of Convolution

An implementation method and convolution technology, applied in physical implementation, biological neural network model, architecture with a single central processing unit, etc., can solve the problems of complex structure of deep neural network, limited logic and storage resources, separate design and implementation structure, etc. , to improve flexibility, reduce power consumption and design costs, and save hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to enable those skilled in the art to better understand the solutions of the present application, the following will clearly and completely describe the technical solutions in the embodiments of the present application with reference to the accompanying drawings in the embodiments of the present application.

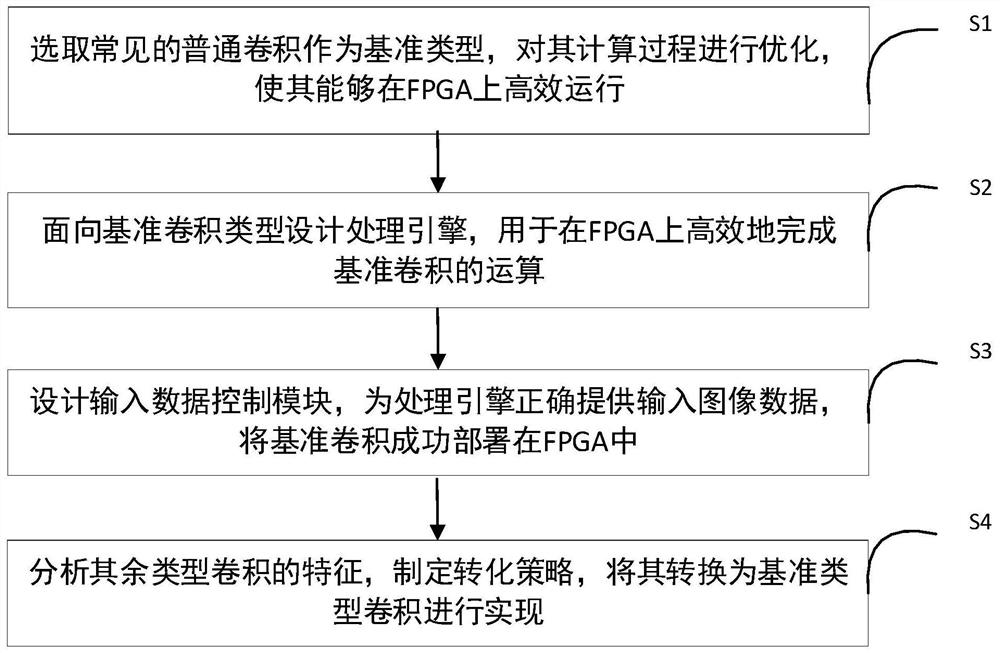

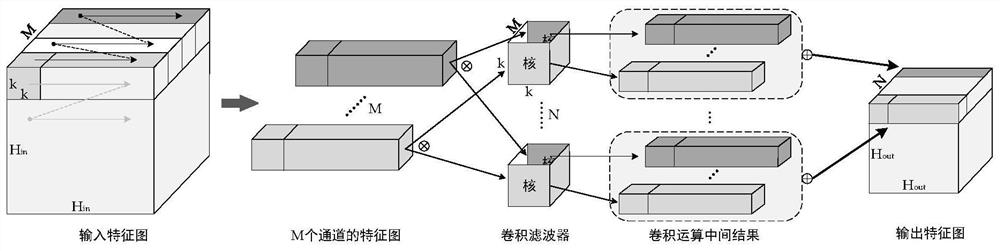

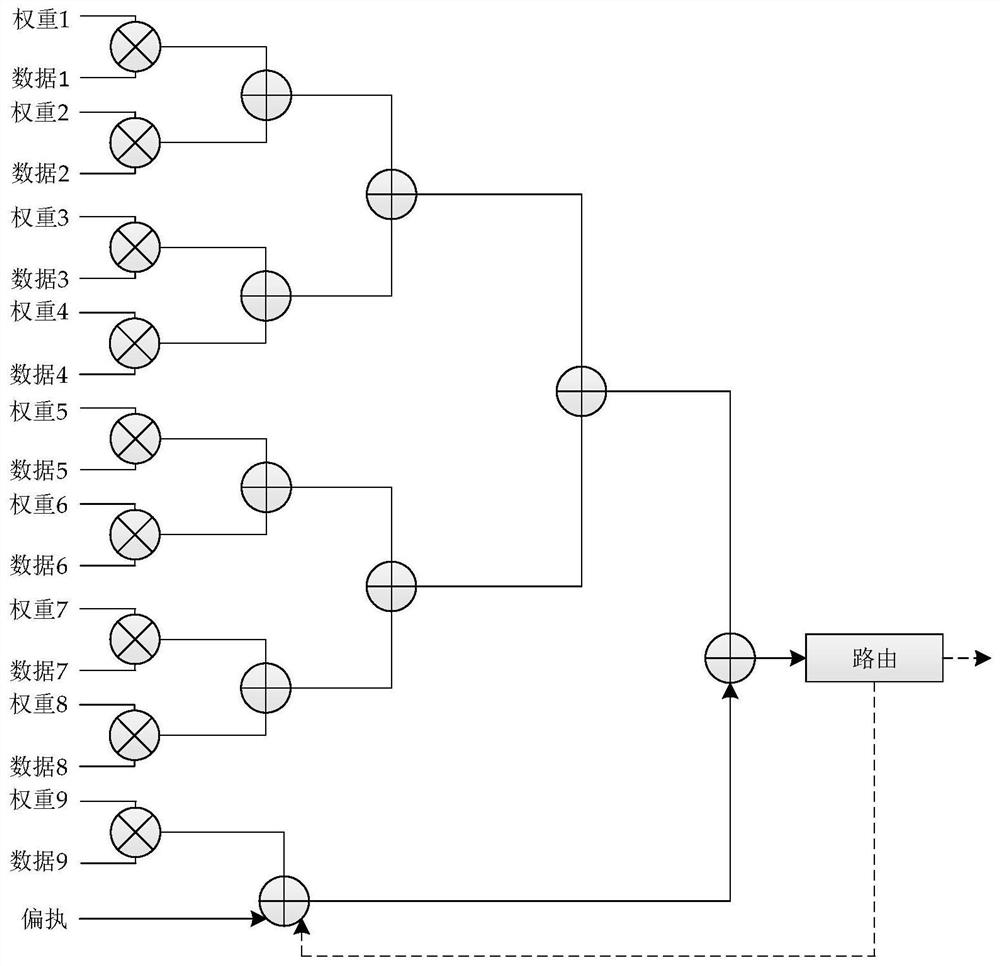

[0032] The present invention provides an FPGA implementation method of multiple types of convolution, which is applied to a deep convolutional neural network, wherein the deep convolutional neural network includes a plurality of convolutional layers, and the convolutional types of each convolutional layer are different. . On the basis of the YOLOv2 network, the deep convolutional neural network of various types of convolutions of the present invention removes the Passthrough operation, and introduces a 3×3 hole convolution with a step size of 1 and an expansion rate of 2, and a step size of 2. 3×3 atrous convolution with an expansion rate of 2, thereby im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com