Flexible planar detector PIN chip and manufacturing method and application thereof

A detector and planar technology, applied in the field of photodetectors, can solve problems such as inapplicable flexible devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0076] In order to describe the technical content, achieved goals and effects of the present invention in detail, the following descriptions will be made in conjunction with the embodiments and accompanying drawings. The test methods used in the examples are conventional methods unless otherwise specified; the used materials, reagents, etc., are commercially available reagents and materials unless otherwise specified.

[0077] Embodiments of the present invention are: a flexible planar detector PIN chip and a preparation method thereof, comprising the following steps:

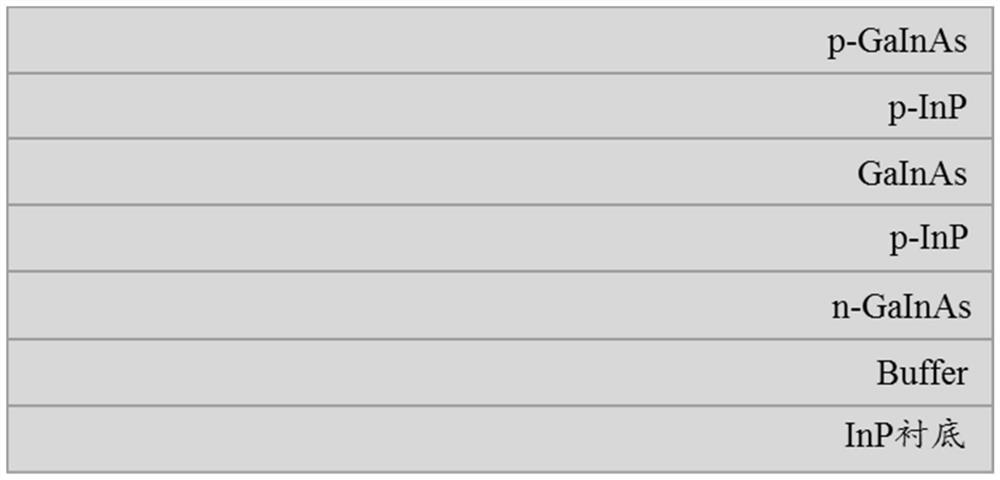

[0078] S1. Grow a Buffer layer (InP) on the surface of the InP substrate, and grow the following layers sequentially upward from the Buffer layer by MOCVD method: n-type InGaAs ohmic contact layer, n-type InP layer, InGaAs layer, p-type InP layer and p-type InGaAs ohmic contact layer, fabricated as figure 1 A prefab A as shown;

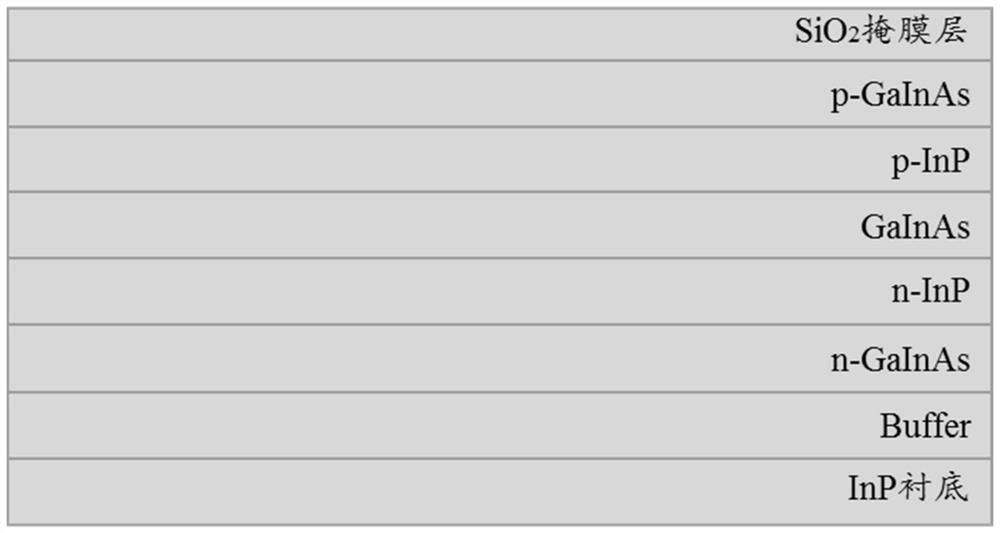

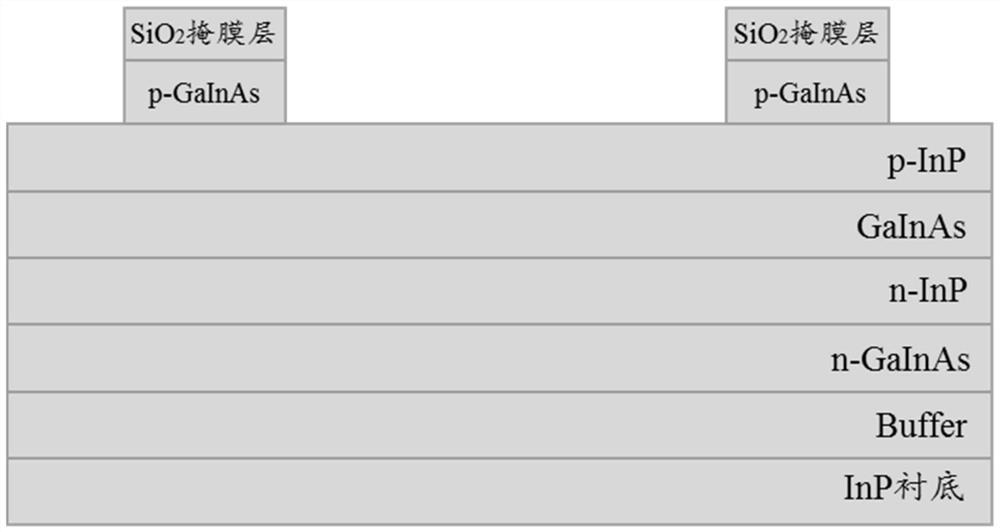

[0079] S2. Deposit SiO on the surface of the p-type InGaAs ohmic contact layer o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More