CMOS hybrid SR memristor latch circuit with asynchronous setting and resetting

A technology of setting reset and memristor, applied in the direction of logic circuit, electrical components, reliability improvement and modification, etc., can solve the problems of not greatly reducing the number of circuit devices, excessive circuit power consumption, etc. less, the circuit structure is simplified, and the circuit structure is simple.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the objectives, technical solutions and advantages of the present invention more clear, the present invention will be further described below in conjunction with the accompanying drawings and examples of the invention.

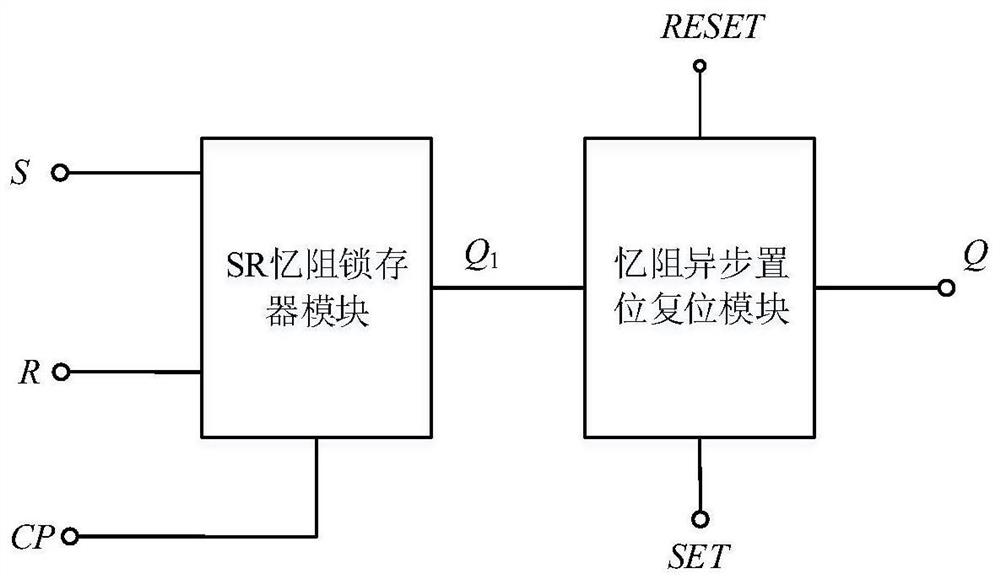

[0018] figure 1 It is a block diagram of the circuit structure of the present invention, and the whole circuit includes an SR memristor latch module and a memristor asynchronous setting and reset module, wherein the SR memristor latch module is composed of memristors and CMOS transistors, the circuit structure is simple, and the number of components is relatively small. The traditional SR latch is greatly reduced and fully functional. The memristor asynchronous set reset module is constructed by the AND gate and the OR gate formed by the memristor, and realizes the asynchronous set and reset function of the circuit. The entire circuit uses a small number of components, is fully functional, and is non-volatile

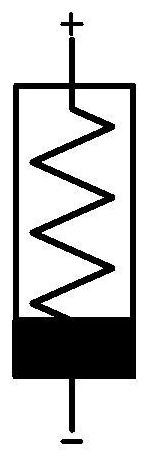

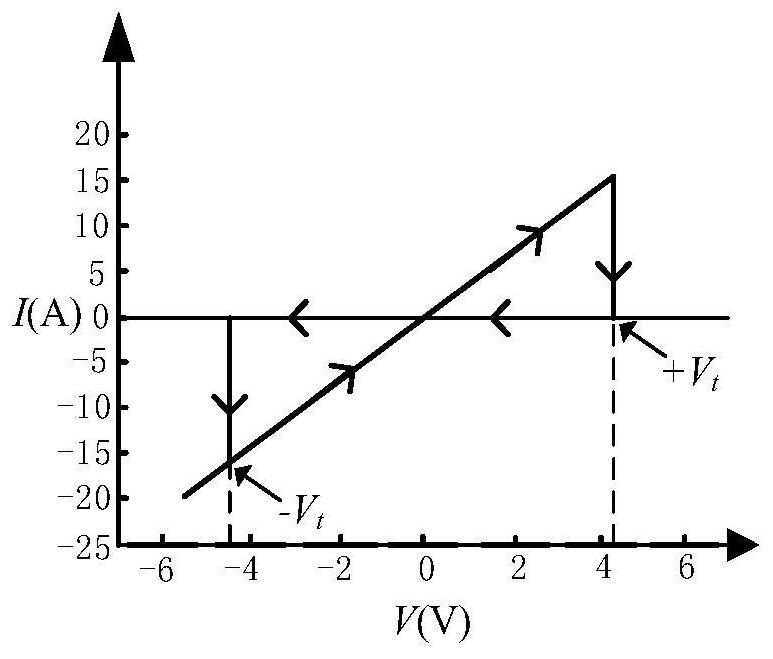

[0019] figure 2 It is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com