Silicon-based eutectic bonding structure, micro-mechanical device, packaging structure and preparation method

A technology of micromechanical devices and eutectic bonding, which is applied in the direction of optomechanical equipment, microstructure devices, metal processing machinery parts, etc., can solve the problems that hinder the reliable formation of bonding structures, and achieve the improvement of mechanical bonding reliability and electrical Interconnect contact reliability, broadening the effect of device fabrication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

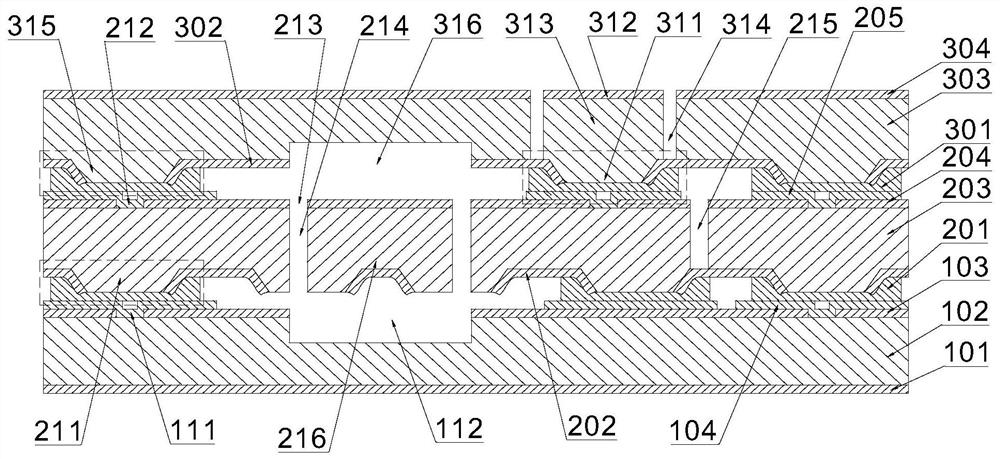

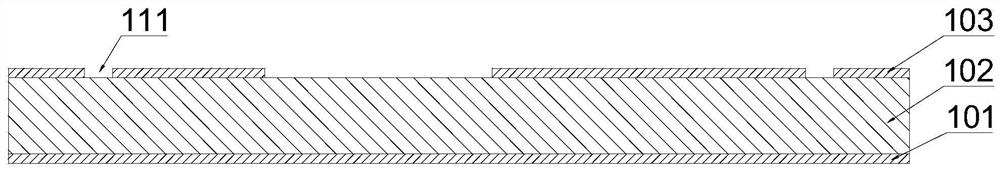

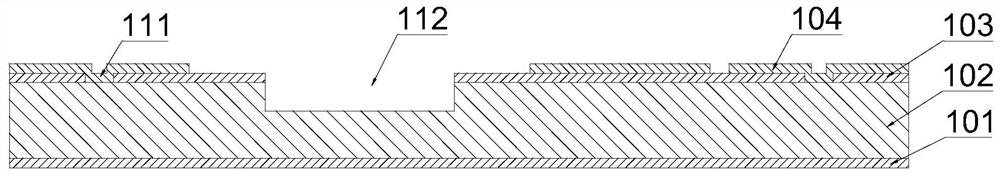

[0051] see figure 1 , the micromechanical device adopting the silicon-based eutectic bonding structure in this embodiment includes a device silicon wafer 203, and both sides of the device silicon wafer 203 are sequentially provided with a device insulating layer 202 and a device-side bonding metal layer 201, Wherein, the device insulating layer 202 at the bottom side is provided with a device bottom side insulating layer window, and the device side bonding metal layer 201 at the bottom side is in electrical contact with the device silicon wafer 203 through the device bottom side insulating layer window; The device-side bonding metal layer 201 and the substrate-side bonding metal layer 104 are connected to each other to form a bonding structure; the silicon wafer 203 of the device is provided with a silicon boss 211 at a position corresponding to the window of the insulating layer on the bottom side of the device, The silicon boss 211 is surrounded by an insulating layer, and t...

Embodiment 2

[0067] see figure 1 , the silicon-based eutectic bonding micromechanical packaging structure in this embodiment includes a micromechanical device and a cover plate packaging interconnection structural unit, the micromechanical device includes a substrate unit and a device unit, and the substrate unit It includes a substrate silicon wafer 102 on which a substrate insulating layer 103 and a substrate-side bonding metal layer 104 are sequentially disposed.

[0068] The cover package interconnection structure unit includes a cover silicon chip 303, the bottom side of the cover silicon chip 303 is provided with a cover insulating layer 302 and a cover side bonding metal layer 301 in turn, and the cover silicon chip 303 The top side is provided with a cover plate top side metal layer 304; wherein, the cover plate side bonding metal layer 301 is bonded to the device side bonding metal layer 201 through a silicon-based eutectic bonding structure including the silicon boss 211 The cov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More