Analog circuit comprising high-resistance resistor and GGNMOS ESD and manufacturing method thereof

A technology for simulating circuits and manufacturing methods, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of complex process steps and high manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

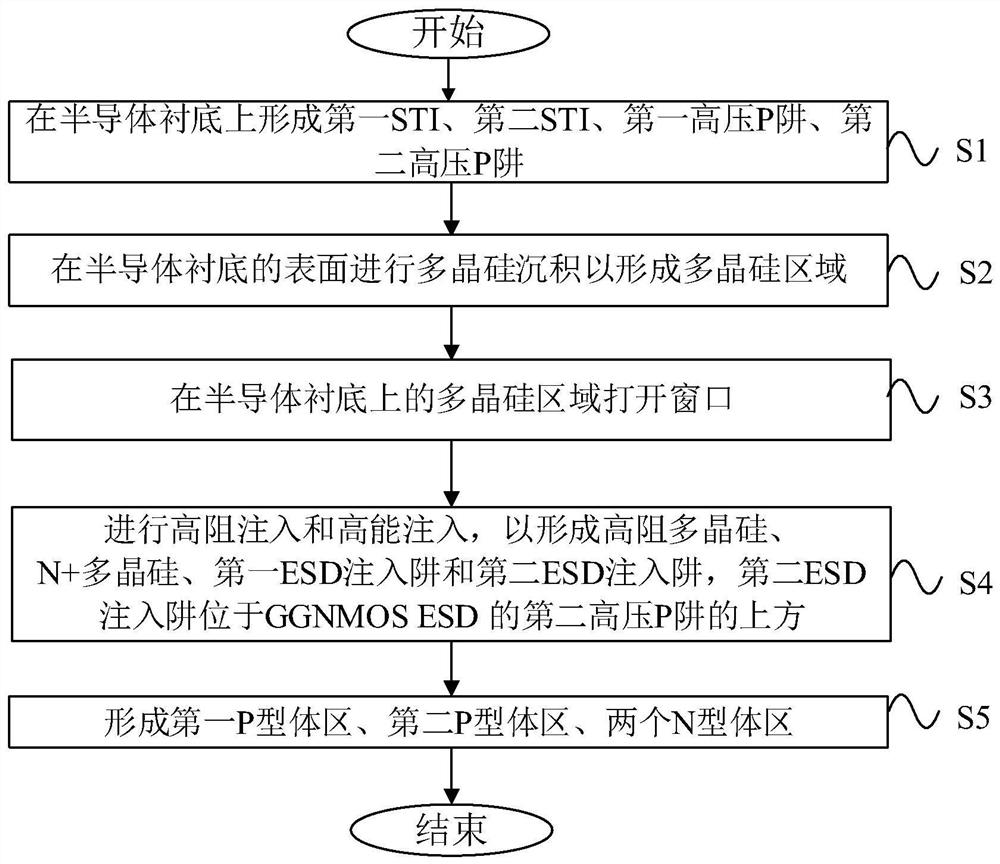

[0039] This embodiment provides a method for making an analog circuit including a high-impedance resistor and a GGNMOS ESD, such as image 3 As shown, the manufacturing method disclosed in this embodiment includes the following steps:

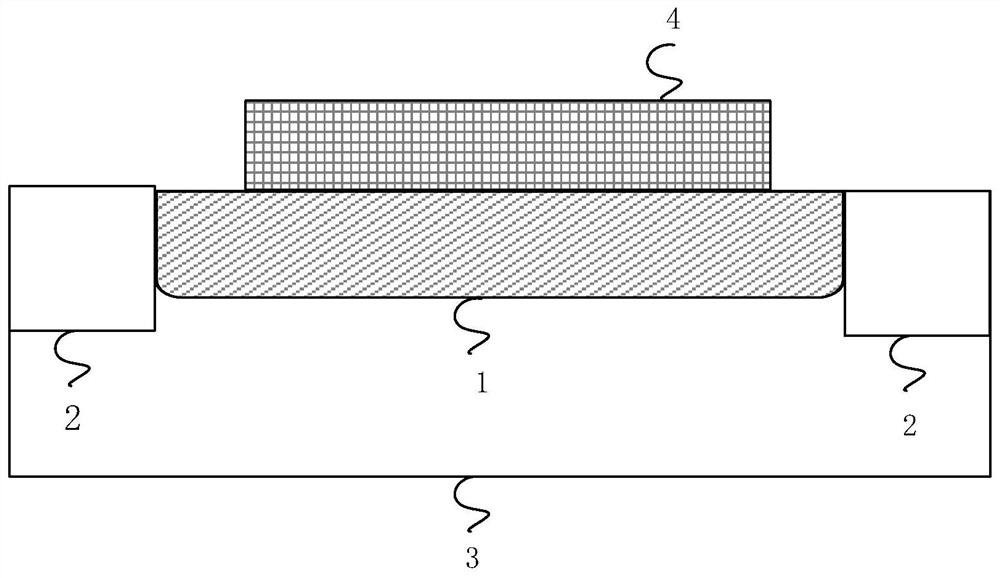

[0040] Step S1 , forming a first STI1 , a second STI5 , a first high voltage P well 3 , and a second high voltage P well 6 on the semiconductor substrate.

[0041] In this embodiment, when the first STI1 and the second STI5 are fabricated on the semiconductor substrate, in other words, the STI region is fabricated. Etch trenches in preset areas in the first high-voltage P well 3 and the second high-voltage P well 6 through a mask, and then fill the trenches with SiO 2 (Silicon Dioxide), using device pairs to fill SiO 2 The grooves are polished to form regions corresponding to the first STI1 and the second STI5, that is, shallow trench isolation regions.

[0042] Step S2, performing polysilicon deposition on the surface of the semiconductor s...

Embodiment 2

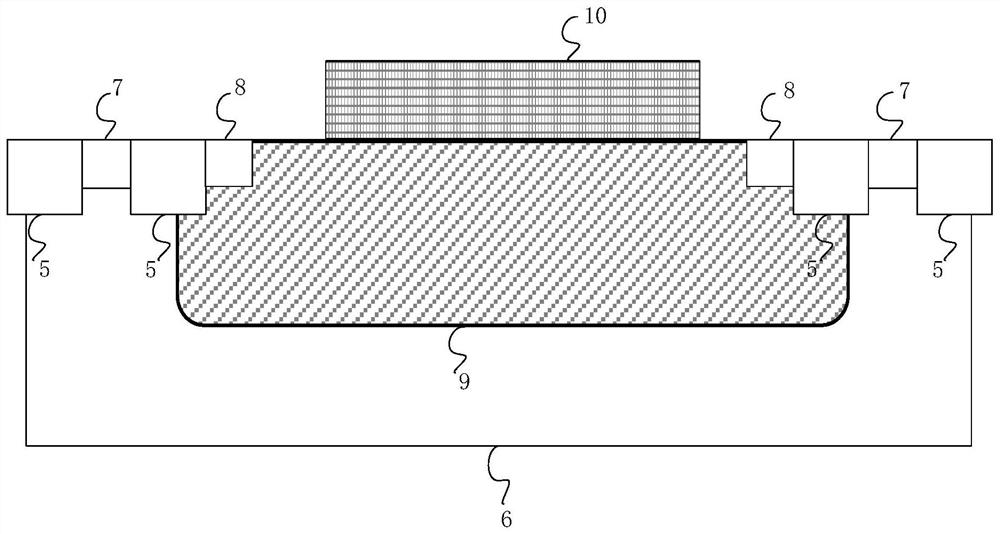

[0073] This embodiment provides an analog circuit including a high-resistance resistor and GGNMOS ESD, and the high-resistance resistor and GGNMOS ESD are manufactured using the method for manufacturing an analog circuit including a high-resistance resistor and GGNMOS ESD in Embodiment 1.

[0074] Compared with the manufacturing method of the traditional standard high-resistance resistor and GGNMOS ESD device, the analog circuit including high-resistance resistor and GGNMOS ESD provided by this embodiment uses high-resistance injection to insert high-energy ESD injection instead of a separate ESD injection well. mask, that is, the use of high-resistance injection and high-energy injection realizes the combination of two photomasks into one photomask, realizes the production of free GGNMOS ESD, solves the problem of complex analog circuit technology including high-resistance resistors and GGNMOS ESD, and saves manufacturing cost. At the same time, the efficiency of the GGNMOS E...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More