Multi-layer chip laminated assembly packaging structure and preparation process thereof

A technology of laminated components and packaging structures, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., and can solve the problems of not being able to meet the sealing of small packaging structures at the same time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0037] The preparation process of the packaging structure of the multi-layer chip stack assembly specifically includes the following steps:

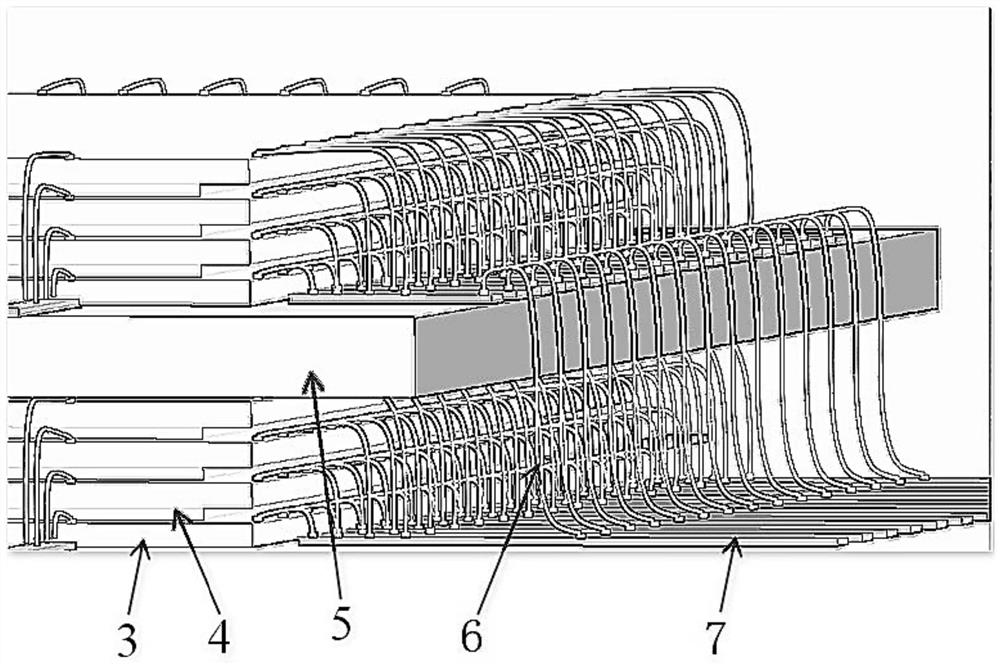

[0038] 1) Bonding the lowest chip 3 of one group of multi-chip stacking assembly units on the shell substrate, and bonding to the shell substrate by reverse bonding process; bonding the bottommost chip 3 of another group of multi-chip stacking assembly units The underlying chip 3 is bonded to the film substrate adapter plate 5, and bonded to the film substrate adapter plate 5 through a reverse bonding process;

[0039] 2) For the package substrate and the film substrate adapter plate 5 respectively, bond the gasket 4 on the bottom chip 3, and bond the chip 3 on the gasket 4;

[0040] Repeat successively to first bond the gasket 4 on the chip 3, then bond the chip 3 on the gasket 4, and make a multi-chip stack assembly unit on the shell substrate and the film substrate adapter plate 5 respectively; Before the gasket 4, the chip 3 is resp...

Embodiment

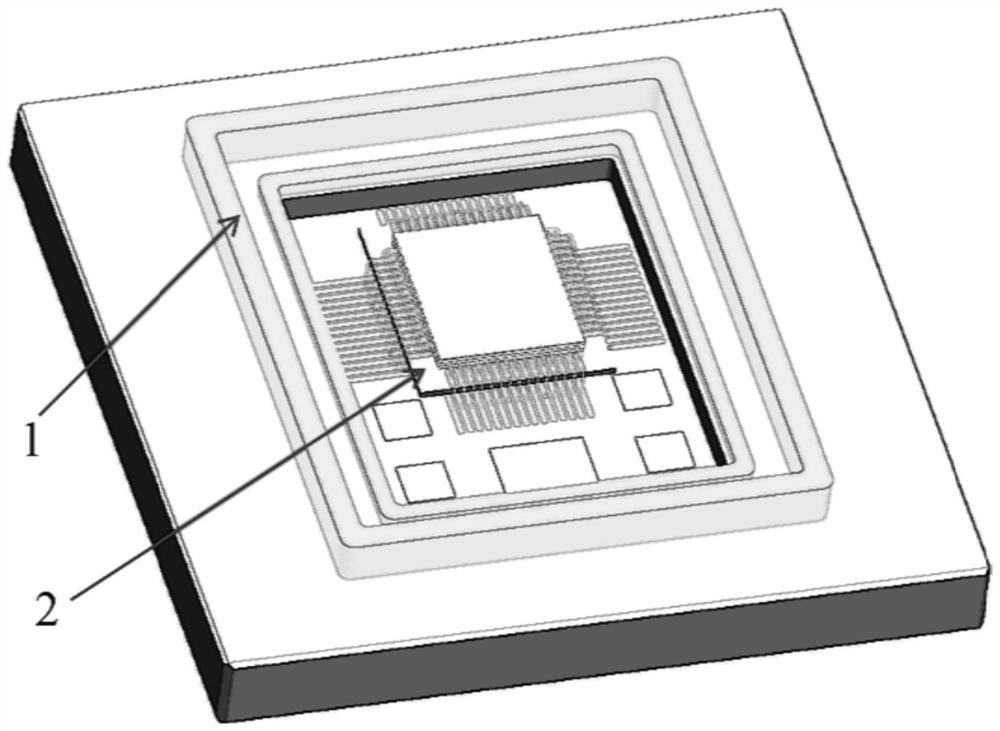

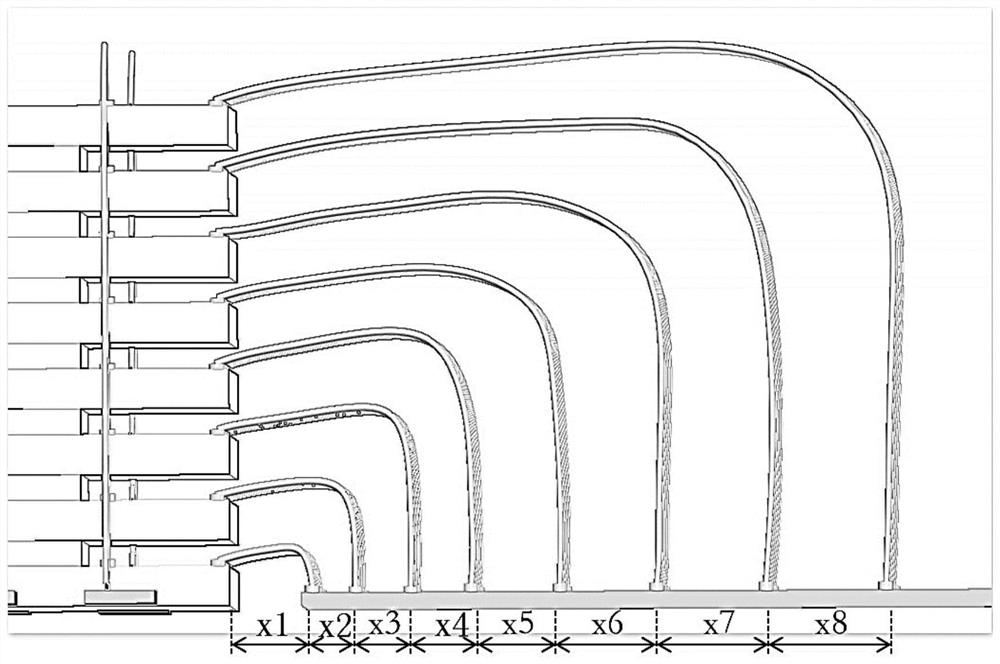

[0060] see figure 1 , figure 2 and Figure 4 , is the packaging structure of the multi-layer chip stack assembly of the present invention. In a specific embodiment, an eight-layer chip stack assembly 2 based on film substrate transfer is formed, wherein the cantilever sandwich type eight-layer chip stack assembly includes 8 super Thin chip, 7 silicon spacers and 1 thin film interposer substrate. The process steps of its preparation process are as follows:

[0061] (1) According to the drawings and materials, observe and determine the bonding area and bonding orientation of the chip 3 under a low-magnification microscope;

[0062] (2) Dip an appropriate amount of adhesive with a dispensing tungsten needle (stir the adhesive at least once every 1 hour, and stir for 2s to 3s each time), and apply it on the center of the chip bonding area. The adhesive should be Approximately coated into the shape of the effective bonding surface of the chip 3 to be bonded or an array of unif...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More